DS28E10 1-Wire SHA-1认证器技术手册

描述

概述

DS28E10在单一芯片内把一次性编程224位用户EPROM与符合FIPS 180-3安全散列算法(SHA-1)的质询-响应安全认证功能结合在一起。一旦写入数据,存储器将自动开启写保护。此外,每一个器件带有唯一的64位ROM注册码(ROM ID),由工厂刻入芯片。每次可向存储器写入4个字节,安全的低成本工厂编程服务可对器件数据进行预编程,这也包括SHA-1安全数据部分。器件通过单触点1-Wire®总线进行通信,遵循标准的1-Wire协议,ROM ID在多器件1-Wire网络中充当节点地址。

数据表:*附件:DS28E10 1-Wire SHA-1认证器技术手册.pdf

应用

- 授权管理的参考设计

- 传感器/配件识别和校准

- 系统知识产权保护

特性

- 专用的硬件加速SHA-1引擎产生SHA-1 MAC

- 一页28字节用户OTP EPROM

- 不可逆写保护

- 唯一的工厂编程64位识别码

- 1-Wire接口支持标准速率和高速驱动

- 以15.4kbps标准速率或高达125kbps的高速模式与主机通信

- 工作在2.8V至3.6V供电范围和-40°C至+85°C温度范围

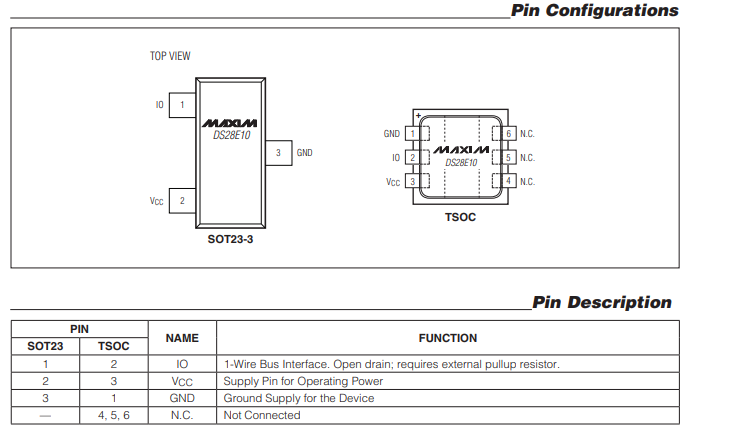

- 3引脚SOT23和6引脚TSOC封装

- 1-Wire和V

CC引脚具有±6kV (典型值)人体模式(HBM) ESD保护

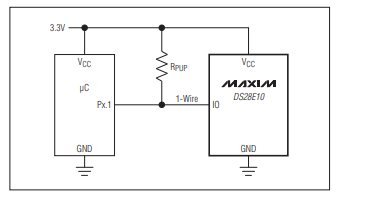

典型操作电路

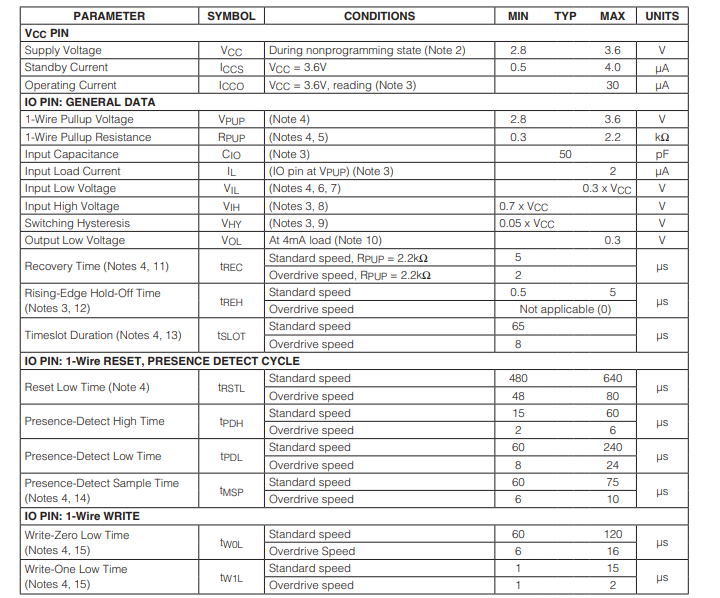

电特性

引脚配置描述

详细说明

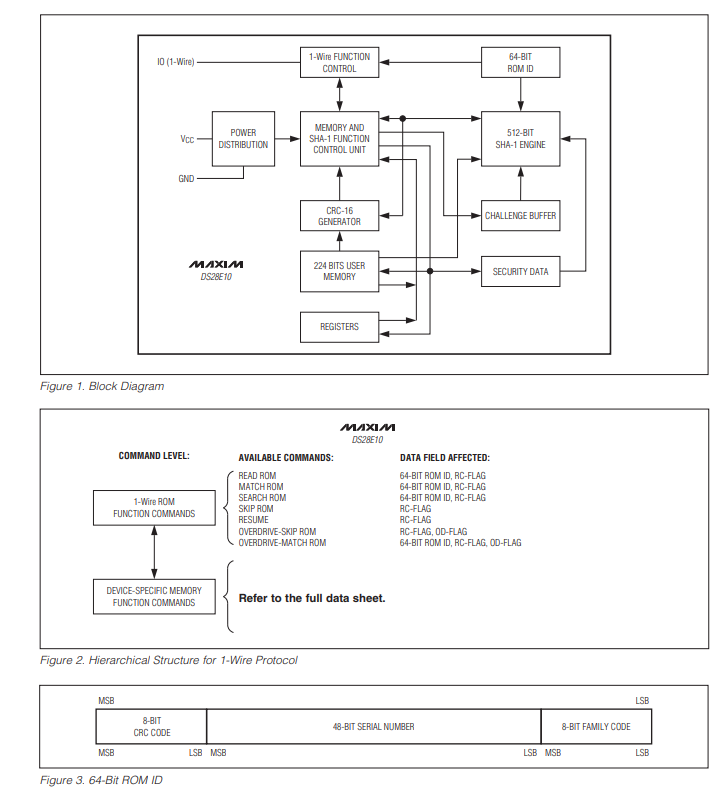

DS28E10将一个512位SHA - 1引擎、安全数据、224位一次性可编程(OTP)电可擦可编程只读存储器(EPROM)以及一个64位ROM ID集成在单个芯片中。数据通过一线协议进行串行传输,仅需一条数据线和地线即可返回。除了在加密SHA - 1计算中作为唯一数据值的重要作用外,设备的64位ROM ID可用于电子识别使用DS28E10的设备。ROM ID还可作为多设备一线网络环境中的节点地址,多个设备在同一一线总线上,并可独立运行。

概述

图1中的框图展示了DS28E10主要控制和存储部分之间的关系。该设备有六个主要数据组件:64位ROM ID、安全数据、主存储缓冲区、264字节用户EPROM存储器、特殊功能寄存器以及一个512位SHA - 1引擎。图2展示了一线协议的层次结构。总线主设备必须首先提供七个ROM功能命令之一:1)读ROM,2)匹配ROM,3)搜索ROM,4)跳过ROM,5)恢复(通信),6)超速跳过ROM或7)超速匹配ROM。在完成标准速度下执行的超速跳过ROM或超速匹配ROM命令后,设备将进入超速模式,此时所有后续通信都将以更高速度进行。这些ROM功能命令所需的协议在图8中说明。在成功执行ROM功能命令后,存储器和SHA - 1功能将变得可访问,主设备可以使用六个可用的功能命令中的任何一个。这些功能命令的协议在图6中说明。所有数据读写均先从最低有效位开始。

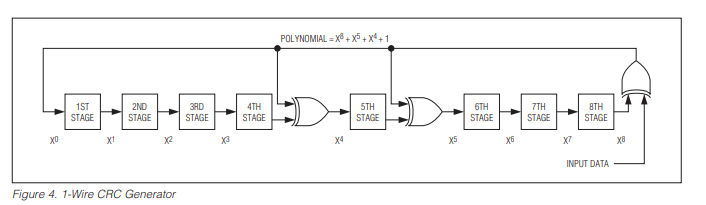

64位ROM ID

每个设备都包含一个唯一的64位ROM ID。前8位是一线家族码。接下来的48位是唯一的序列号。最后8位是对前56位的循环冗余校验(CRC)。详情见图3。一线CRC使用多项式生成器生成,该生成器由移位寄存器和异或门组成,如图4所示。多项式为(X^8 + X^5 + X^4 + 1) 。有关一线CRC的更多信息,请参阅美信应用笔记27:《使用循环冗余校验实现美信1 - 线和iButton产品中的数据验证》。

移位寄存器位初始化为0。然后,从家族码的最低有效位开始,逐位移入。在第8位家族码输入后,输入序列号。在输入序列号的最后一位后,移位寄存器包含CRC值。移位8位后,CRC将移位寄存器重置为全0。

存储器

该设备有三个存储区域:用户存储器、安全数据和特殊功能寄存器。用户存储器和特殊功能寄存器位于线性地址空间中,如图5所示。用户存储器从地址0000h开始,到地址0017h结束。有关详细信息和附加信息,请参阅完整的数据手册。

用户可写存储器采用EPROM技术实现。存储器的出厂默认状态为00h。在编程过程中,目标4字节块中的位可以更改为1或0。一旦一个块被写入,整个4字节块将自动被写保护。这意味着无法多次对一个块进行编程,例如一次更改几位。

一线信号

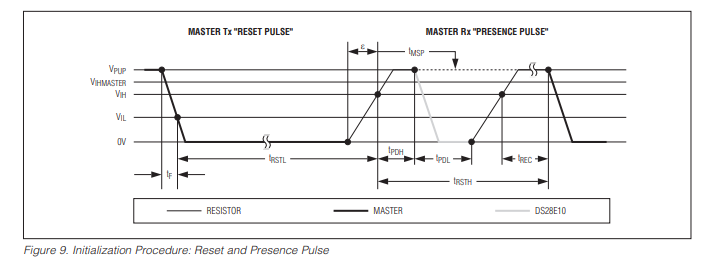

DS28E10需要严格的协议来确保数据完整性。该协议包含一线上的四种信号类型:复位脉冲与存在脉冲、写0、写1和读数据。除存在脉冲外,总线主设备可在所有下降沿发起信号。DS28E10可在两种速度下通信:标准速度和超速。如果未明确切换到超速模式,DS28E10将以标准速度通信。在超速模式下,快速定时适用于所有信号。

从空闲状态转为活动状态时,一线上的电压需从(V_{PU})降至阈值(V_{IL})以下。从活动状态转为空闲状态时,电压需从0V升至阈值(V_{IH})以上。达到此上升所需的时间取决于上拉电阻((R_{PUP}))和一线总线电容((C_{TOT})),其时间如图7所示,持续时间为(tau) 。

图9展示了与DS28E10开始任何通信所需的初始化序列。一个复位脉冲后接一个存在脉冲,表示DS28E10已准备好接收数据、给定的总线主设备ROM和功能命令。如果总线主设备使用慢速率控制(即下降沿),则必须将(t_{RSTL})下拉至(t_{RSTL} + t_{F}) ,以补偿边缘缓慢的情况。持续480μs或更长时间的(t_{RSTL}) ,可在标准速度下扩展超速模式,或返回设备的默认速度。如果DS28E10处于超速模式且(t_{RSTL}) 小于80μs ,则设备将保持在超速模式。如果设备处于超速模式,且(t_{RSTL}) 在80μs至480μs之间,设备将复位,但通信速度不受影响。

总线主设备释放线路后,线路进入接收模式。此时,一线总线通过上拉电阻(对于DS2482 - x00驱动器,则通过有源电路)上拉至(V_{PU}) 。当超过阈值(V_{IH})时,DS28E10将(t_{PDH}) 置为1 ,然后传输存在脉冲以拉低线路电平。为检测存在脉冲,总线主设备必须在(t_{MSP}) 测试一线的逻辑状态。

(t_{RSTH}) 窗口必须至少为(t_{PDHMAX}) 、(t_{IDLEMAX}) 和(t_{RECEMIN}) 之和。在(t_{RSTH}) 过期后,DS28E10准备好进行数据通信。在混合网络中,标准速度下(t_{RSTH}) 应延长至至少480μs ,超速速度下应延长至48μs ,以适应其他一线设备。

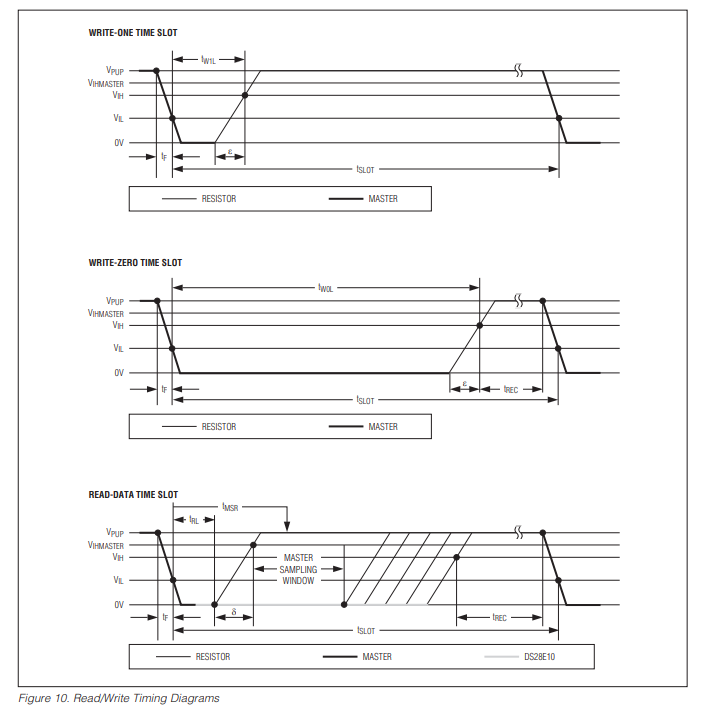

读/写字时隙

与DS28E10的数据通信在时隙中进行,每个时隙传输一位数据。写字时隙将数据从总线主设备传输到从设备。读时隙将数据从从设备传输到总线主设备。图10说明了写和读时隙的定义。

所有通信均由总线主设备拉低数据线开始。当一线总线电平降至阈值(V_{IL})以下时,DS28E10启动内部定时发生器,该发生器决定何时对数据线进行采样。

-

DS28E16 1-Wire Secure SHA-3 Authenticator:安全认证的理想之选2026-04-01 145

-

DS28E25内置1-Wire SHA-256和4Kb用户EEPROM的DeepCover安全认证方案2025-05-14 1048

-

DS28E16 1-Wire SHA-3安全认证器技术手册2025-05-13 1290

-

DS28E40: Deep Cover Automotive 1-Wire Authenticator Data Sheet DS28E40: Deep Cover Automotive 1-Wire Authenticator Data Sheet2023-10-17 65

-

DS28E25: DeepCover Secure Authenticator with 1-Wire SHA-256 and 4Kb User EEPROM Data Sheet DS28E25: DeepCover Secure Authenticator with 1-Wi2023-10-16 51

-

ADI推出DS28E30 1-Wire ECDSA安全认证器2022-05-27 2546

-

DS2465 SHA-256协处理器与1-Wire主机功能2012-06-12 7186

-

DS28E04-100 4096位,1-Wire EEPROM芯片2011-12-23 3576

-

DS28E10 1 - Wire协议2010-10-08 2945

-

为什么1-Wire SHA-1器件是安全的?2009-05-08 1383

全部0条评论

快来发表一下你的评论吧 !