芯片制造中的钨栓塞与铜互连

描述

文章来源:半导体与物理

原文作者:jjfly686

本文主要讲述芯片制造中钨栓塞与铜互连。

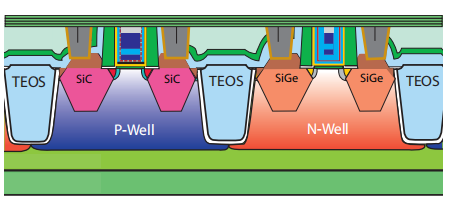

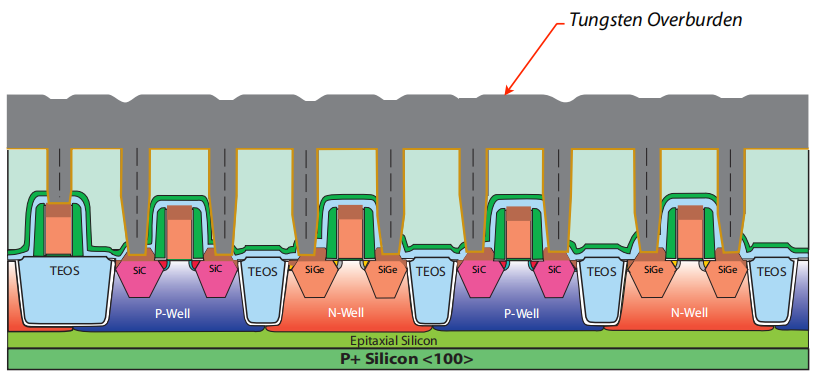

在指甲盖大小的芯片上,数十亿晶体管需要通过比头发丝细千倍的金属线连接。随着制程进入纳米级,一个看似微小的细节——连接晶体管与金属线的"接触孔",却成为影响芯片性能的关键战场。

纳米接触孔的电阻飙升

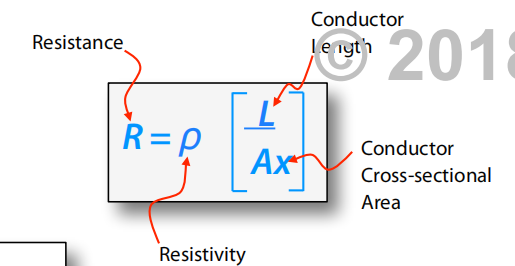

当芯片制程进入20 nm节点时,接触孔直径缩小到20 nm时,金属接触电阻会突然暴增3倍。这是因为接触电阻与导体截面积成反比,当直径从100 nm缩小到20 nm,截面积减少了25倍!

传统钨栓塞的困境:金属钨的电阻率比铜高,在纳米级接触孔中更显劣势;接触孔深度若保持500 nm,其电阻相当于在纳米尺度上"拖着一根细长的金属丝";在28 nm芯片中,接触电阻已占总互连电阻的40%,严重影响芯片速度与功耗。

钨栓塞的绝地反击:从"柱子"到"沟槽"

为了解决这一难题,工程师开发出两项关键技术:

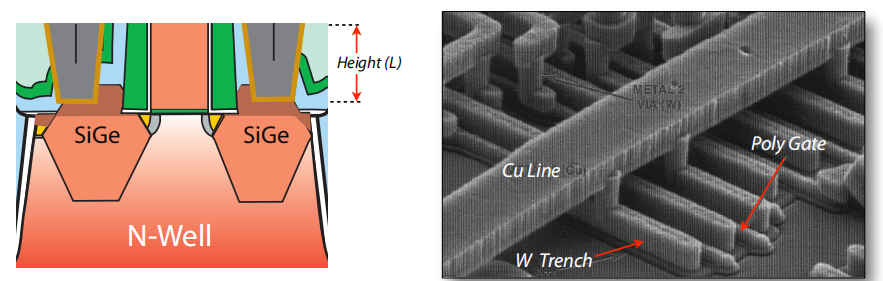

栓塞抛光(Plug Polish Back)在32 nm节点首次实现将钨栓塞抛光至与栅极平齐,将接触孔深度从500 nm压缩到100 nm。由于电阻与长度成正比,深度缩短使接触电阻降低80%。

钨沟槽(Tungsten Trenches)将垂直的栓塞改为横向沟槽,接触面积扩大5-10倍。

抬升源漏

与钨栓塞技术同步发展的,是抬升源漏(Raised Source/Drain)技术:通过外延生长在晶体管源漏区形成凸起的硅锗(SiGe)或硅碳(SiC)层;将接触孔深度从硅衬底内部转移到抬升层,避免损伤敏感的有源区;

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

一文详解铜互连工艺2025-06-16 3231

-

芯片制造中的阻挡层沉积技术介绍2025-05-03 2730

-

集成电路片内铜互连技术的发展2010-05-04 533

-

铜重量在PCB制造中的作用2020-10-20 2492

-

微球强度测定 栓塞刚性测定资料2022-01-18 717

-

铜互连,还能撑多久?2022-12-19 1622

-

提高铜互连优势的方法2023-02-17 2970

-

具有铜互连的IC芯片设计2023-08-18 2017

-

先进封装中硅通孔(TSV)铜互连电镀研究进展2023-09-06 2222

-

什么是铜互连?为什么铜互连非要用双大马士革工艺?2023-11-14 12285

-

铜互连,尚能饭否?2024-07-02 1183

-

铜对芯片制造中的重要作用2025-07-09 1382

-

激光焊接技术在焊接栓塞弹簧圈工艺中的应用2025-09-24 314

全部0条评论

快来发表一下你的评论吧 !