DS5003安全微处理器芯片技术手册

描述

概述

DS5003安全微处理器集成了最先进的加密功能,包括一套专门设计的安全机构,能够抵御各种级别的威胁,包括监测、分析和物理攻击。这样,想要获得任何有关存储器内容的信息,都需付出极大努力。而且, DS5003所特有的“柔性”特性使用户能够频繁修改安全信息,使攻击者经过大量努力获得的任何安全信息失去价值。该器件是DS5002FP安全微处理器芯片的增强版,具有额外的暂存区RAM。

数据表:*附件:DS5003安全微处理器芯片技术手册.pdf

特性

- 适合于安全/敏感应用的8051兼容微处理器

- 可访问32kB、64kB或128kB非易失SRAM的程序和/或数据存储器

- 128字节RAM

- 128字节间接暂存器RAM

- 通过片内串行接口在系统内编程

- 能够在最终系统中调节自身的程序或数据存储器

- 固件安全性

- 存储器以密文方式存储信息

- 加密算法采用片内64位密钥

- 自动操作的真随机密钥生成器

- 自毁输入(SDI)

- 顶部敷层防止微探针探测

- 防止存储内容被盗版

- 防冲击工作

- 没有电源的情况下可保护非易失资源达10年以上(室温下)

- 电源失效复位

- 电源失效早期告警中断

- 看门狗定时器

应用

- 需要软件保护的任何应用

- 游戏机

- 密码键盘

交流特性—程序

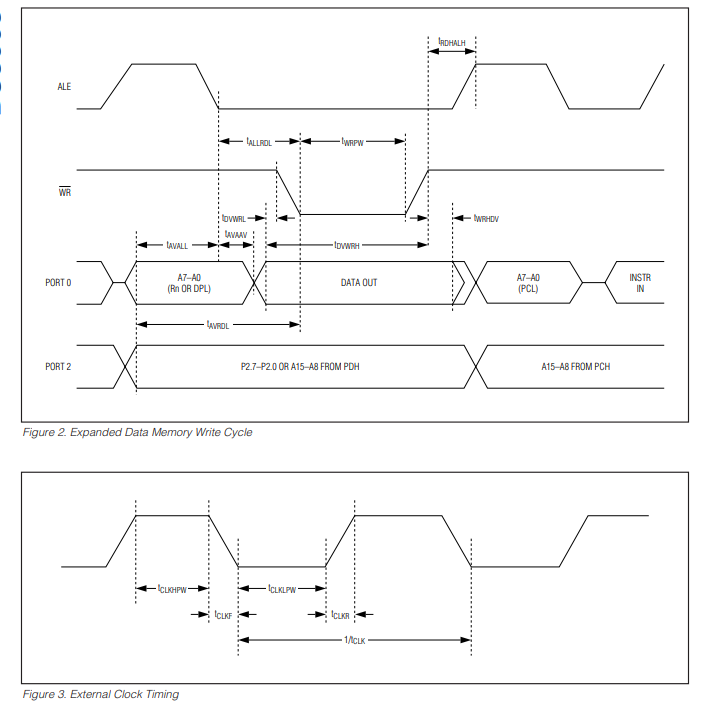

注1:所有电压均以地为参考。

注2:最大振荡频率fOSC是在所有输出引脚断开连接的情况下测量的;XTAL1由t CLKR 、tCLKF = 10ns驱动,VIL = 0.5V;XTAL2断开连接;RST = 端口0 = V CC ,MSEL = VSS 。

注3:空闲模式下,IIDLE是在所有输出引脚断开连接的情况下测量的;XTAL1由t CLKR 、tCLKF = 10ns驱动,VIL = 0.5V;XTAL2断开连接;端口0 = V CC ,RST = MSEL = VSS 。

注4:停止模式下,ISTOP是在所有输出引脚断开连接的情况下测量的;端口0 = V CC ;XTAL2未连接;RST = MSEL = VSS 。

注5:引脚电容是在VCC 下以1MHz、TA = +25°C的测试频率测量的。此规格已进行特性分析,但未进行量产测试。

注6:VCC02是在VIL 最大负载为10μA时的VCC 。

注7:ICC 是在正常工作模式下可从VCC0 汲取的平均最大工作电流。

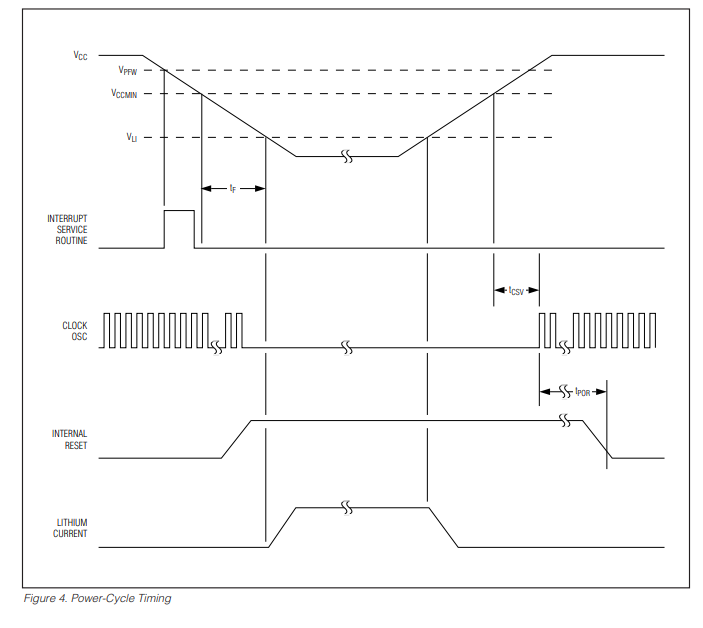

注8:Iμ 是当VCC = 0V且VCC0 断开连接时从VIL 汲取的电流。电池备份模式下,2.5V ≤ VBAT ≤ 4.0V,VSS ≤ V BAT ,VSDI 应为VIL 引脚,IBAT 最大。

注9:PF引脚工作在2.0V或VCC0 (以较低者为准),VBAT ≥ 3.0V 。

注10:VIH 最小值为2.0V或VCC0 (以较低者为准)。脉冲必须长于tPSR 才能通过去抖电路,但SDI未去抖,除非避免意外损坏。

注11:SDI在大于tPSA 之前不保证去抖。

注12:晶体启动时间是从电源施加到芯片开始,使晶体产生振动所需的时间。用户应向晶体供应商确认启动时间是否满足电路时钟脉冲要求。

-

探索DS5000FP软微处理器芯片:特性、应用与设计要点2026-04-01 286

-

探秘DS5002FP安全微处理器芯片:安全与性能的完美融合2026-03-24 150

-

DS1705/DS1706:3.3V和5.0V微处理器监控器的卓越之选2026-02-27 202

-

[3.10.1]--3.10微处理器概述学习电子知识 2023-02-17

-

DS5003FPM-16+ DS5003FPM-16+ - (Maxim Integrated) - 嵌入式 - 微控制器2022-11-16 221

-

基于AVR 8位微处理器的FSPLC微处理器SOC设计2019-07-26 2499

-

微处理器芯片的位数指的是什么2017-11-22 53946

-

MAX708微处理器电源监控芯片2017-01-08 1745

-

SPWM专用控制芯片及微处理器应用比较2016-04-13 960

-

使用DS1075 EconOscillator作8051微处理器的时钟2014-09-23 4109

-

基于SX微处理器的嵌入式Internet技术2011-12-15 669

-

微处理器的低功耗芯片设计技术详解2011-08-01 11423

-

DS5003中文资料,安全微处理器芯片2008-09-06 1345

全部0条评论

快来发表一下你的评论吧 !