ADIN1110可靠的工业低功耗10BASE-T1L 以太网 MAC-PHY技术手册

描述

概述

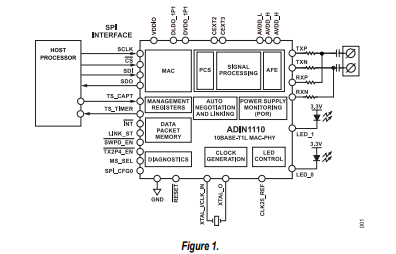

ADIN1110是一款面向工业以太网应用的超低功耗单端口10BASE-T1L收发器,符合IEEE^®^ 802.3cg-2019 ^™^ 以太网标准,支持长程10 Mb/s单对以太网(SPE)应用。ADIN1110具有集成的媒体访问控制(MAC)接口,可通过4线式串行外设接口(SPI)与各种主机控制器直接连接。该SPI可使用低功耗处理器,无需集成MAC,整体系统级功耗非常低。SPI可以配置为使用OPEN联盟SPI协议或通用SPI协议。

ADIN1110支持可编程发射电平、外部端接电阻和独立的接收和发送引脚,适合各种本质安全应用。

ADIN1110集成电压电源监控和上电复位(POR)电路,可提高系统级鲁棒性。

ADIN1110采用40引脚、6 mm × 6 mm引脚架构芯片级封装(LFCSP)。

数据表:*附件:ADIN1110可靠的工业低功耗10BASE-T1L 以太网 MAC-PHY技术手册.pdf

应用

- 现场仪器仪表

- 楼宇自动化和消防安全

- 工厂自动化

- 边缘传感器和执行器

- 状态监控和机器连接

特性 - 符合10BASE-T1L IEEE 802.3cg-2019标准要求

- 电缆延伸范围高达1700 m,支持1.0 V/2.4 V

- 集成SPI的MAC

- 支持OPEN Alliance 10BASE-T1x MAC-PHY串行接口

- 16个MAC地址过滤器

- 带28 kB缓冲器的高低优先级队列

- 直通或存储转发操作

- 支持IEEE 1588时间戳

- 统计计数器

- 低功耗:42 mW(双电源,1.0 V p-p)

- 诊断

- 具有TDR的电缆故障检测

- 具有MSE的链路质量指示器

- 帧生成器和检查器

- 多种环回模式

- IEEE测试模式支持

- 支持1.0 V p-p和2.4 V p-p发送电平

- 4针MDI(RXN、RXP、TXN和TXP)

- 适合本质安全应用

- 外部端接电阻

- 自动协商

- 25 MHz晶振或外部时钟输入

- 电磁兼容性(EMC)测试标准

- IEC 61000-4-4电快速瞬变(±4 kV)

- IEC 61000-4-2 ESD(±4 kV接触放电)

- IEC 61000-4-2 ESD(±8 kV空气放电)

- IEC 61000-4-6传导抗扰度(10 V/m)

- IEC 61000-4-5浪涌(±4 kV)

- IEC 61000-4-3辐射抗扰度(A类)

- EN55032辐射发射(B类)

- 小型封装:40引脚(6 mm × 6 mm) LFCSP封装

- 温度范围

- 工业:−40°C至+85°C

- 扩展范围:−40°C至+105°C

框图

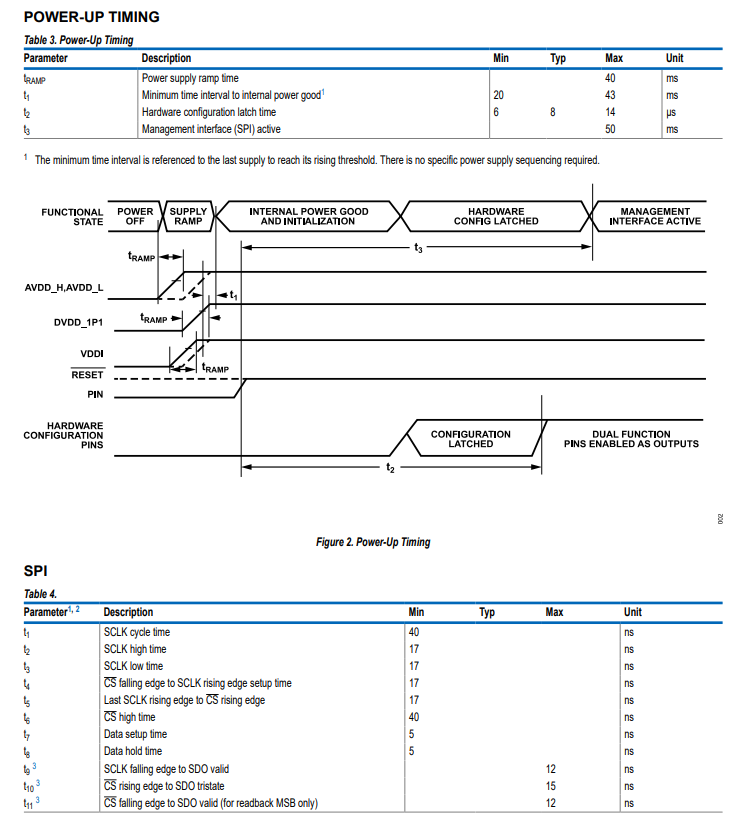

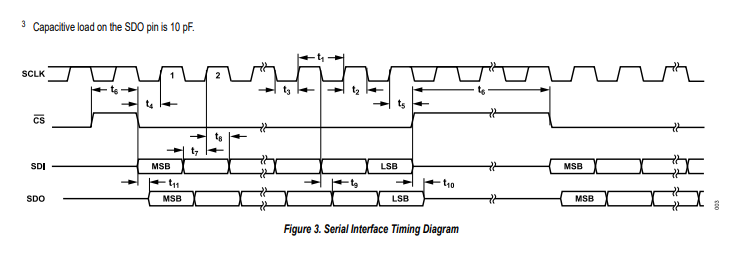

时序特征

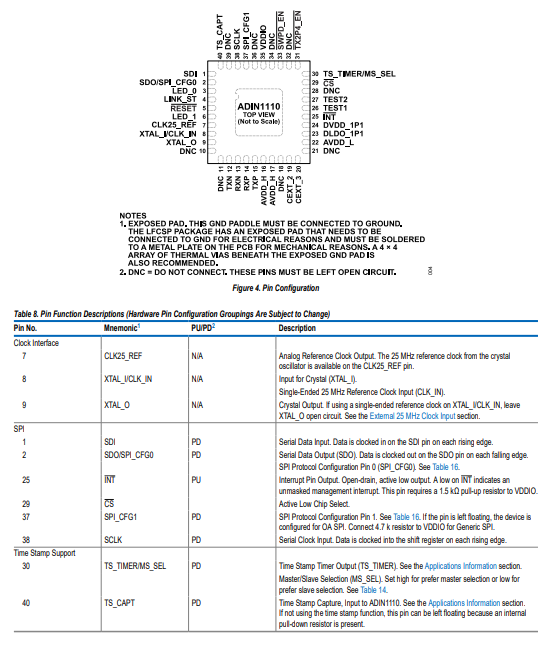

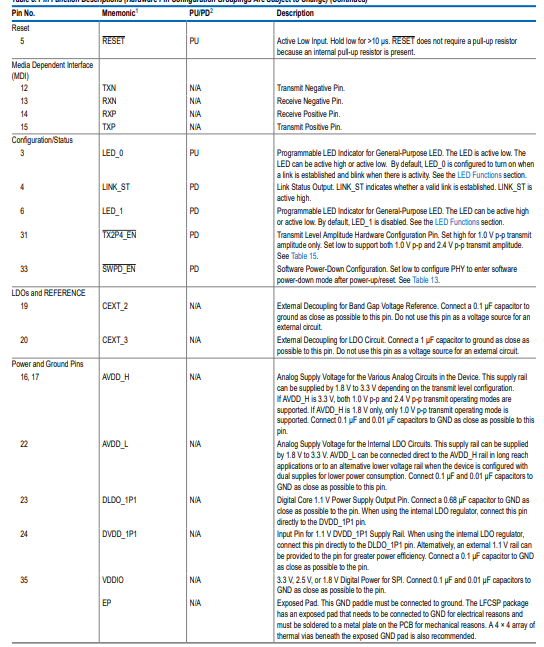

引脚配置描述

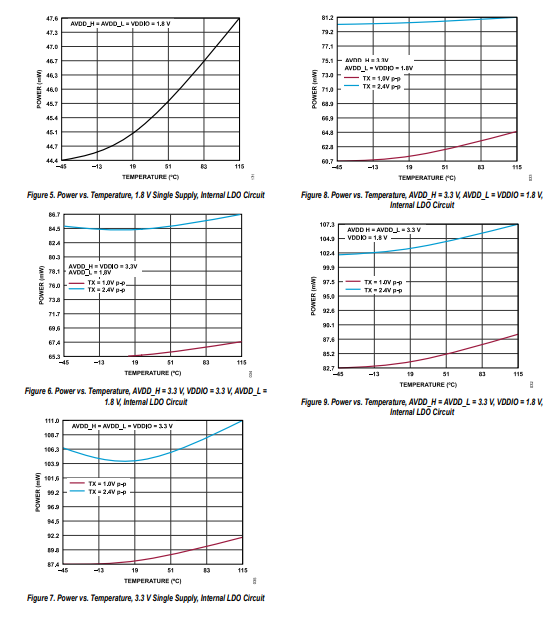

典型性能特征

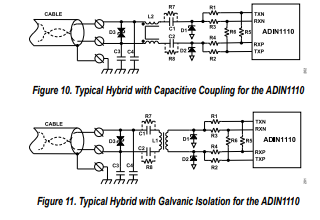

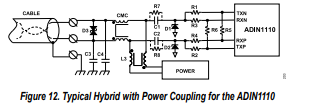

工作原理

- D1、D2:低电容(<5pF)、低电压(击穿电压≥3.3V)的瞬态电压抑制器(TVS)保护元件。

- C1、C2:0.22μF、60V电容。若变压器电感为350μH,则C1和C2可能需增至0.47μF(以符合IEEE 802.3的压降规格)。

- R7、R8:可选电阻,防止电容C1和C2上出现充电。阻值范围为100kΩ至1MΩ 。

- C3、C4:47pF ± 100pF、±5%容差电容。

- D3:低电容(≤100pF)的TVS保护元件。TVS具有低电容至关重要,因为变压器会产生漏电感。

- L1:变压器漏感。必须能在100kHz至20MHz频率范围内工作,电感值>350μH 。

- L2:共模电感,≥220μH,低漏电感<0.5μH 。

- L3:功率电感,用于高级物理层(APL)器件和非APL器件的电源耦合。APL:差分电感值为880μH,压降为10% 。推荐使用>220μH的耦合电感(两个电感在同一磁芯上),或两个>440μH的独立电感。非APL:差分电感值为160μH,最大压降约为25% 。推荐使用>47μH的耦合电感(两个电感在同一磁芯上),或两个>100μH的独立电感。

注:若在MDI传输线上存在隔离变压器,变压器电感与功率电感的总差分电感的并联组合必须大于160μH 。

复位操作

ADN1110支持以下芯片复位方式:

- 上电复位

- 硬件复位

- 软件复位

- MAC子系统复位

- PHY子系统复位

所有这些复位操作会使ADN1110(包括PHY内核和MAC)进入已知状态。只要MAC复位,SDO引脚就会被拉低,TS_TIMER引脚就会被驱动为低电平状态。

上电复位

ADN1110内置电源监测电路,用于监测所有电源。上电期间,ADN1110处于硬件复位状态,直到每个电源都超过其最小上升阈值电压且电源状态良好。

POR模块通过监测电源实现欠压保护。若一个或多个电源降至最小检测阈值以下,发生欠压检测时,器件将保持硬件复位状态,直到电源恢复正常。

硬件复位

硬件复位可由上电复位电路触发,或通过将RESET引脚拉低来实现。该引脚需至少保持低电平10μs 。此引脚上集成了0.3μs的去抖电路,以滤除短脉冲。

当RESET引脚解除置位时,所有输入/输出(I/O)引脚保持高阻态,硬件配置引脚被锁存,I/O模式根据其功能模式进行配置。当所有外部和内部电源均有效且稳定,晶体振荡器电路启用,晶体启动并稳定,锁相环(PLL)启用后,大约50ms(最长)后,RESET引脚的去置位信号生效,内部时钟有效,内部逻辑从复位状态释放,所有管理接口寄存器均可访问,从而可对器件进行编程。

软件复位

通过向芯片复位软件复位寄存器写入1来启动全芯片软件复位。

-

Analog Devices Inc. ADIN1110低功耗10BASE-T1L以太网MAC-PHY数据手册2025-07-02 2155

-

ADIN2111集成10BASE-T1L PHY的低复杂度、2端口以太网交换机技术手册2025-05-15 2980

-

ADIN1110 adi2025-03-11 187

-

DP83TD510E超低功耗802.3cg 10base-T1L 10M单线对以太网PHY数据表2024-06-19 513

-

单对以太网:如何实现 10Base-T1L2023-12-06 1577

-

ADIN2111:低复杂度,2-端以太太网开关,内装10BASE-T1L物理物理物理数据表 ADI2023-10-10 155

-

ADIN1110:强力、工业、低功率10BASE-T1LEthernet MAC-PHY数据表 ADIN1110:强力、工业、低功率10BASE-T1LEthernet MAC-PHY数据表2023-10-07 139

-

单对以太网:如何实现10Base-T1L2023-08-16 2232

-

10BASE-T1L使智能现场仪表供电变得无痛2023-06-27 1792

-

10BASE-T1L MAC-PHY如何简化低功耗处理器以太网连接2022-12-12 5351

-

ADIN1110:坚固、工业、低功耗10BASE-T1L以太网MAC-PHY初步数据表2021-03-22 1108

-

ADIN1100: Robust, Industrial, Low Power 10BASE-T1L Ethernet PHY Preliminary Data Sheet2021-01-29 950

全部0条评论

快来发表一下你的评论吧 !