离子研磨在芯片失效分析中的应用

描述

芯片失效分析中对芯片的截面进行观察,需要对样品进行截面研磨达到要观察的位置,而后再采用光学显微镜(OM Optical Microscopy)或者扫描电子显微(SEM Scanning Electron Microscopy)进行形貌观察。

传统机械研磨的时候,往往会造成金属延展、颗粒物填充等人为损害情况,对后续的检查带来不利影响。有些失效现象比如开裂,空洞等,传统的机械研磨制样会破坏原有的失效现象,分析这种失效现象的时候需要使用离子研磨的方式来制备样品。离子研磨是用聚焦离子束对样品进行切削,这个时候不会引入任何研磨的剪切力,不会破坏原有的失效现象,不会引入人为缺陷。

离子研磨技术相比传统研磨方法优势:

| 特性 | 离子研磨 | 机械研磨 |

| 加工原理 | 物理溅射(非接触式) | 机械摩擦(接触式) |

| 损伤风险 | 低(可控热损伤) | 高(应力/裂纹) |

| 加工精度 | 纳米级(粗糙度 <1 nm) | 微米级(受工具限制) |

| 适用材料 | 广(金属、陶瓷、聚合物等) | 延展性材料(金属、塑料) |

离子研磨的原理介绍

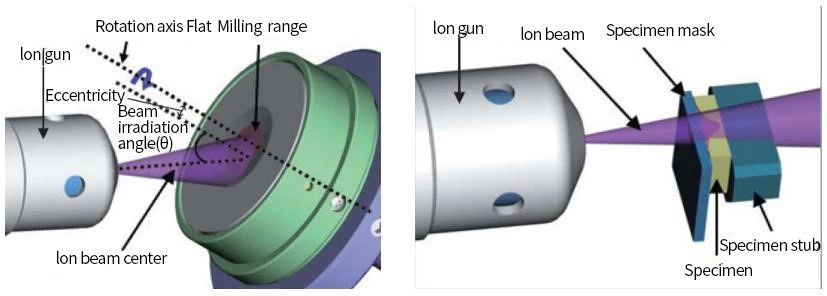

离子研磨(CP Cross-section Polisher)又叫离子抛光,氩离子研磨法。真空环境下,离子枪中低压气体离子化,出射的阳离子又经电场加速,利用通过电场加速过的离子轰击样品表面,在样品表面产生溅射效应,由此制备尺度为毫米级别的平滑表面的研磨方法。氩气属于惰性气体,基本不会和样品发生化学反应,因此通常我们采用氩气作为离子源轰击样品。

由于离子质量比电子大数千、数万倍,所以离子束比电子束具有更大的撞击动能,靠微观的撞击能量加工样品。并且不会对样品造成机械损害,获得表面平滑的高质量样品。可以实现Flat milling 平面研磨和Cross-section截面研磨这两种形式。

离子研磨的方法介绍

离子研磨制备芯片样品一般有以下具体步骤:

机械预处理

1切割芯片

使用金刚石锯等工具,将芯片从晶圆或封装体上切割下来,切割时要注意尽量减小对芯片的损伤,控制切割的尺寸和形状,以便后续操作。

2粗磨减薄

利用砂纸对切割后的芯片进行粗磨,去除大部分多余的材料,使芯片厚度初步降低。可从较粗粒度的砂纸开始,逐渐过渡到较细粒度的砂纸,以获得相对平整的表面。

3精细抛光

采用金刚石抛光膏等进行精细抛光,进一步减小表面粗糙度,为后续离子研磨提供更好的基础。不过要避免过度抛光产生表面应力和形变。

截面离子研磨

1切割样品

若需要观察芯片内部的截面结构,如多层膜、器件结构等,可先使用切割工具将芯片样品沿特定方向切割开,暴露出需要观察的截面。

2垂直轰击

将切割后的样品重新安装在样品台上,使离子束垂直于样品截面,设置加速电压为 2-5kV,选择合适的研磨时间,一般 60 分钟以上,进行离子研磨,以获得平整、无损伤的截面。

样品检查

1SEM 观察

使用扫描电子显微镜(SEM)对离子研磨后的芯片样品进行观察,检查样品表面或截面的显微结构。

2评估指标

重点观察表面平整度,查看是否存在残留的机械损伤、划痕、凹坑等缺陷,同时检查样品的显微结构是否完整,有无因离子研磨过度或不足而导致的结构变形、破坏等情况。若发现问题,可根据情况决定是否需要进一步研磨或采取其他处理措施。

离子研磨的案例

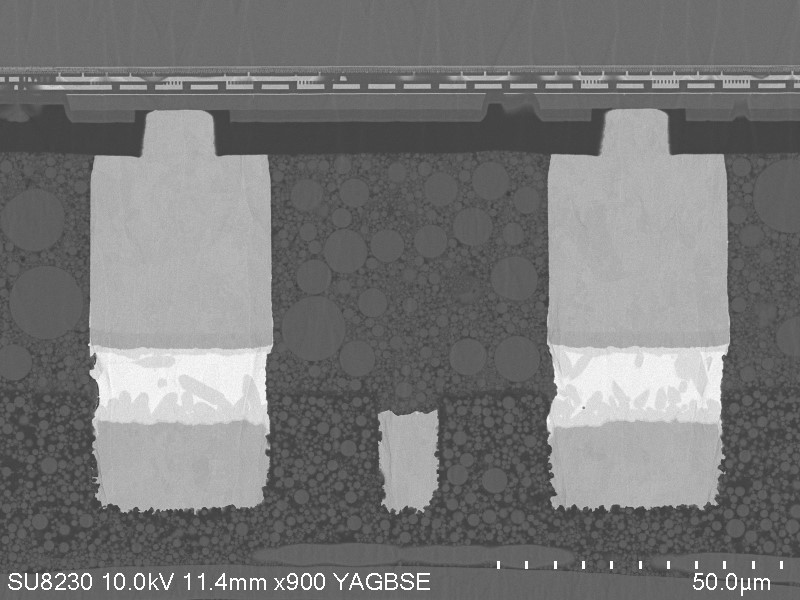

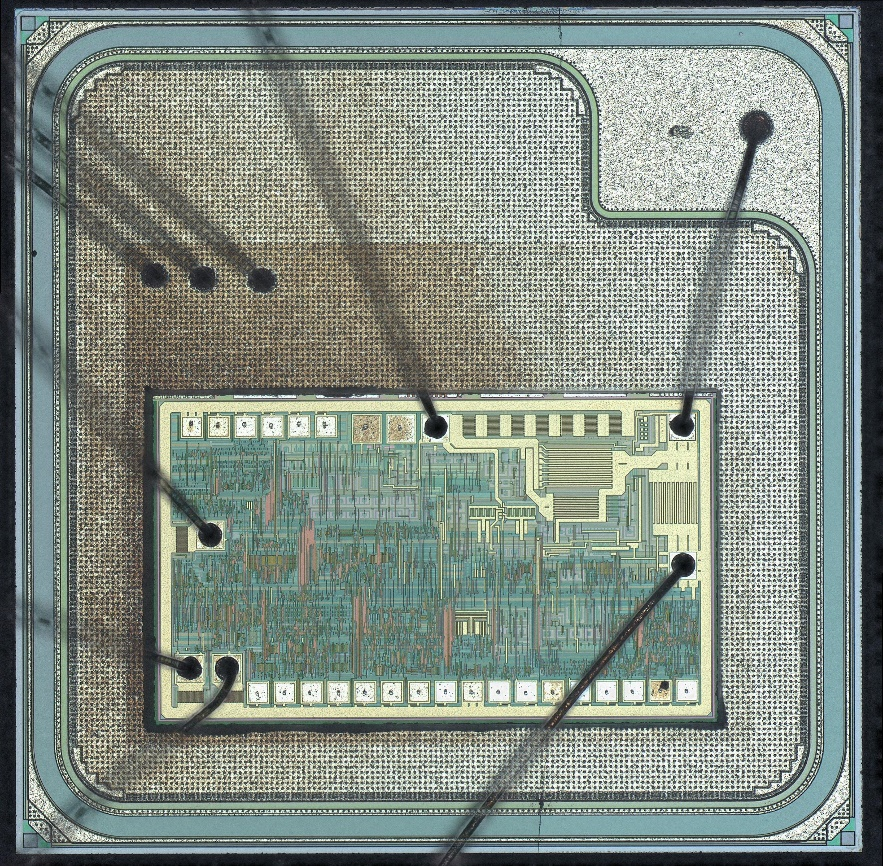

BGA封装(Low K材料,finfet工艺):传统研磨应力过大,FIB加工位置较小无法满足要求。

1Low K材料由于其松软的特性

容易在加工过程中产生裂纹。(物理研磨对这类样品容易造成开裂及分层,FIB加工为更好的方式。)

2 BGA封装厚度及宽度加工难度大。

离子束截面宽范围研磨最大工作范围可达8mm ,加工后的截面样品可以观察更多信息。(对封装类样品和观察范围大的样品比较适用。)

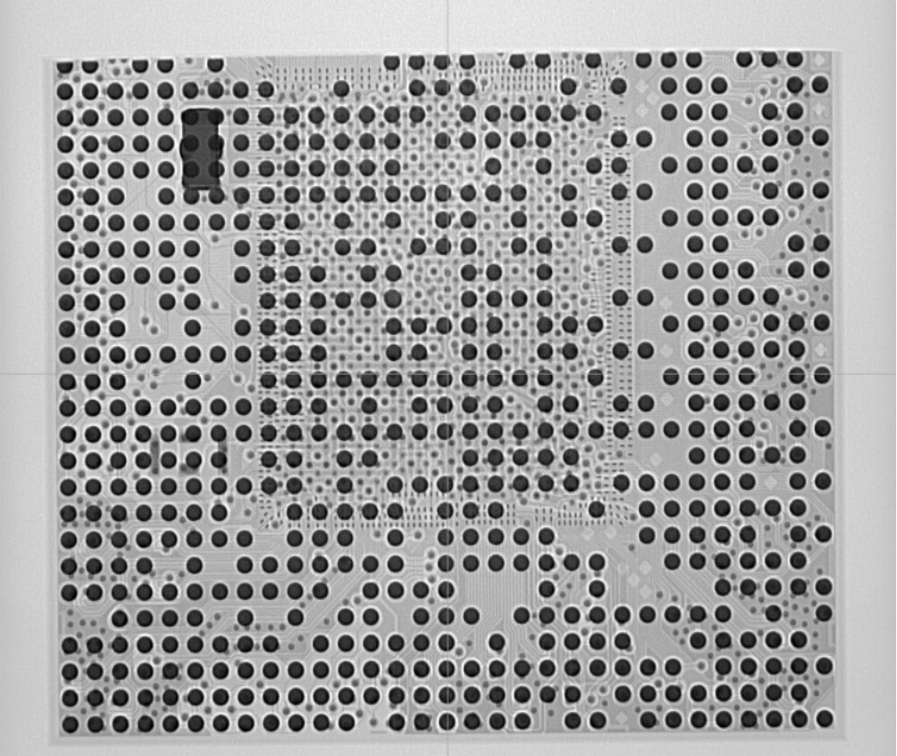

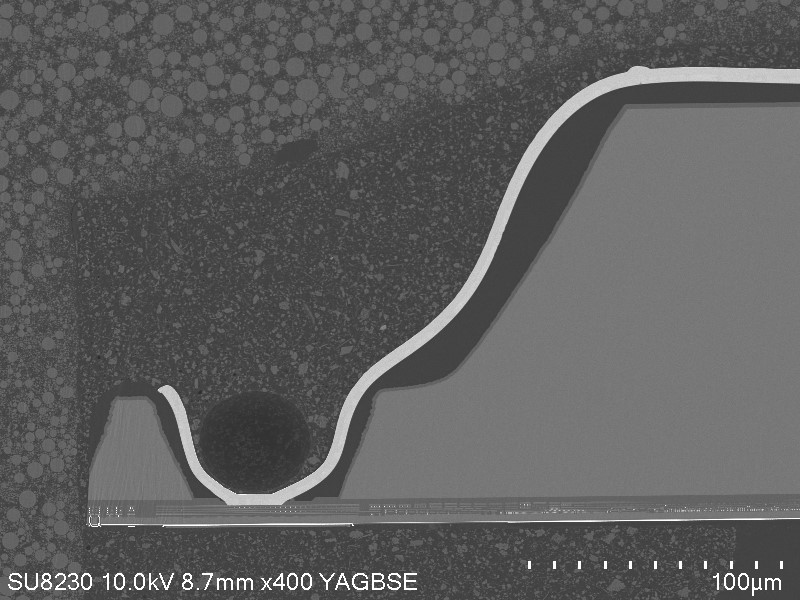

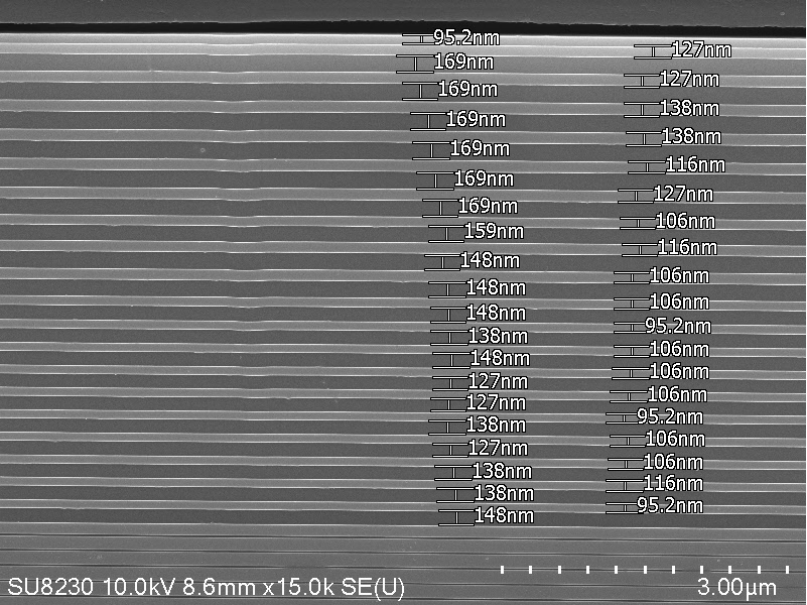

▼观察第一排Bump

▼离子束加工宽度≈8mm

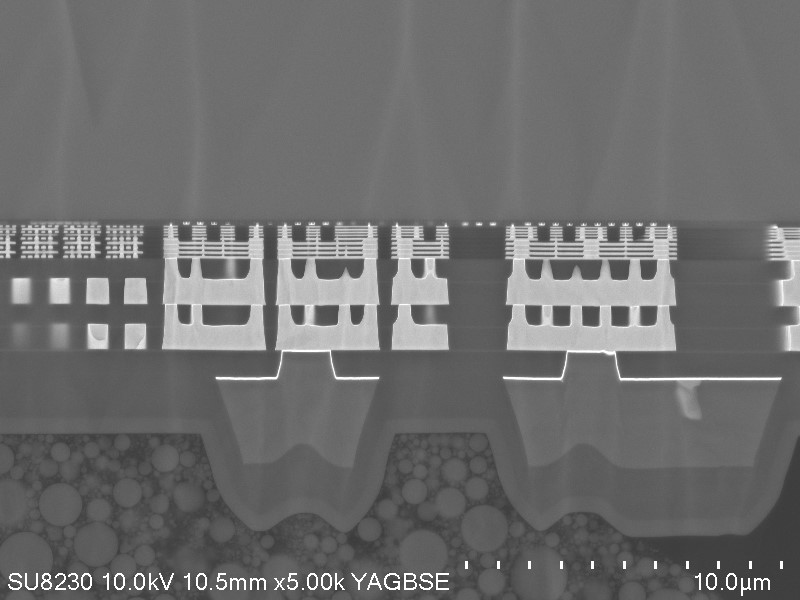

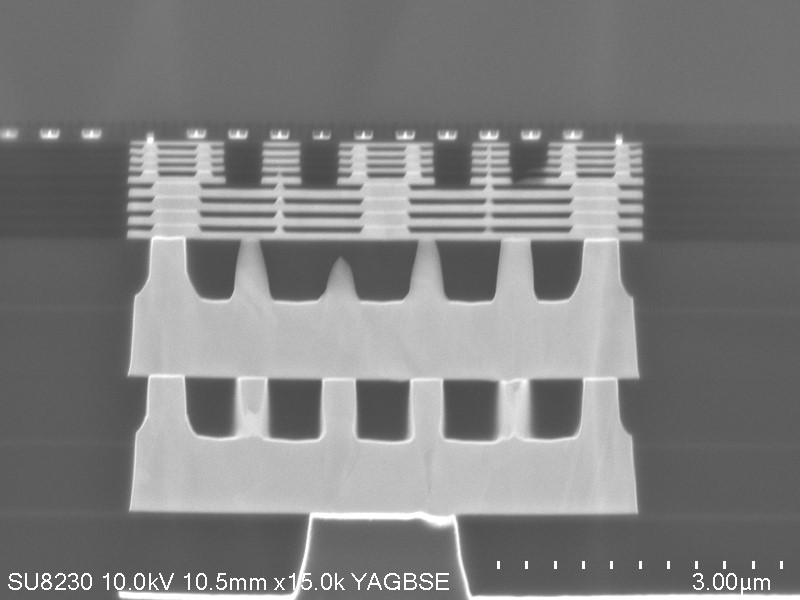

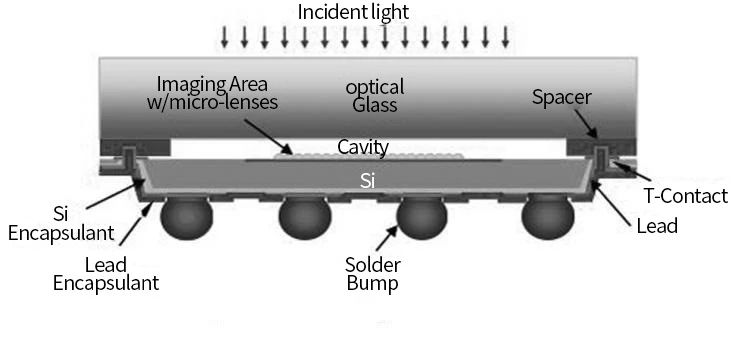

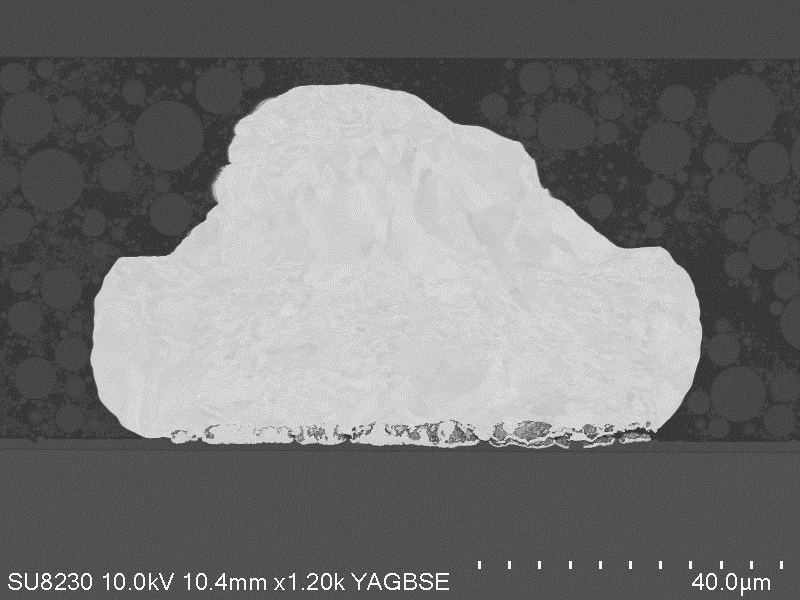

BSI(Backside Illumination)芯片样品:

BSI模组(如图1)表面覆盖一层玻璃厚度较厚无法进行FIB,物理去玻璃可能对芯片造成损伤。

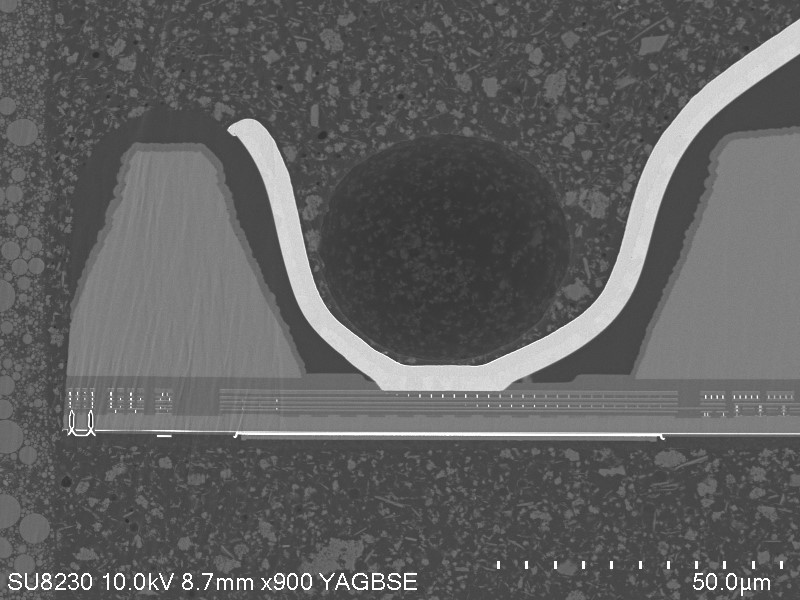

此类样品TSV较大且存在空洞(如图3),物理研磨应力影响很大,会影响对异常的判断。

采用离子束研磨可以有效的避免该问题。

▲图1

▲图2

▲图3

结构分析:

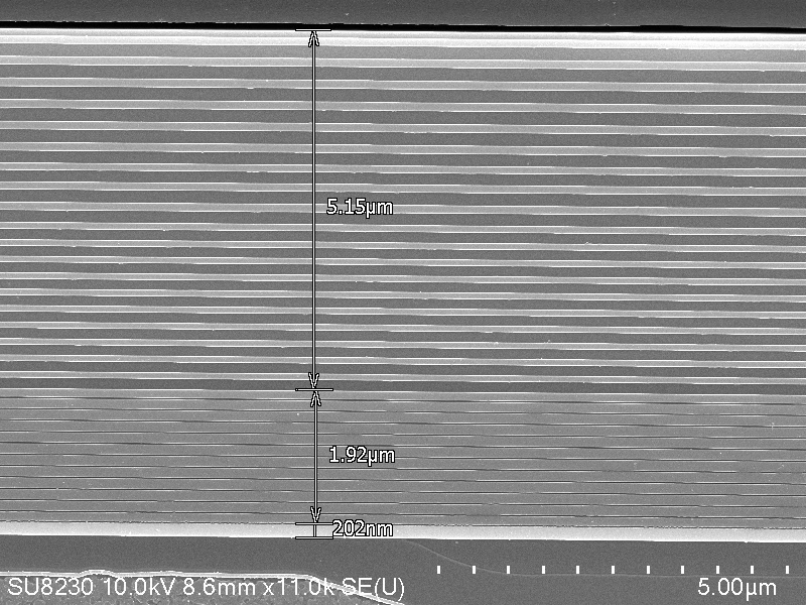

能制备出高质量的芯片截面样品,让研究人员清晰观察到芯片的各层次的结构,查看是否存在缺陷。

光感器件分析难点:

1.样品结构层次多(多达几十层)。

2.晶粒无法从封装中取出(化学试剂与有机膜层发生反应无法保留)。

3.截面加工完成后需要进行DIP后才能显现各层结构界限。

物理研磨和FIB对该样品加工都会存在局限性,用离子研磨可以避免物理研磨的影响,也可以兼顾FIB加工范围不够大的局限性。

分析封装相关问题

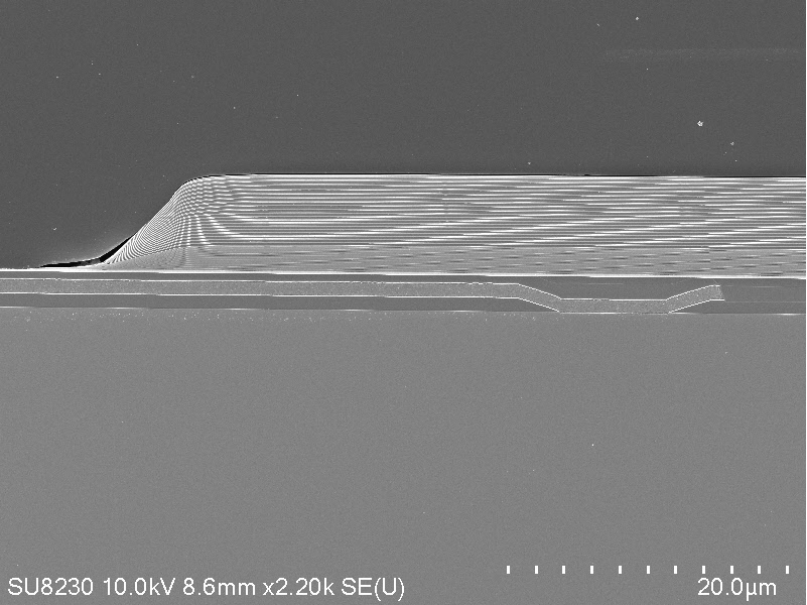

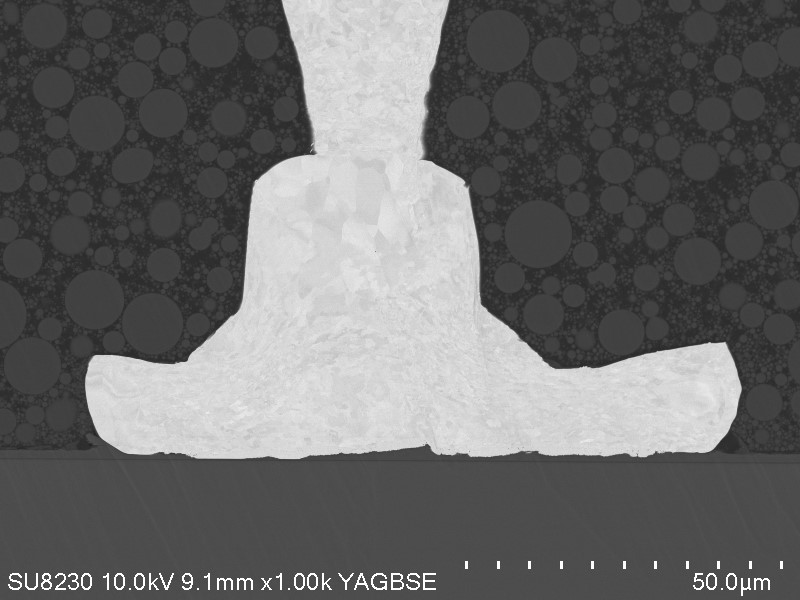

键合点检测:

在芯片封装中,键合点的质量至关重要。离子研磨可以精确地对键合点进行剖面分析,观察键合线与芯片引脚、基板之间的连接情况,判断是否存在键合不牢、键合线断裂、键合处氧化等导致信号传输不良的问题

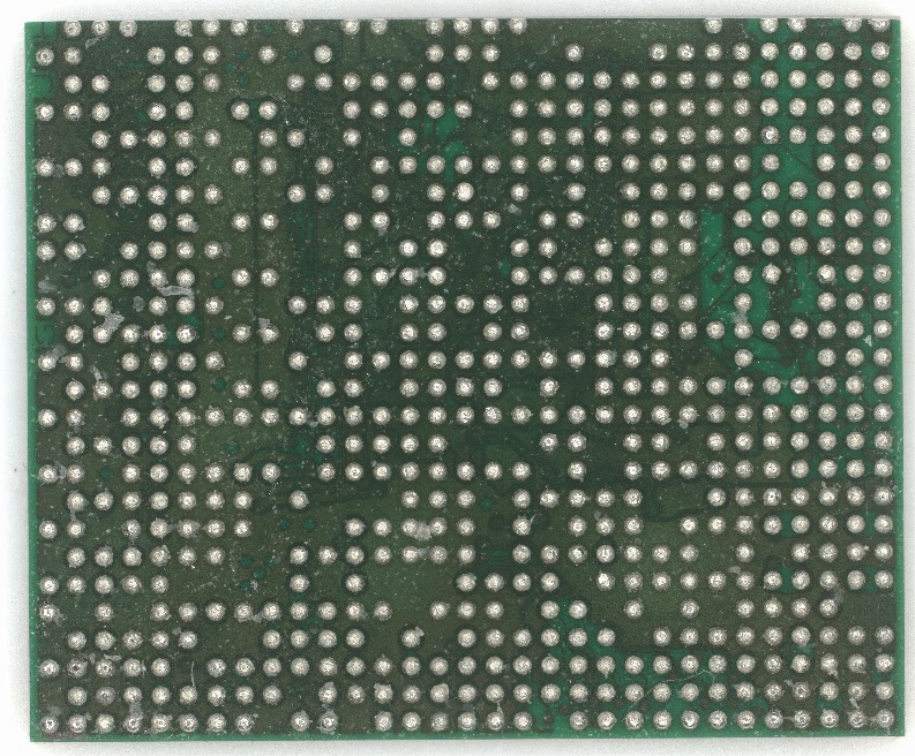

▲图4

▲图5

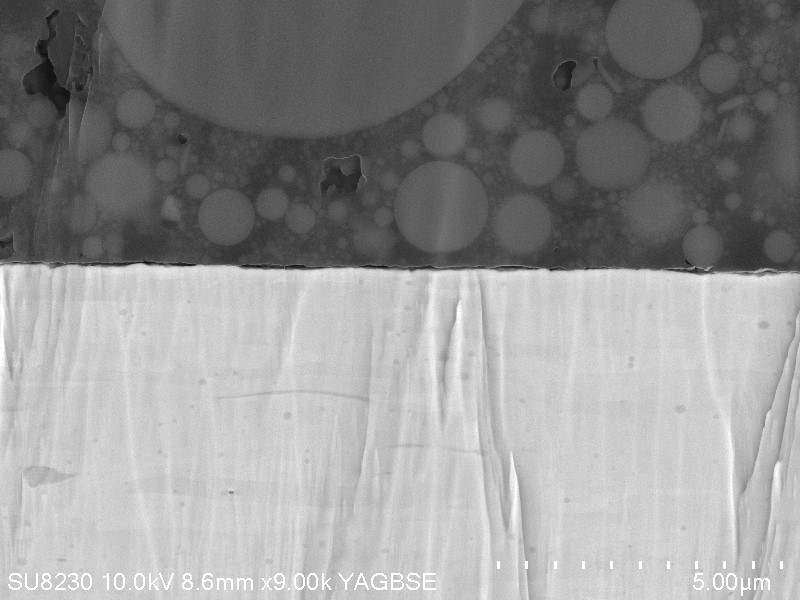

图4.图5为研磨后对样品进行截面离子抛光(通过离子抛光可以去除研磨引入的金属延展,可以更直观的观察产品缺陷及异常)

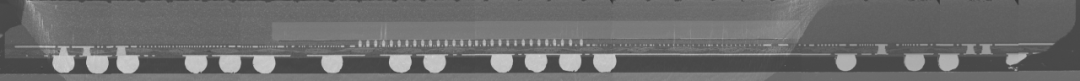

封装材料与芯片界面分析

通过离子研磨,可观察封装材料与芯片之间的界面结合状况,检测是否存在分层、气泡、裂缝等缺陷。这些缺陷可能会导致芯片在使用过程中受到外界环境影响,如湿气入侵,进而引发芯片失效。

▲DECAP后

▲DECAP后

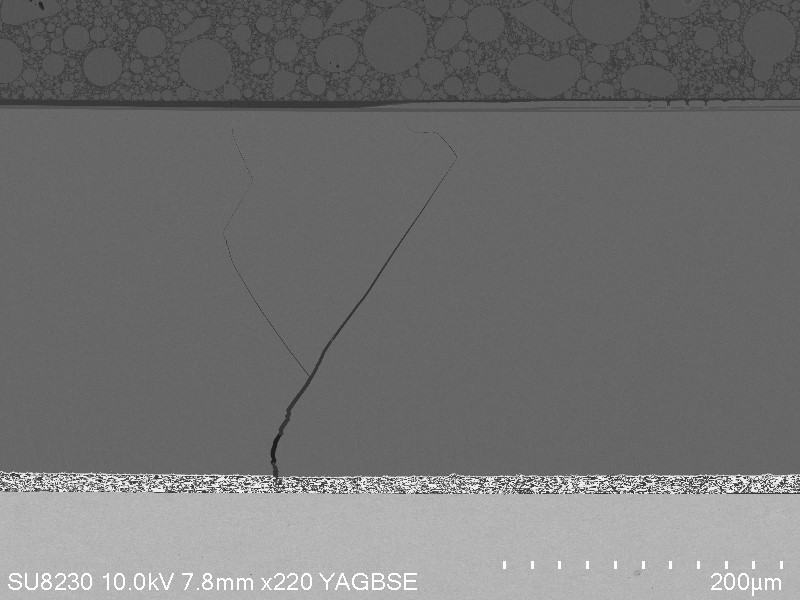

该案例在电性现象为短路(芯片开裂后引起金属错位),经PFA分析后怀疑在蓝膜取晶粒过程中顶针顶裂。

离子研磨在半导体分析中扮演着重要角色,与聚焦离子束(FIB)、扫描电镜(SEM)联用,实现加工与观测同步,推动原位分析技术发展。

●广适性较强可以处理金属、半导体、陶瓷、聚合物等多种材料。

●也可用于表面清洁与抛光:去除氧化层、污染物或机械加工残留,提升表面质量(如半导体晶圆、光学元件)。

季丰电子

季丰电子成立于2008年,是一家聚焦半导体领域,深耕集成电路检测相关的软硬件研发及技术服务的赋能型平台科技公司。公司业务分为四大板块,分别为基础实验室、软硬件开发、测试封装和仪器设备,可为芯片设计、晶圆制造、封装测试、材料装备等半导体产业链和新能源领域公司提供一站式的检测分析解决方案。

季丰电子通过国家级专精特新“小巨人”、国家高新技术企业、上海市“科技小巨人”、上海市企业技术中心、研发机构、公共服务平台等企业资质认定,通过了ISO9001、 ISO/IEC17025、CMA、CNAS、IATF16949、ISO/IEC27001、ISO14001、ISO45001、ANSI/ESD S20.20等认证。公司员工超1000人,总部位于上海,在浙江、北京、深圳、成都等地设有子公司。

-

聚焦离子束(FIB)技术在芯片失效分析中的应用详解2025-12-04 382

-

什么是锂离子电池失效?锂离子电池失效如何有效分析检测?2024-01-10 1825

-

芯片失效分析方法 芯片失效原因分析2023-08-29 6434

-

技术干货 | 失效分析:制样技术介绍(一):离子研磨(CP)2023-01-10 4116

-

LED芯片失效分析2020-10-22 3246

-

芯片失效分析步骤2020-05-18 5319

-

半导体失效分析方法总结2020-05-15 4251

-

芯片失效如何进行分析2020-04-24 4440

-

芯片失效分析含义,失效分析方法2020-04-07 7235

-

失效分析方法累积2020-03-28 2628

-

芯片失效分析方法及分析内容2020-02-13 2983

-

失效分析:离子束剖面研磨2018-08-28 3404

-

怎样进行芯片失效分析?2011-11-29 5130

全部0条评论

快来发表一下你的评论吧 !