ADGM1001/ADGM1002/ADGM1003 0 Hz/DC至34 GHz SPDT MEMS开关技术手册

描述

概述

ADGM1001/[ADGM1002]/[ADGM1003]是一款宽带、单刀双掷(SP2T)开关,采用ADI公司的微型机电系统(MEMS)开关技术制造而成。利用该技术可实现小型、宽RF带宽、高线性、低插入损耗开关,其工作频率可低至0 Hz/DC,可满足各种RF和精密设备开关需求。该器件采用24引脚5.00 mm × 4.00 mm × 0.90 mm基板栅格阵列(LGA)封装。

集成式控制芯片可产生静电驱动该开关所需的高压,通过互补金属氧化物半导体(CMOS)/低压晶体管对晶体管逻辑(LVTTL)兼容型并行接口进行控制。所有开关都可单独进行控制。

多功能引脚名称只能通过相关功能来引用。

数据表:*附件:ADGM1001 ADGM1002 ADGM1003 0 Hz DC至34 GHz SPDT MEMS开关技术手册.pdf

特性

- ADGM1001: 直流至 34 GHz

- 插入损耗

- 18 GHz 时为 0.8 dB(典型值)

- 34 GHz 时为 1.5 dB(典型值)

- IIP3:76 dBm(典型值)

- 最大射频功率:33 dBm

- 导通电阻:3.4 Ω(典型值)

- 最大直流电流:200 mA

- 驱动寿命:1亿次循环(最少)

- 开关时间

ON):200 μ小号(典型) - 集成 3.3 V 驱动器,可通过并行和 SPI 进行简单控制

- 可独立控制的开关

- 节省空间的集成无源元件

- 小,5.00 毫米× 4.00 mm× 0.90 毫米、24 引脚 LGA

- 温度范围:–40°C 至 +85°C

框图

时序图

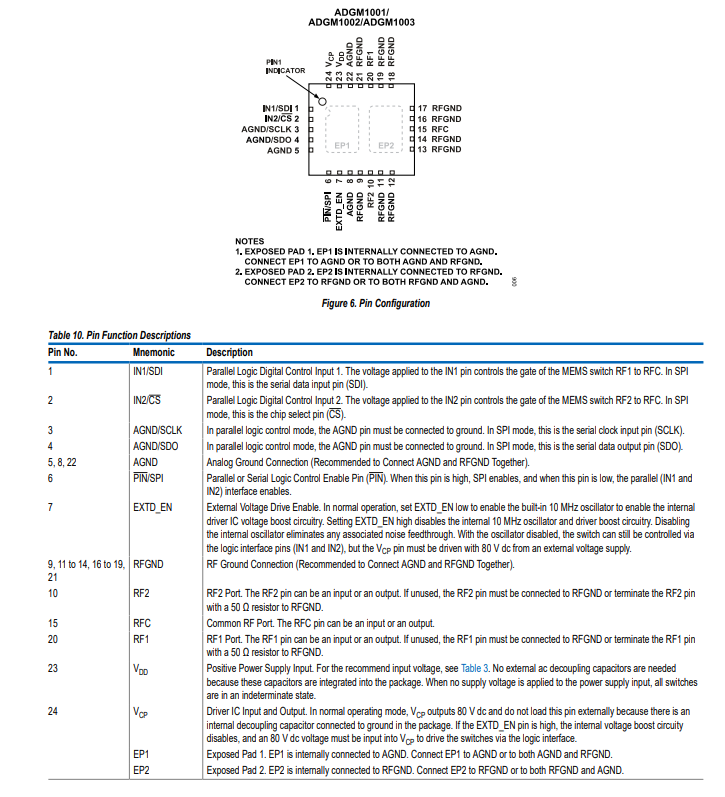

引脚配置描述

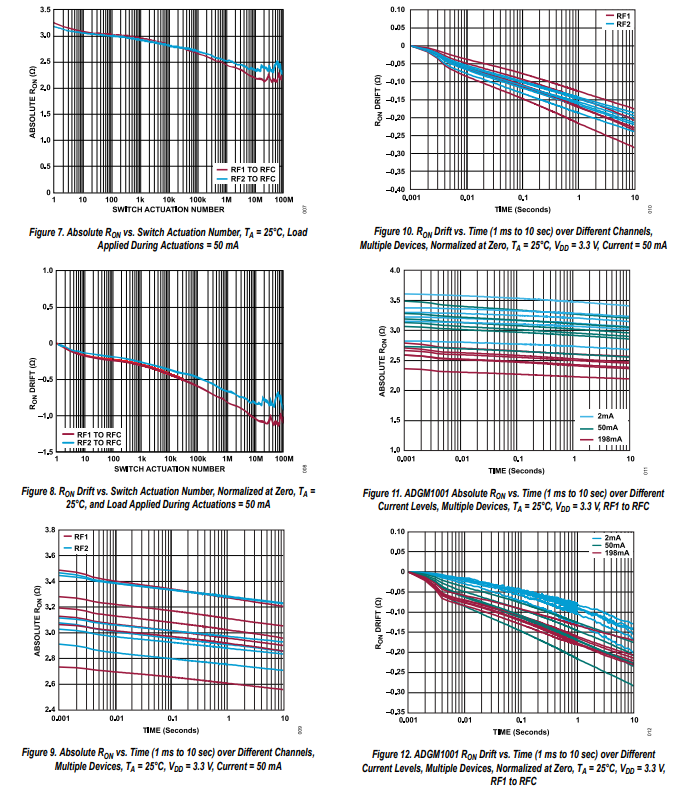

典型性能特征

工作原理

开关设计

ADGM1001是一款宽带单刀双掷(SP2T)开关,采用亚德诺半导体(Analog Devices)的微机电系统(MEMS)开关技术制造。该技术能够实现高功率、低损耗、低失真的宽带(GHz范围)开关,满足严苛的射频(RF)应用需求。

MEMS技术在该类产品中的一个关键优势是,能同时实现高频性能与出色的直流精度,这一特性结合卓越的可靠性以及极小的表面贴装封装尺寸,使MEMS开关成为所有射频及精密信号仪器应用的理想开关解决方案。

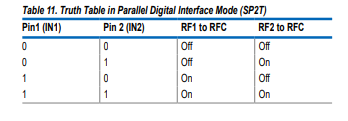

并行数字接口

ADGM1001可通过并行接口进行控制。通过该接口施加的标准互补金属氧化物半导体(CMOS)/低压晶体管 - 晶体管逻辑(LVTTL)信号,可控制所有开关通道的独立开启与关闭。

将引脚6(PIN/SPI)置低,可在双工SP2T模式下启用并行控制接口。引脚1和引脚2(IN1和IN2)控制ADGM1001的开关功能。当向这些引脚中的一个施加逻辑1时,相应的开关开启。反之,施加逻辑0时,开关关闭。在SP2T模式下,一次最多可将一个RFx输入连接到RFC。真值表见表11。

在并行模式下,引脚3和引脚4(AGND/SCLK和AGND/SDO)分别必须连接到地。

当引脚23(V DD )未施加电源电压时,所有开关均处于不确定状态。

SPI数字接口

当引脚6(PIN/SPI)置高时,ADGM1001可通过SPI数字接口进行控制。ADGM1001可使用SPI模式0或模式3,工作时SCLK频率最高为10MHz。使用SPI时,活动(active)、可寻址(addressable)模式为默认模式,此时通过16位SPI命令访问设备寄存器。ADGM1001也可在菊花链模式下工作。

ADGM1001的SPI引脚为(overline{CS})、SCLK、SDI和SDO 。使用SPI时,保持(overline{CS})为低电平。SDI上的数据在SCLK上升沿被捕获,SDO上的数据在SCLK下降沿输出。SDO采用推挽式输出驱动器架构,因此无需上拉电阻。两种可用的SPI操作模式均为可寻址模式和菊花链模式。

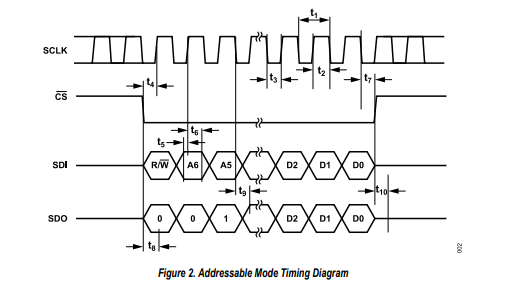

可寻址模式

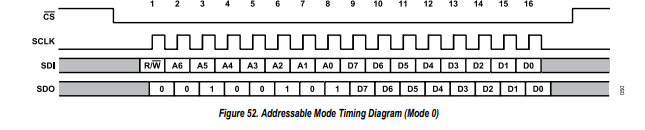

上电后,可寻址模式为ADGM1001的默认模式。可寻址模式下的单个SPI帧由(overline{CS})下降沿起始,(overline{CS})上升沿结束。它由16个SCLK周期组成。图52展示了SPI模式0下可寻址模式的时序图。

SPI命令的第一位指示该命令是读命令还是写命令。接下来的七位确定目标寄存器地址。剩余八位提供要写入目标寄存器的数据。读命令期间忽略最后八位,因为在此类时钟周期中,SDO输出目标寄存器中存储的数据。

在模式0中,(overline{CS})下降沿时,SDO在SCLK下降沿发送输出数据位(在模式3中,如图53所示,第一个SCLK下降沿被忽略 )。在SDO上观察到的对齐位为0x25。

目标寄存器地址在第八个SCLK上升沿确定。该寄存器的数据在第八个SCLK下降沿从SDO输出。读操作期间,第十五个SCLK下降沿输出数据。写操作期间,第十六个SCLK上升沿对寄存器进行写入。

-

Analog Devices Inc. ADGM1121 0Hz/直流至18GHz DPDT MEMS开关IC数据手册2025-06-14 981

-

ADGM1121 0 Hz/DC 至 18 GHz,DPDT MEMS开关技术手册2025-05-15 1139

-

ADGM1121 0Hz/直流至18GHz DPDT MEMS开关IC2024-12-09 2132

-

ADGM1304和ADGM1004如何增加测试仪器仪表的通道密度和测试功能2023-11-24 422

-

ADGM1001 SPDT MEMS开关如何简化数字/RF片上系统的测试流程2022-11-30 1747

-

EVAL-ADGM1304 EVAL-ADGM1304评估板2021-08-18 229

-

EVAL-ADGM1004SDZ EVAL-ADGM1004SDZ评估板2021-07-10 246

-

ADGM1004 S参数2021-05-28 549

-

AN-1360: ADGM1304和ADGM1004如何增加测试仪器仪表的通道密度和测试功能2021-03-22 704

-

ADGM1304: 0 Hz/DC 至14 GHz、集成驱动器的单刀四掷MEMS开关2021-03-19 728

-

ADGM1004 带集成驱动器的0 Hz至13 GHz、2.5kV HBM ESD SP4T MEMS开关2019-02-22 1019

-

开创性的5 kV ESD MEMS开关技术2018-11-01 2442

全部0条评论

快来发表一下你的评论吧 !