GD32H75E Arm Cortex-M7 32-bit MCU技术手册

描述

概述

GD32H75E产品系列支持EtherCAT®从站控制器。其主频高达600MHz,支持高达3840K Flash和1024K SARM。还集成了一系列数字和模拟外设资源,提供 BGA240 封装选项。其中搭配的是兆易创新的GDSCN832系列EtherCAT®从站控制器,GDESC系列提供QFN64封装型号。可广泛适用于伺服控制、变频驱动、工业PLC、工业通讯模块等各类应用场景。

数据表:*附件:GD32H75E Arm Cortex-M7 32-bit MCU技术手册.pdf

● 2 个内置PHY+ 1个MII扩展接口

● 8xFieldbus Memory Management Units (FMMUs)

● 8个同步管理器 (Sync Manager Entities)

● 8KB DPRAM

● 64-bit分布式时钟,支持主从站同步,精度低于1uS

● 支持8/16位串行/并行口通信,支持SPI/QSPI/OSPI从机接口,支持EXMC同步模式

● 支持1.8V-3.3V可变电压I/O

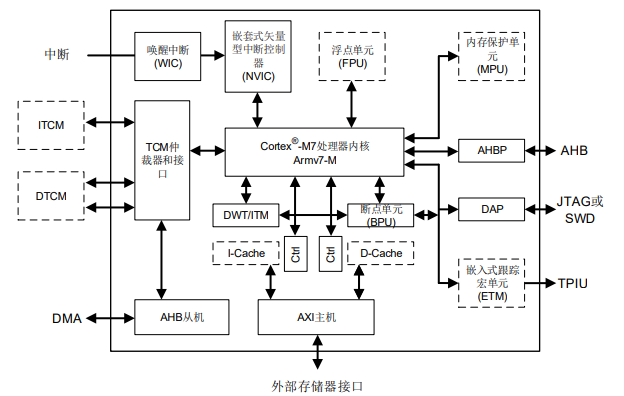

GD32H75E系列器件是基于Arm® Cortex®-M7处理器的32位通用微控制器。Arm® Cortex®-M7处理器包括64位AMBA4 AXI、32位AHB外设(AHBP)端口、32位AHB从设备端口,用于外部主设备访问内存,以及用于CoreSight调试组件的APB接口。存储器的组织采用了哈佛结构,预先定义的存储器映射和高达4 GB的存储空间,充分保证了系统的灵活性和可扩展性。

GD32H75E器件的系统架构示意图

Arm Cortex®-M7 处理器

Arm® Cortex®-M7处理器是一种高效、高性能的嵌入式处理器,具有低中断延迟、低调试成本以及与现有Cortex-M配置文件处理器的向后兼容性。处理器有一个有序的超标量流水线,因为有多个内存接口,这意味着许多指令可以双重发布,包括加载/加载和加载/存储指令对。Cortex®-M7是一款高性能处理器,具有带分支预测的6级超标量流水线和可选的FPU,能够进行单精度和可选的双精度运算。指令和数据总线已比以前的32位总线扩大到64位宽。

处理器支持的接口包括:

- 64位AXI4接口

- 32位AHB主机接口

- 32位AHB从机接口

- 64位指令TCM接口

- 2x32位数据TCM接口

处理器包含以下外部接口:

- AHBP接口

- AHBS接口

- AHBD接口

- 外部专用外围总线

- ATB接口

- TCM接口

- 交叉触发接口

- MBIST接口

- AXIM接口

Cortex®-M7处理器基于ARMv7架构,并且支持一个强大且可扩展的指令集,包括通用数据处理I/O控制任务、增强的数据处理位域操作、DSP(数字信号处理)和浮点运算指令。下面列出由Cortex®-M7提供的一些系统外设:

- 嵌套式向量型中断控制器(NVIC)

- 闪存地址重载及断点单元(FPB)

- 数据观测点及跟踪单元(DWT)

- 指令跟踪宏单元(ITM)

- JTAG或SWD调试接口

- 跟踪端口接口单元(TPIU)

Cortex-M7处理器结构框图

功能说明

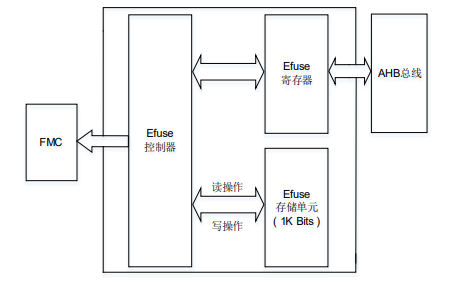

模块框图

熔丝控制器实现了熔丝的读写操作逻辑,其中熔丝模块的存储单元共计1K比特。

(图中展示了FMC与Eftuse控制器相连,Eftuse控制器分别与Eftuse寄存器、Eftuse存储单元(1K Bits)有读写操作连接,Eftuse寄存器与AHB总线相连 )

熔丝采用了double - bit冗余备份机制,前512比特数据和后512比特数据互相备份,从而有效保证数据的正确性。当编程熔丝的第n比特时,熔丝控制器会同时编程第n及n + 512比特。

当读取熔丝的第n比特时,熔丝控制器会同时读取第n及n+512比特,并将读取的结果进行或运算,最终将运算结果返回至参数寄存器中。以上过程全部由芯片内部进行处理,用户操作时只需访问前512比特即可,后512比特数据用户不可访问。

-

GD32H75E MCU规格书2025-02-07 951

-

GD32H737xx系列Arm Cortex-M7 MCU数据手册2024-01-03 1268

-

GD32E50x Arm®Cortex®-M33 32位MCU用户手册2023-12-14 775

-

CLM32L003 ARM Cortex M0+ 32-bit MCU数据手册2023-10-10 910

-

GD32F10x Arm Cortex-M3 32-bit MCU用户手册2023-09-20 665

-

IAR全面支持GD32H7系列超高性能MCU开发解决方案2023-07-17 3249

-

IAR全面支持兆易创新基于Arm Cortex-M7内核的超高性能MCU2023-07-13 2058

-

首款Cortex-M7内核超高性能MCU性能揭秘2023-05-25 2086

-

ARM Cortex M7技术参考手册2022-09-28 1545

-

stm32h7内存分配_STM32H7 - ARM Cortex-M7 MCUs (400 MHz) - STMicroelectronics2021-12-07 1189

-

浅析ARM对于Cortex-M7的期待与策略2014-10-02 4157

全部0条评论

快来发表一下你的评论吧 !