MAX9377/MAX9378任意逻辑至LVPECL/LVDS转换器,引脚可设置四分频电路技术手册

描述

概述

MAX9377/MAX9378是一种全差分、高速、低抖动的任意电平到LVPECL/LVDS的转换器,具有有四分频选择引脚。其极低的传输延迟和高速等特性,尤其适合于多种高速网络路由和背板应用,在非分频模式下工作速度高达2GHz。

MAX9377/MAX9378可接受任何电源电压范围内、幅度不小于100mV的差分信号。输入完全兼容于LVDS、LVPECL、HSTL和CML差分信号标准,MAX9377输出满足LVPECL电平,具有足够的电流驱动50Ω传输线。MAX9378输出特性满足LVDS电平,符合ANSI EIA/TIA-644 LVDS标准。

MAX9377/MAX9378提供8引脚µMAX形式封装,工作于+3.3V单电源、-40°C至+85°C的温度范围。

数据表:*附件:MAX9377 MAX9378任意逻辑至LVPECL LVDS转换器,引脚可设置四分频电路技术手册.pdf

应用

- 背板逻辑标准转换

- DLC

- DSLAM

- 局域网(LAN)

- WAN

特性

- 保证2GHz工作频率

- 接受LVDS/LVPECL/任意电平输入

- 四分频选择功能

- 421ps (典型)传输延迟(MAX9733)

- 30ps (最大)脉冲扭曲

- 2ps

RMS(最大)随机抖动 - 为确保AC特性,最小差分输入100mV

- 带温度补偿的LVPECL输出

- 工作电源电压范围+3.0V至+3.6V

- ESD保护:>2kV人体模型(HBM)

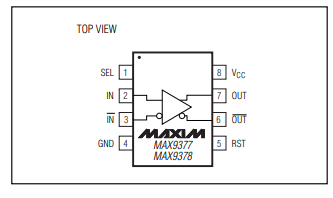

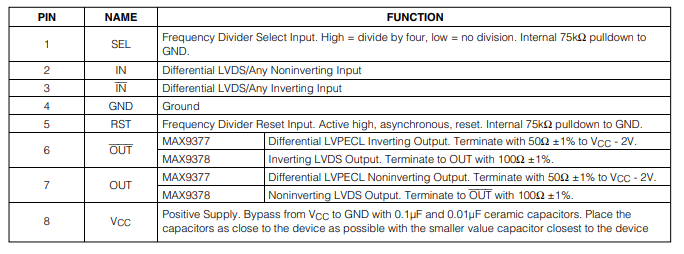

引脚配置描述

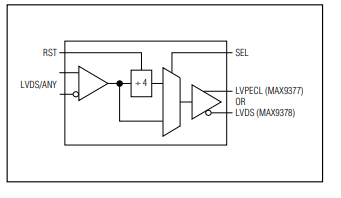

框图

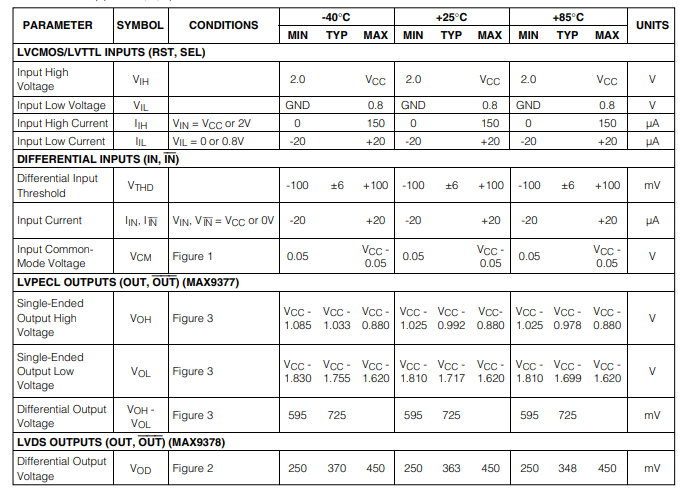

DC电气特性

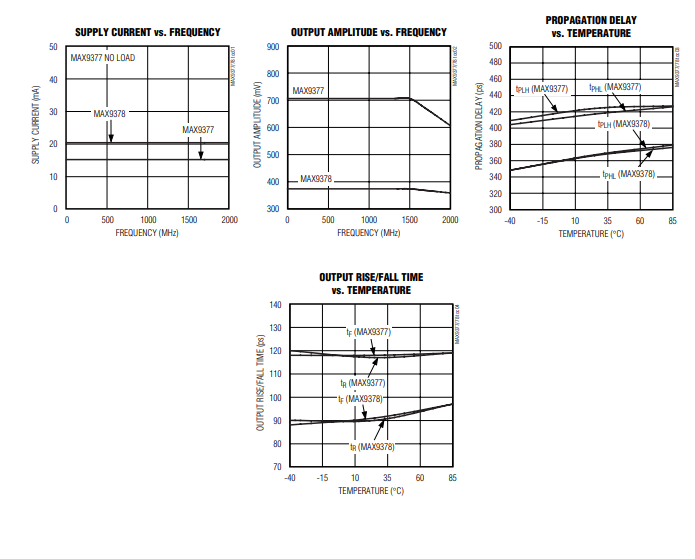

典型操作特性

应用信息

LVPECL输出端端接(MAX9377)

将MAX9377的LVPECL输出端用50Ω电阻端接到(V_{CC} - 2V ),或采用等效的戴维南端接方式。分别对OUT和 overline{OUT} 进行相同的端接,以减少输出失真。当从差分输出端引出单端信号时,请勿同时端接OUT和 overline{OUT} 。

确保输出电流不超过绝对最大额定值中规定的值。在所有工作条件下,都应遵守器件的总热限制。

LVDS输出端端接(MAX9378)

MAX9378的LVDS输出为电流导向型器件,无需端接电阻即可产生输出电压。端接电阻应与传输线的差分阻抗匹配。输出电压电平取决于端接电阻上的电压降。MAX9378针对点对点通信进行了优化,100Ω端接电阻与接收输入匹配。端接电阻值可在90Ω至132Ω之间变化,具体取决于传输介质的特性阻抗。

电源去耦

使用0.1μF和0.01μF的高频表面贴装陶瓷电容将 V_{CC} 旁路至地。尽可能将电容放置在靠近器件引脚的位置,0.01μF的电容应离器件引脚最近。

走线

电路板的走线布局对于保持高速差分信号的信号完整性至关重要。保持信号完整性在一定程度上是通过减少信号反射和偏斜,以及提高共模噪声抗扰度来实现的。

信号反射是由50Ω特性阻抗的走线不连续造成的。通过保持差分走线之间的距离、不使用尖锐转角或过孔来避免不连续情况。保持走线间距一致也能提高共模噪声抗扰度。通过使差分走线的电气长度匹配来减少信号偏斜。

-

MAX9370/MAX9371/MAX9372 LVTTL/TTL至差分LVPECL/PECL转换器技术手册2025-05-19 1314

-

MAX9376 LVDS/任意逻辑至LVPECL/LVDS、双路电平转换器技术手册2025-05-16 1286

-

MAX9152 800Mbps、LVDS/LVPECL至LVDS、2 x 2交叉点开关技术手册2025-04-16 1432

-

请问一下D触发器怎样实现四分频呢?2023-05-10 4502

-

MAX9377EUA+ 逻辑器件 - 转换器,电平移位器2023-02-10 75

-

10-37GHz CMOS四分频器的设计2010-12-29 949

-

MAX14569 双对单向逻辑电平转换器2010-10-08 1097

-

MAX9376 LVDS/任意逻辑至LVPECL/LVDS、2009-12-19 1960

-

五分频电路,四分频电路2009-06-22 14863

-

四分频器2009-04-11 3890

全部0条评论

快来发表一下你的评论吧 !