用移位寄存器实现边沿检测的技巧

FPGA/ASIC技术

描述

本文记录一下关于用移位寄存器实现边沿检测的技巧。要学会硬件思维式的“模块式”读写代码,那么请多看别人的代码,并用ISE或者VIVADO综合出来看看。

边沿检测

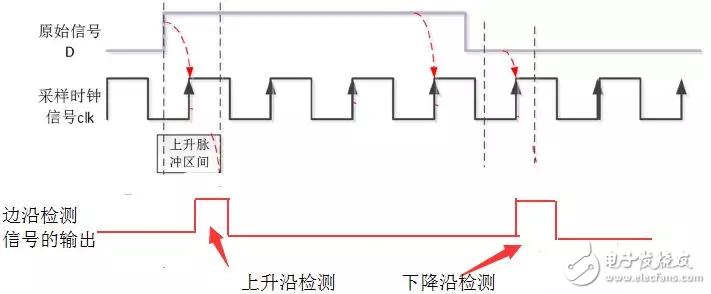

边沿检测,顾名思义,就是检查信号的边沿,当信号的上升沿或者下降沿到来时,获取一个脉冲信号,时序图如下所示:

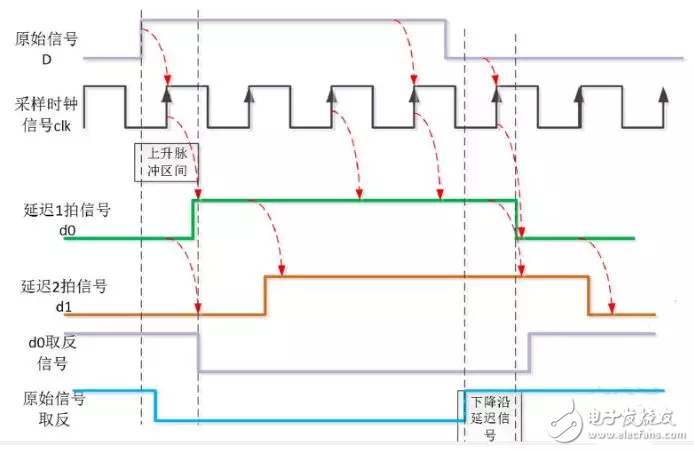

上图的检测信号同时输出上升沿检测和下降沿检测。那么这个波形怎么来的呢,我们来看看下面几组波形:

可以发现:

原始信号与延迟一拍的信号 d0 的反向信号相与,就是上升沿脉冲;

而原始信号取反,然后与延迟一拍信号d0相与就是下降沿脉冲。

如果担心采样不稳定,可以利用延迟两拍的 d1 信号进行相 与。如果担心不定态,还可以将脉冲信号进行锁存。

多级触发器的代码如下所示:

module DFF_N #(parameter N=1)(

2 input clk,

3 input reset,

4 input [N-1:0] D,

5 output [N-1:0] D_rising_edge, //上升沿检测

6 output [N-1:0] D_falling_edge //下降沿检测

7 );

8 reg [N-1:0]d0;

9 reg [N-1:0]d1;

10 reg [N-1:0]Q;

11 always@(posedge clk or negedge reset)

12 if(!reset)begin

13 d0 <= 0;

14 d1 <= 0;

15 Q <= 0;

16 end else begin

17 d0 <= D;

18 d1 <= d0;

19 Q <= d1;

20 end

21

22 assign D_rising_edge = ~d0 & D; //关键

23 assign D_falling_edge= d0 & ~D; //关键

24 endmodule

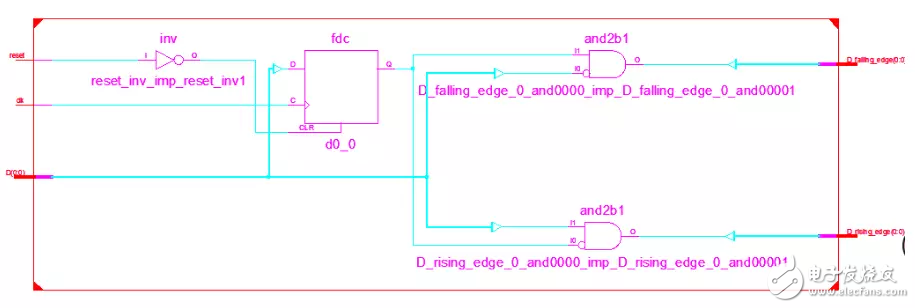

综合得到的电路如下所示:

这个电路把代码中的Q触发器优化掉了。两个输出信号D_rising_edge 、D_falling_edge分别输出上升沿检测信号脉冲和下降沿检测信号脉冲。

- 相关推荐

- 热点推荐

- 寄存器

-

移位寄存器右移是怎么移位的2024-07-12 3896

-

移位寄存器的工作原理 移位寄存器左移和右移怎么算2024-01-18 13688

-

移位寄存器的设计与实现2022-09-06 5656

-

移位寄存器的原理2019-07-15 77166

-

一文解析Matlab如何实现移位寄存器2018-04-26 17790

-

移位寄存器实验报告_移位寄存器原理2017-12-22 29369

-

寄存器与移位寄存器2016-05-20 1245

-

移位寄存器及其应用实验2012-07-16 7329

-

移位寄存器,移位寄存器是什么意思2010-03-08 18146

-

线性移位寄存器2010-01-12 2218

-

集成移位寄存器2009-03-20 1167

全部0条评论

快来发表一下你的评论吧 !