讨论SAR DAC响应时间和几种实现设计

描述

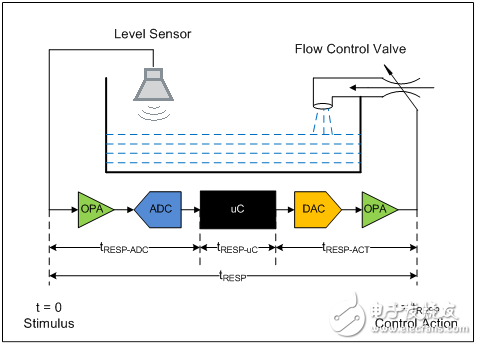

很多典型控制系统应用的目标是根据输入控制变量的状态来影响控制操作。其中的一些变量包括位置、速度、角度、水平、温度和压力。

对于这些控制变量中的每一个,你也许需要针对“精确的”测量、“准确的”控制操作和/或快速“响应时间”来优化设计。在这个系列博文中,我们将讨论SAR DAC响应时间和几种实现设计最佳效果的方法。

当我们考虑模拟电子元器件时:

-

系统的“高精度”要求转化为你的模拟块(放大器、基准、传感器等)和混合信号块(ADC,DAC等)所需要的性能技术规格。

-

系统的“响应时间”要求转化为主机控制器的选择和混合信号块(ADC,DAC等)的速度。

但是,让我们将注意力放到如何优化系统响应时间 (tRESP) 上来。其中一个比较有效的方法是在设计中的不同“非实时”块上,即ADC,主机控制器和DAC,安排系统响应时间。

-

ADC的响应时间 (tRESP-ADC) 是采样模拟输入与主机控制器内部相应数字编码可用时之间的时间差异。

-

主机控制器的响应时间 (tRESP-uC) 是控制器决定一个控制操作所花费的时间量。

-

DAC的响应时间 (tRESP-ACT) 是主机控制器决定一个控制操作和这个控制操作在DAC的输出上开动时之间的时间差异。

为什么使用一个SAR(逐次逼近寄存器)ADC?

SAR架构将高精度与快速响应组合在一起,使其成为很多工业用控制系统应用的理想选择。

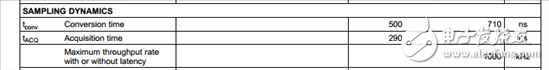

如果你仔细检查任何SAR DAC数据表,你将会发现技术规格中提到的吞吐率或速度。下面是一张ADS8881数据表:

那么SAR DAC的“响应时间” (tRESP-ADC) 只不过是吞吐率的倒数,对吗?

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

产品响应时间2018-06-16 0

-

请问AD9144输出响应时间?2018-08-03 0

-

SAR ADC响应时间实现迅速响应、快速控制的方法2018-09-12 0

-

SAR ADC响应时间和市场营销的类比2018-09-12 0

-

什么是响应时间2009-05-24 5643

-

什么是液晶电视的响应时间2010-03-27 4501

-

SAR ADC 响应时间:迅速响应、快速控制2017-04-18 1150

-

SAR ADC响应时间与市场营销有何相同点?2018-07-10 849

-

什么是单片机的中断响应时间2018-12-19 10474

-

面板响应时间有什么影响2019-01-14 4107

-

SAR DAC响应时间和几种实现设计最佳效果2022-02-06 1651

-

进程响应时间是指什么2023-11-17 1233

-

影响VCO响应时间的因素2024-08-20 733

-

光谱传感器的响应时间2025-01-27 262

全部0条评论

快来发表一下你的评论吧 !