一文看懂单电压基准与双电压基准区别

电子常识

描述

本文主要详解单电压基准与双电压基准区别,分别从三个拓扑结构,性能方面的不同以及占用的空间和成本方面来详细的解说。

一、两个基准电压的三个拓扑结构

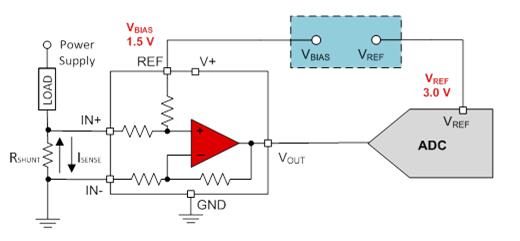

诸如图1中显示的双向电流感测的应用要求使用两个良好匹配的低漂移基准电压。第一个电压,VREF定义ADC的满量程范围。需要一个偏置电 压,VBIAS,来电平位移双极信号。需要使VBIAS= VREF/2,这样的话,ADC的正负摆幅相等。

图1:低漂移双向单电源低端电流感测系统

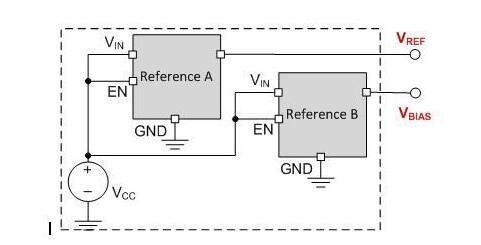

如图2中显示,使用两个单独的电压基准来提供一个简单且直接的方法。

图2:解决方案1(两个独立的基准)

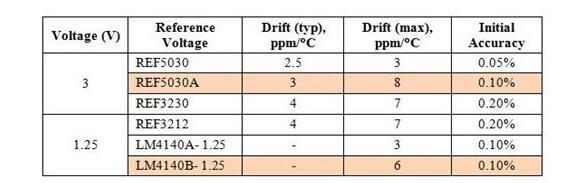

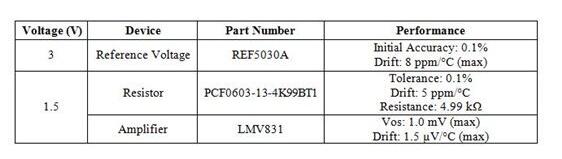

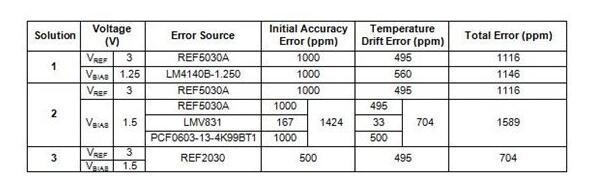

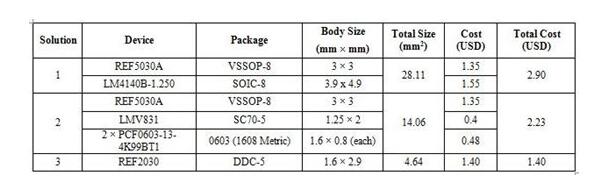

对于图1中的应用,VREF和VBIAS分别为3.0V和1.5V。表1列出了一对低漂移基准。在将漂移、准确度和成本考虑在内时,REF5030A 是针对3V基准电压的不错选择。不幸的是,低漂移、固定1.5V基准是不太容易得到的。在这个情况下,你可以选择一个1.25V基准,诸如 LM4149B,虽然这个选择使正负范围失衡。

表1:低漂移电压基准

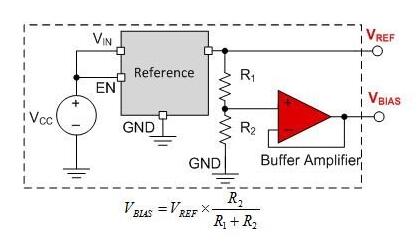

第二解决方案是可行的,使用图3中显示的分压器指定一个3V电压基准。

图3:解决方案2(基准+分压器+缓冲器)

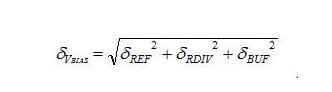

在这里,VBIAS的漂移,如方程式 (1) 所示,由基准 (δREF)、电阻分压器网络 (δRDIV)和缓冲放大器 (δBUF) 的漂移所导致。

对于一个相类似的低漂移解决方案,选择具有0.1%耐受值和5ppm/°C温度漂移的电阻器。考虑到放大器的满量程范围为1.5V,缓冲放大器的偏移 不是很明显。要达到输入偏移电压所导致的误差为0.1%和1ppm/°C漂移误差的目标,此放大器应该具有少于1.5mV的偏移电压和1.5µV/°C的 漂移。表2显示为这个解决方案所选择的器件。要获得与组件选择的更多细节,请参考TIPD156,这是一款TI设计参考库中的电流感测参考设计。

表2:第二个解决方案中的组件

二、性能方面

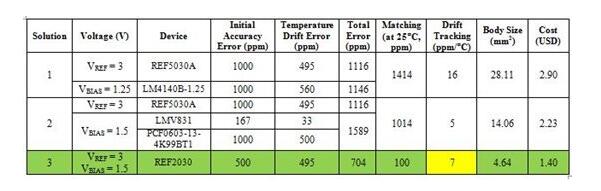

将从三个方面,即他们输出之间的总体误差、漂移跟踪和匹配,来比较这三种解决方案的性能。

总体误差

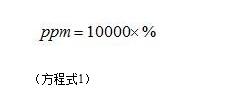

方程式 (1) 将用百分比 (%) 给出的技术规格转换为百万分比 (ppm) 表示的技术规格。

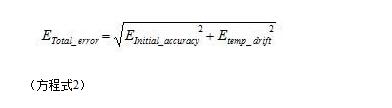

每个电压输出的总体误差性能指标取决于他的初始精度和工作温度范围内的漂移,如方程式(2) 中所给出的那样。

在解决方案1中,由于在数据表中没有指定LM4140B的漂移典型值,小编们使用70ºC温度范围内的最大漂移技术规格来进行计算。在解决方案2中,偏 移电压 (VBIAS) 由REF5030A,电阻器网络和一个缓冲器产生。因此,正如第一部分中方程式 (1) 所指定的那样,初始精度和漂移可以表示为这三个误差源的RSS值。由于REF2030和REF5030A使用打包方法来确定漂移,计算的温度范围为整个工 作温度范围,或者说165ºC。

表1显示VREF在解决方案1和解决方案2中具有相同的性能时,他的VBIAS输出的误差会大很多。需要注意的是,VBIAS在解决方案2中的误差包括来自VREF的误差。由于两个输出上的高初始精度和低温度漂移,解决方案3在三个解决方案中具有最低误差。

表1:每个输出电压误差原因比较

漂移跟踪和匹配

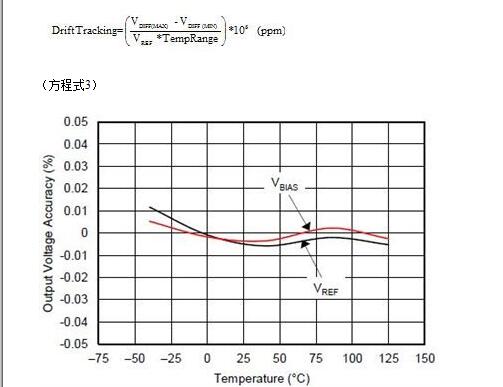

这个双输出系统的另外一个重要技术规格是漂移跟踪,这个参数描述了特定温度范围内两个电压之间的匹配准确度,计算方法如方程式 (3) 所示。图1显示了REF2030的漂移跟踪性能典型值。

图1:VREF和VBIAS跟踪与温度之间的关系图

由于小编们在解决方案1中采用了两个独立的电压基准,理论上来讲,这两个基准也许不会直接相互跟踪,所以跟踪是他们最大温度漂移 (11 ppm/ºC) 的RSS值。由于LM4140B的额定温度范围只在0°C至70ºC之间,这个漂移跟踪只适用于这个温度范围。

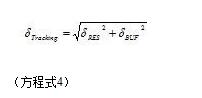

在解决方案2中,由于VREF的误差在两个输出上同时存在,VREF和VBIAS之间的漂移跟踪 (δTracking) 只取决于电阻器网络 (δRES) 和缓冲器 (δBUF) 的漂移,计算方法如方程式 (4) 所示。

三、占用的空间和成本

空间占用和成本

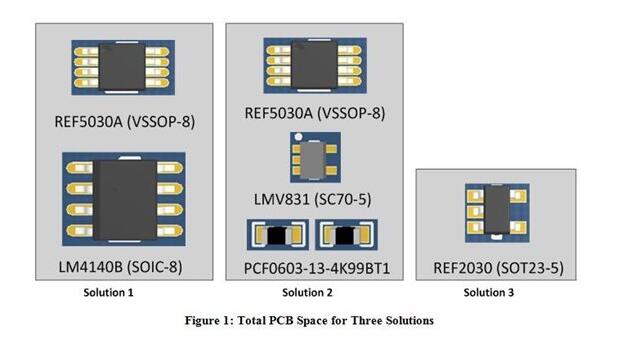

除了系统性能之外,在高密度应用中,PCB面积要求会十分关键。图1中给出了每个解决方案的总PCB空间一览(未考虑去耦合电容器)。

下方的表1显示所需空间的简单计算结果(只考虑器件本体尺寸)。通过从一个封装尺寸为4.64 mm2的集成解决方案中提供双输出,相对于解决方案1和解决方案2,REF2030将占用的总空间分别减少了83%和67%。从成本角度 看,REF2030仅为1.4美元,比解决方案1和2分别低52%和30%。

表1:空间占用和成本

结论

解决方案1

有两个独立的电压基准构成,解决方案1非常简单直接且易于实现。然而,其缺点也很明显:电压选项有限,在输出间无直接漂移跟踪。此外,解决方案1中使用的两个低漂移高精度基准价格很高。

解决方案2

虽然需要使用更多组件并占用更大主板空间,解决方案2比解决方案1的成本更低,并具有更好的漂移跟踪。然而,解决方案2中VBIAS的精度要逊于解决 方案1,这是因为他取决于VREF的漂移、分压器和缓冲放大器。在有利方面,解决方案2在设计不同偏置电压时比较灵活,在这些设计中,VBIAS≠ VREF/2。

解决方案3

解决方案3最显著的不同就是其单芯片解决方案。这个设计具有最佳的初始精度、更低的成本以及更小的PCB空间占用。事实上,解决方案3输出匹配比解决 方案2好90%,占用的空间小67%,成本降低30%。换句话说,如果你的设计目标是一款低漂移系统,并且你不想在获得高精度性能方面花费过多的话,解决 方案3 (REF2030) 会是一个好的选择。

表2:最终比较结果

- 相关推荐

- 热点推荐

- 电压基准

-

为什么要用基准电压源?如何选择基准电压源?基准电压源怎么选型号?2023-07-17 5048

-

如何选择合适的电压基准?2022-11-15 691

-

#硬声创作季 6.电压基准选型步骤Mr_haohao 2022-10-20

-

电压基准2021-06-16 739

-

电压基准的结构和特性_如何选择电压基准2019-09-29 12176

-

单电压基准与双电压基准的对决-第一部分2018-09-12 2576

-

合适的电压基准怎么选?2018-07-10 3991

-

基准电压芯片有什么用_基准电压芯片如何使用2018-01-29 119194

-

精密双极性电压基准的建立2011-10-09 2235

-

电压基准及时间基准基础知识2010-06-11 686

-

如何选择最佳的电压基准源2010-01-08 1137

-

精密基准双极性输出基准电压源电路图2009-04-15 1644

-

选择最佳的电压基准源2009-01-23 2327

全部0条评论

快来发表一下你的评论吧 !