8086CPU引脚图及功能_8086CPU组成部分

cpu

描述

8086简介

Intel8086是一个由Intel于1978年所设计的16位微处理器芯片,是x86架构的鼻祖。Intel8086拥有四个16位的通用寄存器,也能够当作八个8位寄存器来存取,以及四个16位索引寄存器(包含了堆栈指标)。资料寄存器通常由指令隐含地使用,针对暂存值需要复杂的寄存器配置。它提供64K8位元的输出输入(或32K16位元),以及固定的向量中断。大部分的指令只能够存取一个内存位址,所以其中一个操作数必须是一个寄存器。运算结果会储存在操作数中的一个寄存器。

8086的性能特点

16位的内部结构,16位双向数据信号线;

20位地址信号线,可寻址1M字节存储单元;

较强的指令系统;

利用第16位的地址总线来进行I/O端口寻址,可寻址64K个I/O端口;

中断功能强,可处理内部软件中断和外部中断,中断源可达256个;

单一的+5V电源,单相时钟5MHz。

另外,Intel公司同期推出的Intel8088微处理器一种准16位微处理器,其内部寄存器,内部操作等均按16位处理器设计,与Intel8088微处理器基本上相同,不同的是其对外的数据线只有8位,目的是为了方便地与8位I/O接口芯片相兼容。

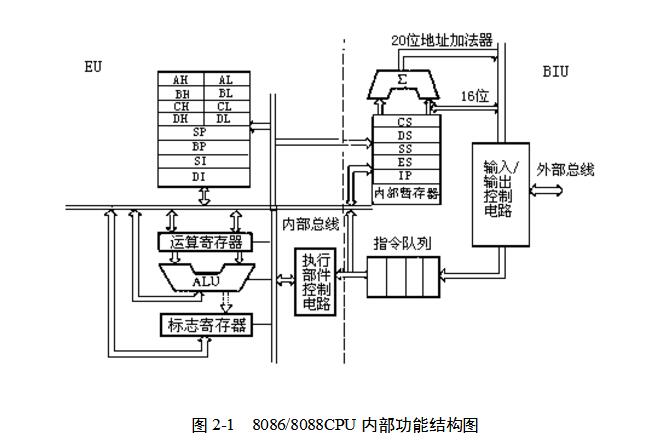

8086的组成部分

1、总线接口部件BIU

总线接口单元的功能:

从内存中取指令到指令预取队列

负责与内存或输入/输出接口之间的数据传送

在执行转移程序时,BIU使指令预取队列复位,从指定的新地址取指令,并立即传给执行单元执行。

2、执行部件EU

执行单元的功能:

指令译码

指令执行————————-在ALU中完成

暂存中间运算结果—————-通用寄存器

保存运算结果特征—————-标志寄存器flags

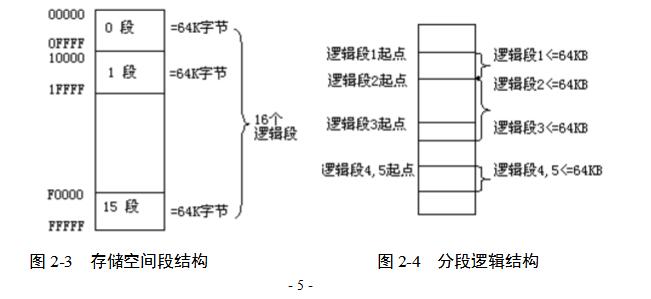

存储器组织

1.存储容量

8086有20根地址总线,因此,它可以直接寻址的存储器单元数为220=1Mbyte

2.物理地址

8086可直接寻址1Mbyte的存储空间,其地址区域为00000H—FFFFFH,与存储单元一一对应的20位地址,我们称之为存储单元的物理地址。3.存储器的分段及段地址

由于CPU内部的寄存器都是16位的,为了能够提供20位的物理地址,系统中采用了存储器分段的方法。规定存储器的一个段为64KB,由段寄存器来确定存储单元的段地址,由指令提供该单元相对于相应段起始地址的16位偏移量。

这样,系统的整个存储空间可分为16个互不重叠的逻辑段,如图2-3所示。存储器的每个段的容量为64KB,并允许在整个存储空间内浮动,即段与段之间可以部分重叠、完全重叠、连续排列,非常灵活,如图2-4所示。

4.偏移地址

偏移地址是某存储单元相对其所在段起始位臵的偏移字节数,或简称偏移量。它是一个16位的地址,根据指令的不同,它可以来自于CPU中不同的16位寄存器(IP、SP、BP、SI、DI、BX等)。

5.物理地址的形成

物理地址是由段地址与偏移地址共同决定的,段地址来自于段寄存器(CS、DS、ES、SS),是十六位地址,由段地址及偏移地址计算物理地址的表达式如下:

物理地址=段地址×16+偏移地址

例如:系统启动后,指令的物理地址由CS的内容与IP的内容共同决定,由于系统启动的CS=0FFFFH,IP=0000H,所以初始指令的物理地址为0FFFF0H,我们可以在0FFFF0H单元开始的几个单元中,固化一条无条件转移指令的代码,即转移到系统初始化程序部分。

6.存储器分段组织带来存储器管理的新特点

首先,在程序代码量、数据量不是太大的情况下,可使它们处于同一段内,即使它们在64Kbyte的范围内,这样可以减少指令的长度,提高指令运行的速度;

其次,内存分段为程序的浮动分配创造了条件;

第三,物理地址与形式地址并不是一一对应的,举例:6832H:1280H,物理地址为695A0H。

第四,各个分段之间可以重叠

7.特殊的内存区域

8088/8086系统中,有些内存区域的作用是固定的,用户不能随便使用,如:中断矢量区:00000H—003FFH共1K字节,用以存放256种中断类型的中断矢量,每个中断矢量占用4个字节,共256×4=1024=1K显示缓冲区:B0000H—B0F9FH约4000(25×80×2)字节,是单色显示器的显示缓冲区,存放文本方式下,所显示字符的ASCII码及属性码;B8000H—BBF3FH约16K字节,是彩色显示器的显示缓冲区,存放图形方式下,屏幕显示象素的代码。

启动区:FFFF0H—FFFFFH共16个单元,用以存放一条无条件转移指令的代码,转移到系统的初始化部分。

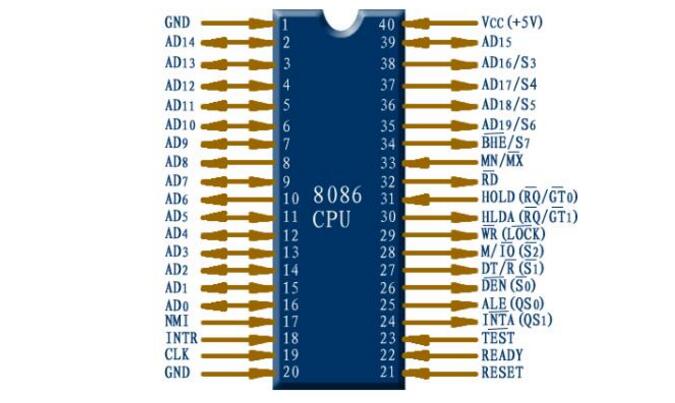

8086引脚图及功能

⑴AD15~AD0(addressdatabus):地址/数据总线,双向,三态。

这是一组采用分时的方法传送地址或数据的复用引脚。根据不同时钟周期的要求,决定当前是传送要访问的存储单元或I/O端口的低16位地址,还是传送16位数据,或是处于高阻状态。

⑵A19/S6~A16/S3(address/status):地址/状态信号,输出,三态。

这是采用分时的方法传送地址或状态的复用引脚。其中A19~A16为20位地址总线的高4位地址,S6~S3是状态信号。S6表示CPU与总线连接的情况,S5指示当前中断允许标志IF的状态。S4,S3的代码组合用来指明当前正在使用的段寄存器。S4,S3的代码组合及对应段寄存器的情况。

⑶BHE(低)/S7(bushighenable/status):允许总线高8位数据传送/状态信号,输出,三态。

为总线高8位数据允许信号,当低电平有效时,表明在高8位数据总线D15~D8上传送1个字节的数据。S7为设备的状态信号。

⑷RD/(read):读信号,输出,三态,低电平有效。

信号低电平有效时,表示CPU正在进行读存储器或读I/O端口的操作。

⑸READY(ready):准备就绪信号,输入,高电平有效。

READY信号用来实现CPU与存储器或I/O端口之间的时序匹配。当READY信号高电平有效时,表示CPU要访问的存储器或I/O端口已经作好了输入/输出数据的准备工作,CPU可以进行读/写操作。当READY信号为低电平时,则表示存储器或I/O端口还未准备就绪,CPU需要插入若干个“TW状态”进行等待。

⑹INTR(interruptrequest):可屏蔽中断请求信号,输入,高电平有效。

8086CPU在每条指令执行到最后一个时钟周期时,都要检测INTR引脚信号。INTR为高电平时,表明有I/O设备向CPU申请中断,若IF=1,CPU则会响应中断,停止当前的操作,为申请中断的I/O设备服务。

⑺TEST/(test):等待测试控制信号,输入,低电平有效。

信号用来支持构成多处理器系统,实现8086CPU与协处理器之间同步协调的功能,只有当CPU执行WAIT指令时才使用。

⑻NMI(non-maskableinterrupt):非屏蔽中断请求信号,输入,高电平有效。

当NMI引脚上有一个上升沿有效的触发信号时,表明CPU内部或I/O设备提出了非屏蔽的中断请求,CPU会在结束当前所执行的指令后,立即响应中断请求。

⑼RESET(reset):复位信号,输入,高电平有效。

RESET信号有效时,CPU立即结束现行操作,处于复位状态,初始化所有的内部寄存器。复位后各内部寄存器的状态,当RESET信号由高电平变为低电平时,CPU从FFFF0H地址开始重新启动执行程序。

⑽CLK(clock):时钟信号,输入。

CLK为CPU提供基本的定时脉冲信号。8086CPU一般使用时钟发生器8284A来产生时钟信号,时钟频率为5MHz~8MHz,占空比为1:3。

⑾VCC电源输入引脚。

8086CPU采用单一+5V电源供电。

⑿GND:接地引脚。

⒀MN/MX/(minimum/maximum):最小/最大模式输入控制信号。

引脚用来设置8086CPU的工作模式。当为高电平(接+5V)时,CPU工作在最小模式;当为低电平(接地)时,CPU工作在最大模式。

CPU工作于最小模式时使用的引脚信号

当引脚接高电平时,CPU工作于最小模式。此时,引脚信号24~31的含义及其功能如下。

⑴M/IO/(memoryI/Oselect):存储器、I/O端口选择控制信号。

信号指明当前CPU是选择访问存储器还是访问I/O端口。为高电平时,访问存储器,表示当前要进行CPU与存储器之间的数据传送。为低电平时,访问I/O端口,表示当前要进行CPU与I/O端口之间的数据传送。

⑵WR/(write):写信号,输出,低电平有效。

信号有效时,表明CPU正在执行写总线周期,同时由信号决定是对存储器还是对I/O端口执行写操作。

⑶INTA/(interruptacknowledge):可屏蔽中断响应信号,输出,低电平有效。

CPU通过信号对外设提出的可屏蔽中断请求做出响应。为低电平时,表示CPU已经响应外设的中断请求,即将执行中断服务程序。

⑷ALE(addresslockenable):地址锁存允许信号,输出,高电平有效。

CPU利用ALE信号可以把AD15~AD0地址/数据、A19/S6~A16/S3地址/状态线上的地址信息锁存在地址锁存器中。

⑸DT/(datatransmitorreceive):数据发送/接收信号,输出,三态。

DT/信号用来控制数据传送的方向。DT/为高电平时,CPU发送数据到存储器或I/O端口;DT/为低电平时,CPU接收来自存储器或I/O端口的数据。⑹DEN/(dataenable):数据允许控制信号,输出,三态,低电平有效。

信号用作总线收发器的选通控制信号。当为低电平时,表明CPU进行数据的读/写操作。

⑺HOLD(busholdrequest):总线保持请求信号,输入,高电平有效。

在DMA数据传送方式中,由总线控制器8237A发出一个高电平有效的总线请求信号,通过HOLD引脚输入到CPU,请求CPU让出总线控制权。

⑻HLDA(holdacknowledge):总线保持响应信号,输出,高电平有效。

HLDA是与HOLD配合使用的联络信号。在HLDA有效期间,HLDA引脚输出一个高电平有效的响应信号,同时总线将处于浮空状态,CPU让出对总线的控制权,将其交付给申请使用总线的8237A控制器使用,总线使用完后,会使HOLD信号变为低电平,CPU又重新获得对总线的控制权。

CPU工作于最大模式时使用的引脚信号

当引脚接低电平时,CPU工作于最大模式。此时,引脚信号24~31的含义及其功能如下。

⑴S2,S1,S0(statussignals):总线周期状态信号,输出,低电平有效。

⑵RQ/,GT/(request/grant):总线请求允许信号输入/总线请求允许输出信号,双向,低电平有效。

该信号用以取代最小模式时的HOLD/HLDA两个信号的功能,是特意为多处理器系统而设计的。当系统中某一部件要求获得总线控制权时,就通过此信号线向8086CPU发出总线请求信号,若CPU响应总线请求,就通过同一引脚发回响应信号,允许总线请求,表明8086CPU已放弃对总线的控制权,将总线控制权交给提出总线请求的部件使用。RQ/GT0优先级高于RQ/GT1。

⑶LOCK/(lock)总线封锁信号,输出,低电平有效。

信号有效时,表示此时8086CPU不允许其他总线部件占用总线。

⑷QS1,QS0(queuestatus):指令队列状态信号,输出。

QS1和QS0信号的组合可以指示总线接口部件BIU中指令队列的状态,以便其他处理器监视、跟踪指令队列的状态。

-

微机原理02--8086结构2021-12-09 1203

-

计算机由哪几部分组成2021-07-29 1131

-

8086cpu工作原理2021-07-22 2149

-

8086cpu引脚口诀相关资料推荐2021-05-25 1561

-

求大佬分享关于8086CPU汇编指令速查手册2021-04-12 1372

-

8086cpu是16位的,内存单元只有8位怎么写进去?2019-03-12 4135

-

8086CPU中文资料汇总(8086引脚图及功能_工作原理及应用电路)2018-04-16 76161

-

PROTEUS下8086CPU的不可屏蔽中断(NMI)仿真2017-01-09 6355

-

小白求助~~请问,8086CPU能装载exe文件吗?2013-12-25 3398

-

8086CPU 汇编指令速查手册2010-10-17 4807

-

8086CPU设计微机最小系统.ppt2006-06-29 3373

全部0条评论

快来发表一下你的评论吧 !