定制化SoC阵列设计

电子说

描述

定制化SoC阵列设计融合了多核异构集成与分布式计算架构,其核心在于根据不同应用场景的需求,通过硬件模块化设计和软件定义能力实现算力密度与能效比的突破。以下是关键设计要素与技术特征:

一、架构设计原则

异构集成架构

采用CPU+GPU+NPU+专用加速器的组合模式,支持动态资源分配与硬件虚拟化技术,例如芯原平台支持多处理器协同工作并可选配ASIL D级功能安全岛

模块化扩展性

通过PCIe 5.0/CXL 2.0高速互连协议构建弹性集群,单节点支持3D封装集成内存与计算核心,实现TB/s级带宽扩展

二、核心技术实现

先进工艺优化

针对5nm/7nm车规工艺进行PPA(功耗/性能/面积)优化,结合Chiplet技术实现不同制程芯片的异构集成

高速互连系统

采用光互连总线探索量子-经典计算混合架构,通过低延时通信网络支持AI推理、边缘计算等混合负载

三、功能安全特性

基于ISO 26262认证的设计流程,集成硬件级安全隔离引擎,实现多租户场景下的数据安全防护

在自动驾驶决策系统中,通过冗余计算单元和实时监控机制保障功能安全完整性等级(ASIL)达D级

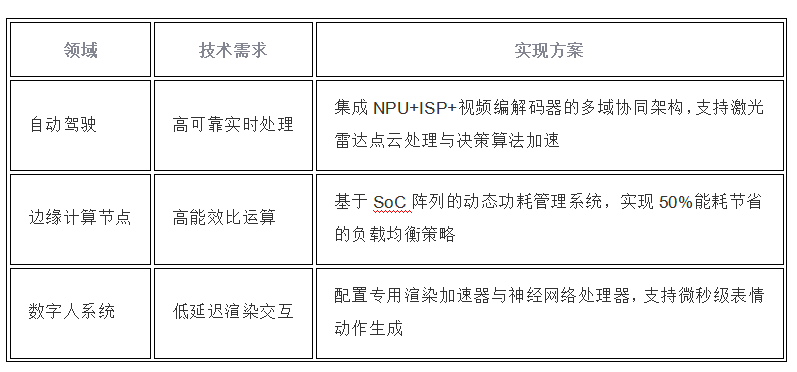

四、典型应用场景

五、设计流程创新

平台即服务(SiPaaS)模式:提供从芯片架构设计、验证到车规认证的全流程服务,包含安全需求分析、失效模式验证等20余项认证支持

自动化设计工具链:支持RISC-V与ARM指令集混合编排,实现IP核的灵活调用与验证覆盖率优化

这种设计范式已成功应用于智能座舱域控芯片,例如高通骁龙8775通过座舱域与智驾域的深度协同,实现4K导航渲染与HUD预警联动的实时响应能力。未来发展趋势聚焦于Chiplet互联标准化与光子计算集成,预计可将阵列服务器能效比再提升3-5倍。

审核编辑 黄宇

-

AMIS新模拟阵列法与定制互联层相结合减少成本及开发时间2018-08-27 1599

-

门阵列是什么?2019-08-21 5732

-

通用MCU呈现专用SOC化的趋势2021-02-21 2935

-

MCU呈现专用SOC化的趋势2021-11-01 1457

-

Socionext高端车载定制化SoC闪耀美国CES20232023-02-09 1054

-

门阵列,门阵列是什么是意思2010-03-26 2132

-

什么是soc芯片2010-09-10 50837

-

Altera 基于ARM的用户可定制SoC FPGA.2013-10-10 552

-

东芝将推出样品交付周期较短的新款结构化阵列2018-09-25 332

-

基于FPGA软核,定制你的SoC2019-04-22 2899

-

史密斯英特康为医疗应用市场提供了新的定制化网格阵列技术2022-11-09 899

-

AMD Xilinx SoC:定制PetaLinux中的FSBL2023-07-10 1586

-

高算力AI模组前沿应用:基于ARM架构的SoC阵列式服务器2023-07-27 1631

-

Cadence 与 Arm Total Design 合作,加速开发基于 Arm 的定制 SoC2023-10-25 1084

-

高通SoC阵列服务器2025-06-03 1126

全部0条评论

快来发表一下你的评论吧 !