MAX9169/MAX9170 4端口LVDS和LVTTL至LVDS转发器技术手册

描述

概述

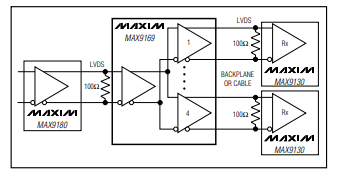

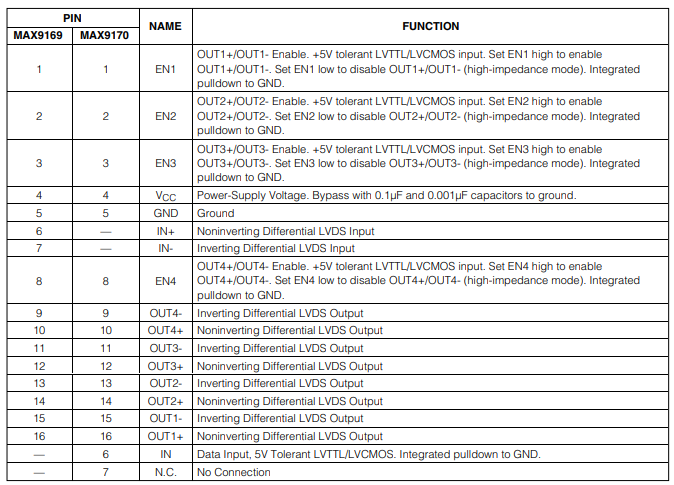

MAX9169/MAX9170是低抖动、低电压、差分LVDS/LVTTL至LVDS中继器,尤其适合于那些要求高速数据或时钟分配、且尽可能减小功耗和尺寸以及噪声的应用。器件接收单路LVDS (MAX9169)或LVTTL (MAX9170)输入,将其复现为4路LVDS输出。每路差分输出可驱动100Ω负载,允许在接收器输入端带有100Ω终端电阻的传输线上进行点到点信号分配。MAX9169和MAX9170引脚分别兼容于SN65LVDS104和SN65LVDS105,提供改进的脉冲扭曲性能。

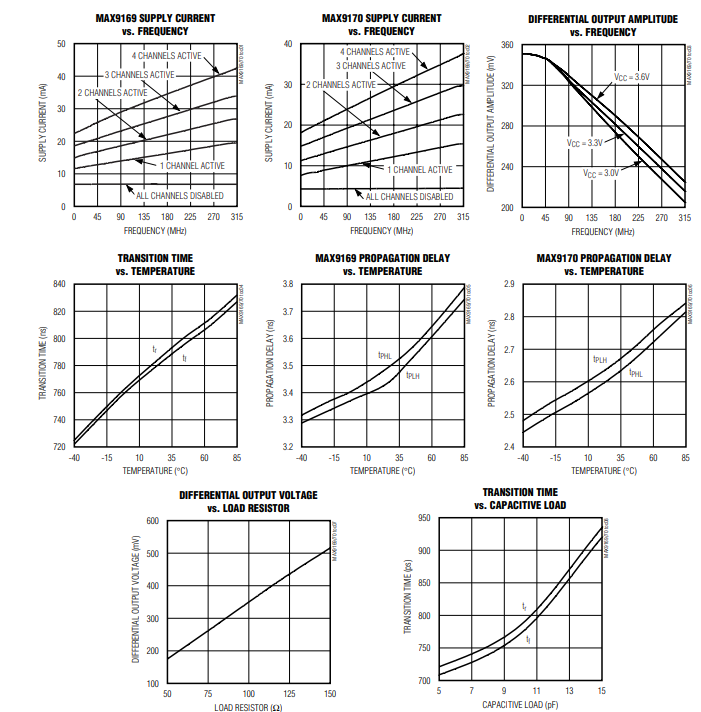

150ps (最大)的超低脉冲扭曲和200psP-P (最大)加性系统抖动等特性,保证在那些定时误差极其敏感的高速链路中,尤其是那些包含时钟和数据恢复电路,或串行器和解串器应用中,进行可靠地通讯。在整个3.0V至3.6V的工作电源范围内,其高速转换性能可以保证630Mbps的数据传输速率和小于120ps的通道间扭曲。

MAX9169的最大电源电流是30mA,MAX9170是25mA。LVDS输入和输出符合ANSI EIA/TIA-644标准。当输入处于无驱动的开路、终端匹配或短路时,MAX9169的安全失效特性将设置高输出。MAX9169/MAX9170提供16引脚TSSOP和SO封装,工作于-40°C至+85°C的扩展级温度范围。

对于SC70封装的LVDS线接收器,请参考MAX9130的数据资料。

数据表:*附件:MAX9169 MAX9170 4端口LVDS和LVTTL至LVDS转发器技术手册.pdf

应用

- 上/下路复用器

- 背板互连

- 蜂窝电话基站

- 时钟分配

- 数字交叉连接

- 网络路由器和交换机

- 点到点基带数据传输

特性

- 150ps (最大)脉冲扭曲

- 在630Mbps (2^23^ - 1) PRBS码型测试时,具有极低的200ps

P-P(最大)加性系统抖动 - 8ps

RMS(最大)加性随机抖动 - 120ps (最大)通道到通道扭曲

- 630Mbps数据速率

- 符合ANSI EIA/TIA-644 LVDS标准

- 最大30mA (MAX9169)或最大25mA (MAX9170)电源电流,比竞争产品改进15%

- LVDS输入(MAX9169)或+5V耐压的LVTTL/LVCMOS输入(MAX9170)

- 在无驱动差分输入时,安全失效电路置输出为高电平

- 额定10pF负载输出

- 独立的输出使能端

- 3.3V单电源

- 改进的SN65LVDS104 (MAX9169)/SN65LVDS105 (MAX9170)代用品

- 16引脚SO和TSSOP封装

应用电路

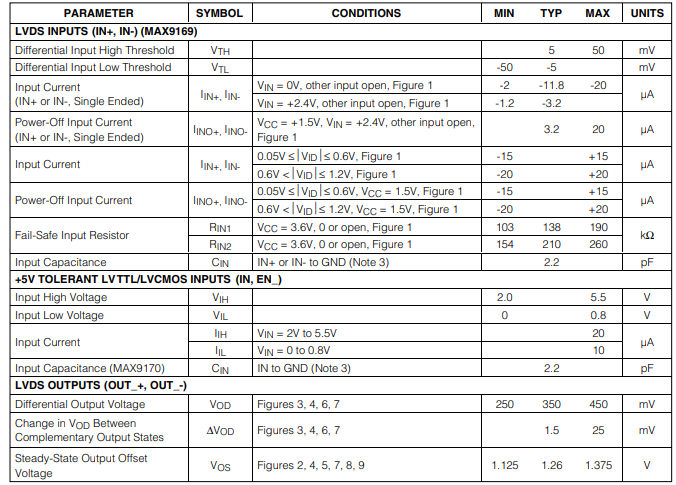

DC电气特性

典型操作特性

引脚配置描述

详细说明

LVDS(低压差分信号)是一种用于点到点和多点数据通信的信令方法,通过受控阻抗介质传输,符合ANSI TIA/EIA - 644和IEEE 1596.3标准。LVDS使用的电压摆幅比其他常见信令标准更低,在降低功耗的同时实现更高的数据速率,还能减少电磁干扰(EMI)以及系统对噪声的敏感度。

MAX9169/MAX9170是630Mbps的四端口转发器,适用于高速、低功耗应用。MAX9169电路接受LVDS输入,并具有故障安全输入电路。MAX9170具有一个 +5V 容限的单端LVTTL/LVCMOS输入。这两款器件都会在每个LVDS输出端重复输入信号。MAX9169可检测低至50mV、共模范围在 -|Vp|/2 至 2.4V - |Vp|/2 之间的差分信号。MAX9170的 +5V 容限LVTTL/LVCMOS输入包括电路,可在温度和电源电压变化时将判决阈值保持在恒定的 +1.5V。

MAX9169/MAX9170输出采用电流调节配置,可产生2.5mA至4.5mA的输出电流。这种电流调节方法可减少接地反弹和直通电流,提高噪声裕度和系统速度性能。输出为短路电流限制型,器件断电时阻抗较高。

MAX9169/MAX9170的电流调节输出需要电阻负载来端接信号,完成传输回路。由于器件切换的是电流方向而非电压电平,输出电压摆幅由端接电阻的阻值乘以输出电流决定。典型情况下,MAX9169/MAX9170的输出电流为3.5mA,当传输线端接100Ω电阻时,会产生350mV的输出电压(3.5mA×100Ω = 350mV)。逻辑状态由通过端接电阻的电流方向决定。

故障安全电路

MAX9169的故障安全功能在差分输入出现以下情况时将输出置为高电平:

- 开路

- 未驱动且短路

- 未驱动且端接

如果没有故障安全电路,当输入未驱动时,输入处的噪声可能会使输出切换,看起来像是系统正在发送数据。开路或未驱动的端接输入情况可能会在LVDS驱动器电缆断开或切断时出现,或者当LVDS驱动器输出因电缆阻抗过高而处于高阻抗状态时出现。短路输入可能是由于电缆故障引起。

当输入信号符合LVDS标准,输入共模电压小于Vcc - 0.3V且故障安全电路未激活时(图1)。如果输入开路、未驱动、短路、未驱动且并联端接,内部电阻会将两个输入拉高至Vcc - 0.3V以上,激活故障安全电路并强制输出为高电平。

应用信息

电源去耦

用高频表面贴装陶瓷电容(0.1μF和0.001μF)对Vcc进行去耦,尽可能将较小值的电容靠近器件的Vcc引脚并联安装。使用多个并联过孔,以最小化寄生电感。

走线、电缆和连接器

差分输入和输出连接的特性会影响MAX9169/MAX9170的性能。使用受控阻抗的走线、电缆和连接器,并匹配其特性阻抗。

通过将差分对的走线紧密排布在一起,确保噪声以共模方式耦合。通过匹配差分对中走线的电气长度来减少偏移。差分对中走线的过度偏移会导致磁场抵消降低。在走线之间保持恒定距离,以避免差分阻抗出现不连续性。

-

解析SN65LVDS10x:4端口LVDS与4端口TTL - LVDS中继器的卓越性能2025-12-31 462

-

MAX9205/MAX9207 10位、总线LVDS串行器技术手册2025-05-29 1023

-

MAX9130单路、500Mbps、LVDS线接收器,SC70封装技术手册2025-05-19 1175

-

MAX9376 LVDS/任意逻辑至LVPECL/LVDS、双路电平转换器技术手册2025-05-16 1266

-

MAX9180 400Mbps、低抖动、低噪声LVDS转发器,SC70封装技术手册2025-04-16 1056

-

SN65LVDS109/SN65LVDS117双4端口和双8端口LVDS中继器数据表2024-07-03 571

-

LVDS系统接口的解串器MAX9268资料推荐2021-04-01 1153

-

Maxim推出高速LVDS串行器/解串器MAX9259/MAX9260/MAX92652014-12-06 5965

-

MAX9234,MAX9236,MAX9238热插拔、21位、直流平衡、LVDS解串器2012-11-08 4695

-

MAX9205, MAX9207 10位、总线式LVDS串行2010-12-21 1467

-

空间转发器系统,空间转发器系统是什么意思2010-04-03 2267

-

MAX9244多路LVDS串并转换方案2010-02-14 3695

-

MAX9376 LVDS/任意逻辑至LVPECL/LVDS、2009-12-19 1956

全部0条评论

快来发表一下你的评论吧 !