MAX9315 1:5差分LVPECL/LVECL/HSTL时钟和数据驱动器技术手册

描述

概述

MAX9315是低扭曲、1:5差分驱动器,设计用于时钟和数据分配。这种器件允许选择两路输入之一。所选择的输入再生5路差分输出。差分输入经过调整后,可以允许单端输入,只需将片上VBB电源接到一个输入端作为参考电压即可。

MAX9315具有低输出到输出扭曲(20ps)的特点,尤其适合于通过背板或电路板上的时钟和数据分配。在与差分HSTL和LVPECL信号接口时,这些器件工作在+2.375V至+3.8V的电源范围,能够实现在+2.5V或+3.3V标称电源的系统中,进行高性能的时钟或数据分配。与差分LVECL接口时,这些器件工作在-2.375V至-3.8V的电源范围。

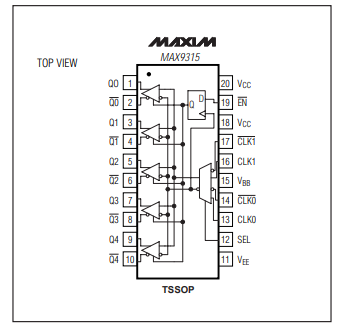

MAX9315提供节省空间的20引脚TSSOP封装。

数据表:*附件:MAX9315 1比5差分LVPECL LVECL HSTL时钟和数据驱动器技术手册.pdf

应用

- 自动测试设备(ATE)

- 局端背板时钟分配

- 数据和时钟驱动器与缓冲器

- DSLAM背板

- 低抖动数据中继器

- 精密时钟分配

- 无线基站

特性

- 工作在差分HSTL/LVPECL下时,电源为+2.375V至+3.8V

- 工作在差分LVECL下时,电源为-2.375V至-3.8V

- 两路可选择的差分输入

- 同步输出使能/禁止

- 20ps输出至输出扭曲

- 360ps传输延迟

- 在1.5GHz下,保证400mV差分输出

- 为单端输入提供片上基准电压

- 输入开路时,输入偏置为低

- 引脚兼容于MC100LVEP14

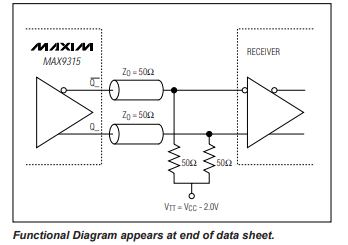

应用电路

引脚配置描述

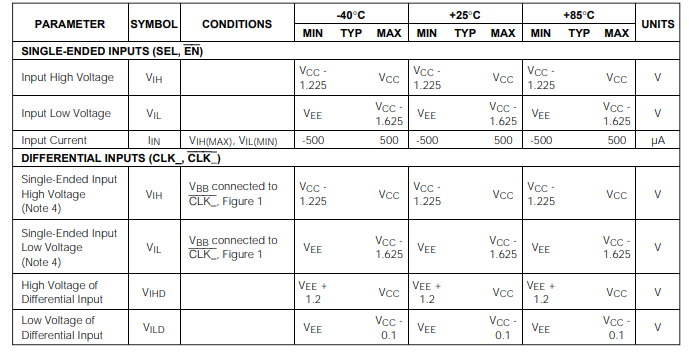

DC电气特性

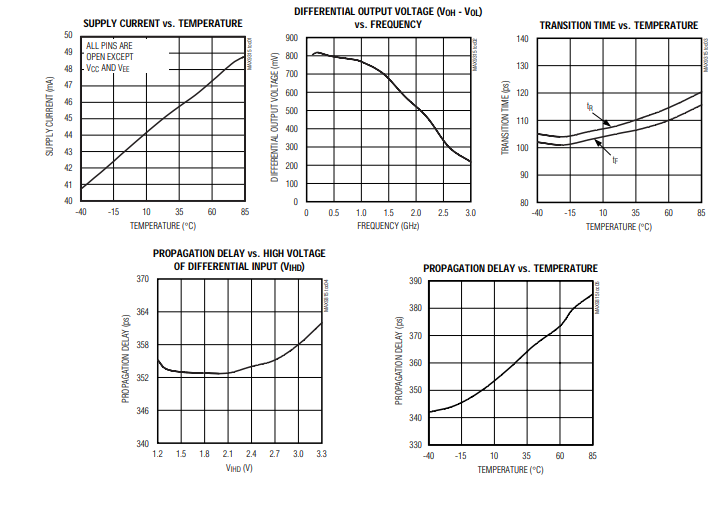

典型操作特性

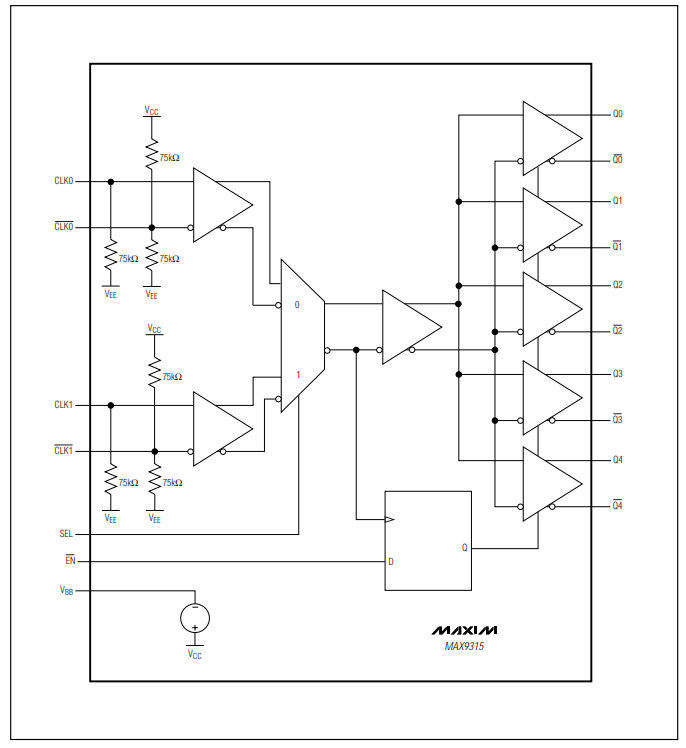

框图

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

探索MAX9315:高性能时钟与数据驱动的理想之选2026-03-26 113

-

深入剖析 CDCLVP215:低电压双差分 1:5 LVPECL 时钟驱动器2026-02-09 253

-

CDCLVP110 1:10 LVPECL/HSTL时钟驱动器技术文档总结2025-09-22 943

-

CDCLVP215 低电压双差分1:5 LVPECL时钟驱动器技术文档总结2025-09-18 814

-

MAX9310 1:5时钟驱动器,可选的LVPECL输入与LVDS输出技术手册2025-05-19 1233

-

MAX9321B差分PECL/ECL/LVPECL/LVECL接收器/驱动器技术手册2025-04-16 1241

-

CDC111差分LVPECL时钟驱动器数据表2024-08-23 455

-

CDCVF111 1:9差分LVPECL时钟驱动器数据表2024-08-21 461

-

MAX9312, MAX9314 双路、1:5差分LVPEC2010-01-26 1589

全部0条评论

快来发表一下你的评论吧 !