MAX9320/MAX9320A 1:2差分LVPECL/LVECL/HSTL时钟和数据驱动器技术手册

描述

概述

MAX9320/MAX9320A是一种低扭曲、1:2差分驱动器设计用于时钟和数据分配,由一路输入再生2路差分输出。差分输入经过调整后,可以允许单端输入,只需外加基准电压即可。

MAX9320/MAX9320A具有超低传输延迟(208ps)、20ps的器件至器件扭曲和6ps的输出至输出扭曲以及最大30mA的电源电流等特性,使其尤其适合于时钟分配。为与差分HSTL和LVPECL信号接口,该器件工作于+2.25V至+3.8V的电源电压,能够实现在+2.5V或+3.3V标称电压系统中,进行高性能的时钟或数据分配。而对于差分LVECL工作方式,该器件工作于-2.25V至-3.8V的电源电压。

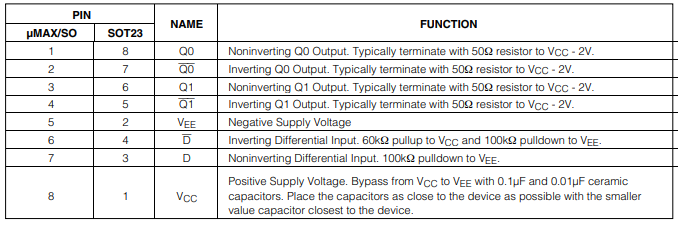

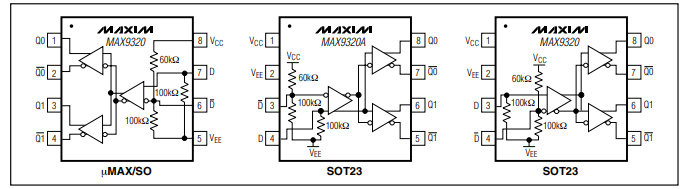

MAX9320和MAX9320A的唯一区别是引脚排列不同。为简化背板与双面电路板任何一面的布线连接,提供有多种引脚排列。

这些器件提供节省空间的8引脚SOT23、µMAX®和SO封装。

数据表:*附件:MAX9320 MAX9320A 1比2差分LVPECL LVECL HSTL时钟和数据驱动器技术手册.pdf

应用

- 低抖动数据中继器

- 精密时钟分配

- 保护开关

特性

- 改进的MC10LVEP11 (MAX9320)代用产品

- +2.25V至+3.8V差分HSTL/LVPECL工作方式

- -2.25V至-3.8V LVECL工作方式

- 22mA (典型)的低电源电流

- 20ps (典型)器件至器件扭曲

- 6ps (典型)输出至输出扭曲

- 208ps (典型)的传输延迟

- 3GHz时最小输出300mV

- 输入开路时,输出为低电平

2kV的ESD保护(人体模型)

- 提供热增强型、底盘裸露的SO封装

引脚配置描述

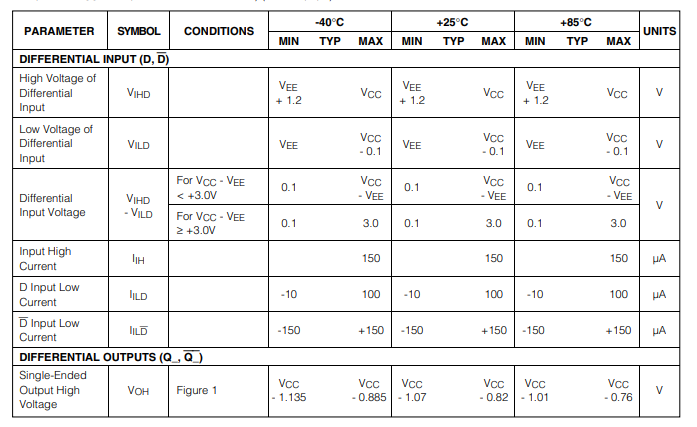

DC电气特性

典型操作特性

详细说明

MAX9320/MAX9320A是低偏斜的1:2差分驱动器,专为时钟和数据分配而设计。为了与差分HSTL和LVPECL信号进行接口,这些器件在+2.25V至+3.8V的电源电压范围内工作,能够在具有标称+2.5V或+3.3V电源的系统中实现高性能的时钟和数据分配。对于差分LVECL工作模式,这些器件的工作电压范围为+2.25V至+3.8V。

从D到D的差分输入的最大幅度为VCC - VEE或3.0V(取较小值)。此限制也适用于任何参考电压输入与单端输入之间的差值。

差分输入具有偏置电阻,当输入开路时,会将输出驱动为差分低电平。反相输入D通过一个60kΩ上拉电阻偏置到Vcc,通过一个100kΩ下拉电阻偏置到VEE。同相输入D通过一个100kΩ下拉电阻偏置到VEE。差分输入电压的高电平和低电平(VHD和VLD)以及差分输入电压(VIH - VIL)需同时满足要求(VLD不能高于VHD)。

输出电平以Vcc为参考,根据Vcc电源的电平,被视为LVPECL或LVECL。当Vcc连接到地且VEE连接到负电源时,输出为LVPECL。当Vcc连接到正电源且VEE连接到地时,输出为LVECL。

以参考电压为中心、幅度约为±100mV的单端输入,或差分输入的幅度至少为±100mV时,可将输出切换到直流电气特性表中规定的VOH和VOL电平。

应用信息

电源去耦

用0.1μF和0.01μF的高频表面贴装陶瓷电容将Vcc旁路到VEE,尽可能将电容靠近器件安装,0.01μF电容最靠近器件。使用多个并联过孔,以最小化电感。

走线

输入和输出走线特性会影响MAX9320/MAX9320A的性能。将差分输入或输出信号连接到50Ω特性阻抗的走线。尽量减少过孔数量,以防止阻抗不连续。通过匹配连接器和电缆保持50Ω特性阻抗,减少反射。通过匹配走线的电气长度,减少差分对内的偏移。

外露焊盘(EP)SO封装可焊接到PC板上,以增强热性能。如果EP未焊接到PC板上,热阻与常规SO封装相同。EP连接到芯片的VEE电源。此外,应确保焊盘不与其他电源接触。有关EP封装的使用指南,请联系美信(Maxim)封装部门。

输出端接

通过50Ω电阻将输出端接到Vcc - 2V,或使用等效的戴维南端接。同时端接两个输出,并使用相同的端接方式,以实现最低的输出间偏斜。当从差分输出获取单端信号时,需同时端接两个输出。例如,如果Q0用作单端输出,则需同时端接Q0和Q0。

-

CDCLVP110 1:10 LVPECL/HSTL时钟驱动器技术文档总结2025-09-22 686

-

MAX9320B 1:2差分PECL/ECL/LVPECL/LVECL时钟和数据驱动器技术手册2025-05-19 685

-

MAX9321差分LVPECL/LVECL/HSTL接收器/驱动器技术手册2025-04-16 853

-

MAX9320ESA+ - (Maxim Integrated) - 时钟/计时 - 时钟缓冲器,驱动器2023-09-08 64

-

MAX9320BEUA+T - (Maxim Integrated) - 时钟/计时 - 时钟缓冲器,驱动器2023-09-07 60

-

MAX9312, MAX9314 双路、1:5差分LVPEC2010-01-26 1501

全部0条评论

快来发表一下你的评论吧 !