UCC27531-Q1 具有 8V UVLO、35V VDD 和分离输出的汽车类 2.5A/5A 单通道栅极驱动器数据手册

描述

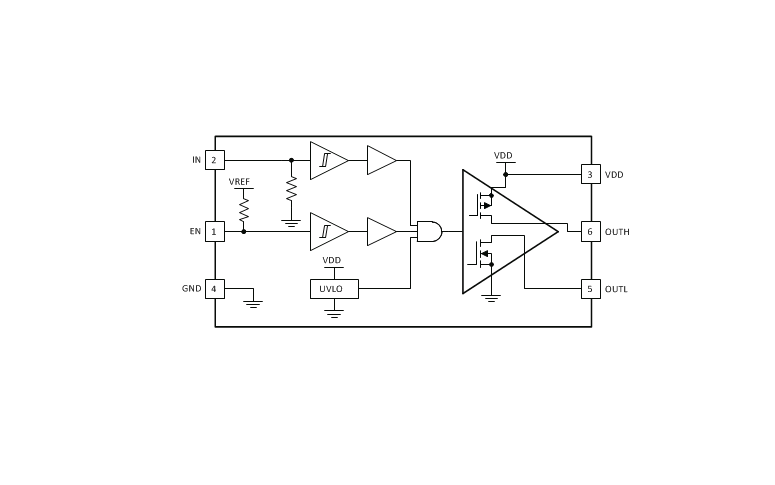

UCC27531-Q1 是一款单通道、高速栅极驱动器,能够有效地 通过使用高达 2.5A 的拉电流和 5A 灌电流(非对称 drive) 峰值电流。非对称驱动中的强大灌电流能力增强了对寄生的抗扰度 Miller 开启效应。UCC27531-Q1 器件还可以具有分离输出配置,其中 栅极驱动电流通过 OUTH 引脚提供,并通过 OUTL 引脚吸收。此引脚 配置允许用户将独立的导通和关断电阻器施加到 OUTH 和 OUTL 引脚,并轻松控制开关转换速率。

*附件:ucc27531-q1.pdf

该驱动器具有轨到轨驱动能力和极小的传播延迟 通常为 17 ns。

UCC27531-Q1 的输入阈值基于 TTL 和 CMOS 兼容的低电压逻辑, 它是固定的,独立于 VDD 电源电压。1V 典型迟滞可提供出色的 抗噪性。

驱动器具有具有固定 TTL 兼容阈值的 EN 引脚。EN 引脚位于内部 拉起;将 EN 引脚拉低可禁用驱动器,而将其保持打开状态可提供正常作。 EN 引脚可用作附加输入,具有与 IN 引脚相同的性能。

将驱动器的 input pin 保持打开状态,使 output 保持低电平。的 driver 显示在 Application Diagram、timing Diagram 和 Input and output logic truth 中 桌子。

VDD 引脚上的内部电路提供 UVLO 功能,将输出保持为低电平,直到 VDD 电源电压在工作范围内。

UCC27531-Q1 驱动器采用 6 引脚标准 SOT-23 (DBV) 封装。设备 可在 –40°C 至 140°C 的宽温度范围内工作。

特性

- 适用于汽车应用

- 符合 AEC-Q100 标准,结果如下:

- 设备温度 1 级

- 器件 HBM ESD 分类等级 H2

- 器件 CDM ESD 分类等级 C4B

- 低成本栅极驱动器(为驱动 FET 和 IGBT 提供最佳解决方案

) - 分立晶体管对

驱动的绝佳替代品(提供与控制器的轻松接口) - TTL 和 CMOS 兼容输入逻辑

阈值(与电源电压无关) - 分离式输出选项允许调谐导通

和关断电流 - 使用固定 TTL 兼容阈值启用

- 在 18V VDD 时,具有 2.5A 的高拉电流峰值和 5A 灌电流峰值驱动

电流 - 10 V 至 35 V 的宽 VDD 范围

- 输入和使能引脚能够承受高达

地以下 –5V DC 的电压 - 当输入悬空或在

VDD UVLO 期间,输出保持低电平 - 快速传播延迟(典型值为 17ns)

- 快速上升和下降时间

(1800pF 负载时,典型值为 15ns 和 7ns) - 欠压锁定 (UVLO)

- 用作高侧或低侧驱动器(如果

设计具有适当的偏置和信号隔离) - 低成本、节省空间的 6 引脚 DBV (SOT-23)

封装选项 - 工作温度范围为 –40°C 至 140°C

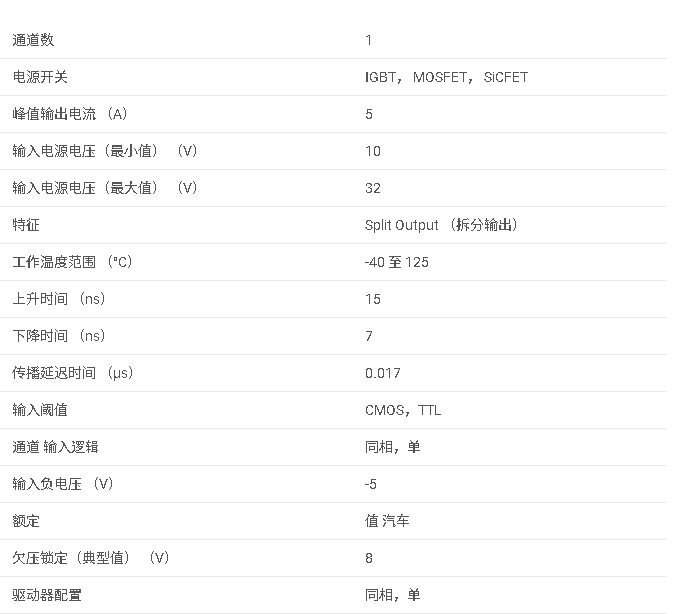

参数

方框图

1. 产品概述

- 型号:UCC-Q1

- 类型:.-A和-A,5-V MAX VDD FET和IGBT单栅极驱动器

- 特点:

- 适用于汽车应用,符合AEC-Q标准

- TTL和CMOS兼容输入逻辑阈值,独立于电源电压

- 提供高达2.5-A源电流和5-A漏电流(非对称驱动)

- 宽VDD范围:V至V

- 输入和使能引脚可承受低至-V DC的电压

- 输出在输入浮动时保持低电平

- 快速传播延迟(典型值ns)

- 欠压锁定(UVLO)功能

- 可作为高侧或低侧驱动器(需适当偏置和信号隔离)

- 低成本、节省空间的引脚DBV(SOT-3)封装

2. 应用领域

- 汽车

- 开关电源

- DC-DC转换器

- 太阳能逆变器

- 电机控制

- UPS

- HEV和EV充电器

- 家用电器

- 可再生能源电力转换

- SiC FET转换器

3. 电气特性

- UVLO:

- VDD启动阈值:约.V

- 滞后电压:约.V

- 输入特性:

- 高电平输入阈值(VIN_H):.V至2.2V

- 低电平输入阈值(VIN_L):.V至1.2V

- 输入滞回:1V

- 使能特性:

- 使能高电平阈值(VEN_H):1.7V至.V

- 使能低电平阈值(VEN_L):0.8V至.V

- 使能滞回:.V

- 输出特性:

- 源峰值电流(ISRC):.A

- 漏峰值电流(ISNK):5A

- 输出高电平电压(VOH):接近VDD

- 输出低电平电压(VOL):约0.5V至.V

4. 功能描述

- VDD UVLO:在VDD电压低于UVLO阈值时,输出保持低电平。

- 输入阶段:基于TTL和CMOS兼容的低电压逻辑,具有宽滞回以增强噪声免疫力。

- 使能功能:EN引脚具有固定的TTL兼容阈值,内部上拉。拉低EN引脚可禁用驱动器。

- 输出阶段:具有独特的输出结构,可在Miller平台期间提供高峰值源电流,增强对寄生Miller开通效应的免疫力。

5. 设备功能模式

- 正常模式:输出状态取决于输入和使能引脚的状态。

- UVLO模式:当VDD电压低于UVLO阈值时,输出保持低电平。

6. 应用与实现

- 设计考虑:包括输入输出配置、输入阈值类型、VDD偏置电压、峰值源漏电流、使能功能、传播延迟和功率耗散等。

- 典型应用:包括驱动IGBT(无负偏置)、驱动IGBT(带3V负关断偏置)以及在逆变器中使用UCC1-Q驱动器。

7. 电源推荐

- 建议VDD使用1µF的旁路电容,以改善噪声滤波。

8. 布局

- 布局指南:建议将驱动器尽可能靠近功率器件放置,以最小化高电流迹线的长度,并使用宽迹线和平行信号与返回迹线。

- 热考虑:提供了热阻等热度量标准,以帮助评估散热性能。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

UCC27531-Q1:高性能单通道栅极驱动器的设计秘籍2026-01-09 458

-

汽车应用利器:UCC27624V-Q1低侧栅极驱动器深度剖析2026-01-06 365

-

UCC27532-Q1 具有 8V UVLO、35V VDD 和 CMOS 输入的汽车类 2.5A/5A 单通道栅极驱动器数据手册2025-05-20 783

-

UCC27524A1-Q1 具有 5V UVLO 和负输入电压处理能力的汽车类 5A/5A 双通道栅极驱动器数据手册2025-05-19 908

-

UCC5350-Q1 汽车类 ±5A 单通道隔离式栅极驱动器数据手册2025-05-17 1492

-

具有8V UVLO、跨导保护和使能端的汽车类120V、3.7A/4.5A 半桥驱动器UCC27301A-Q1数据表2024-03-28 454

-

具有UVLO的5A、5A光耦兼容单通道功能隔离式栅极驱动器UCC23113数据表2024-03-22 574

-

UCC27531-Q1 UCC27531-Q1 2.5A、5A、35VMAX VDD FET 和 IGBT 单门驱动器2018-10-16 486

全部0条评论

快来发表一下你的评论吧 !