MAX9263/MAX9264 HDCP千兆位多媒体串行链路串行器/解串器技术手册

描述

概述

MAX9263/MAX9264芯片组将Maxim的吉比特多媒体串行链路(GMSL)技术扩展到支持宽带数字内容保护(HDCP)加密,用于DVD和Blu-ray™视频及音频数据保护。MAX9263串行器或任何HDCP-GMSL串行器,配合MAX9264解串器或任何HDCP-GMSL解串器,构成数字串行链路,用于传输控制数据和HDCP加密视频、音频数据。GMSL是经过Digital Content Protection (DCP),LLC认证的HDCP技术。

数据表:*附件:MAX9263 MAX9264 HDCP千兆位多媒体串行链路串行器 解串器中文手册.pdf

并行接口可针对24位或32位字节宽度编程,工作在8.33MHz至104MHz (24位)或6.25MHz至78MHz (32位)像素时钟。针对24位或32位字节编程时,3路输入用于I²S音频,支持8kHz至192kHz采样率、4位至32位采样深度。嵌入式控制通道在串行器和解串器之间形成9.6kbps至1Mbps全双工差分UART链路。电子控制单元(ECU)或微控制器(µC)可位于链路的串行器侧(通常用于视频显示)、链路的解串器侧(通常用于图像检测),或两侧(通常用于HDCP视频显示中继器)。控制通道使能远端外设的ECU/µC控制,例如背光控制、触摸屏,并执行HDCP相关的操作。

串行链路信号为交流耦合CML,8b/10b编码。为了驱动更长电缆,串行器提供可编程预加重/去加重,解串器提供可编程通道均衡器。GMSL器件在串行(串行器)和并行(解串器)输出具有可编程扩频功能。串行链路输入和输出满足ISO 10605和IEC 61000-4-2 ESD标准。串行器主电源电压为1.8V;解串器主电源电压为3.3V;I/O电源为1.8V至3.3V。两款器件均采用64引脚、TQFP封装,带裸焊盘,工作在-40°C至+105°C汽车级温度范围。

应用

- 高分辨率汽车导航

- 兆像素照相系统

- 后排座信息终端

特性

- 通过控制通道可设置HDCP加密使能/禁用

- 控制信号处理所有HDCP协议—无需独立的控制总线

- HDCP密钥预先设置在非易失安全存储器

- 2.5Gbps净荷数据率(额定3.125Gbps)

- 交流耦合串行链路,带有8b/10b行编码

- 8.33MHz至104MHz (24位模式)或6.25MHz至78MHz (32位模式)像素时钟

- 4位至32位字长,8kHz至192kHz I²S音频通道支持高清音频

- 内置半/全双工双向控制通道

- 基本模式:9.6kbps至1Mbps

- 旁路模式:9.6kbps至1Mbps

- 中断支持触摸显示屏

- 远端I²C主机控制外设

- 可编程预加重/去加重和通道均衡器,可驱动3.125Gbps数据沿电缆传输15m

- 串行或并行输出提供可编程扩频功能,降低EMI

- 解串器提供串行数据时钟恢复,无需外部参考时钟

- 自动数据率检测,允许“实时”改变数据率

- 串行器像素时钟输入可旁路PLL,用于衰减抖动

- 内置PRBS发生器/检测器,用于串行链路的BER测试

- 可检测串行链路对地、对电池短路以及开路故障。

- ISO 10605和IEC 61000-4-2 ESD保护

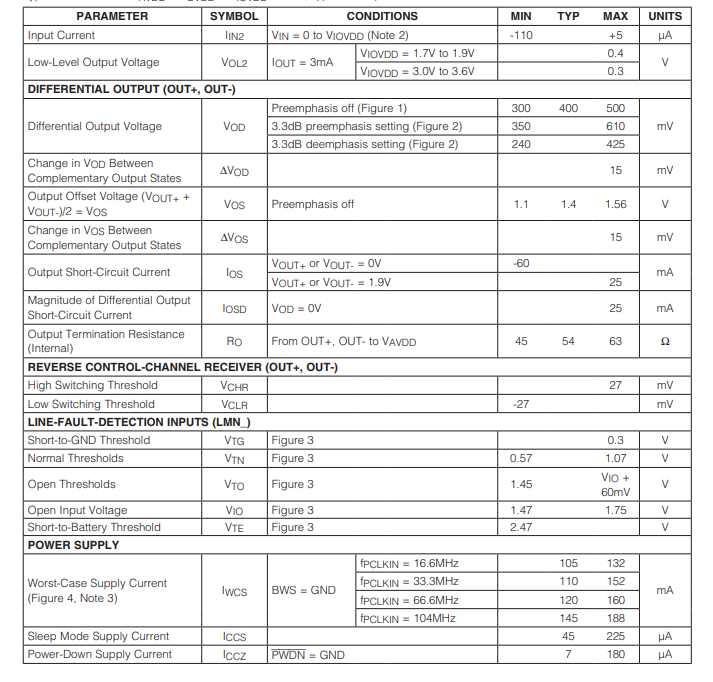

MAX9263 DC电气特性

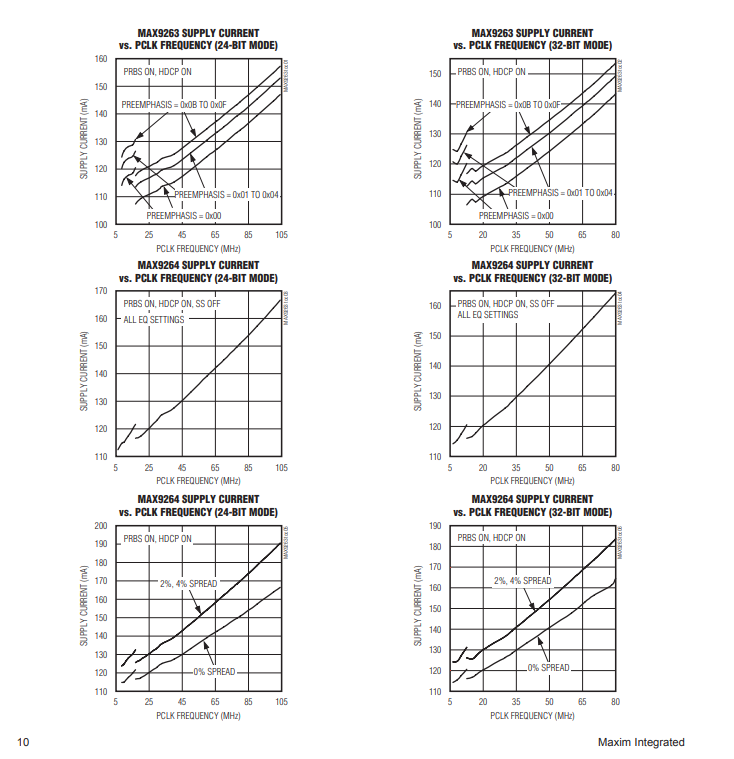

典型操作特性

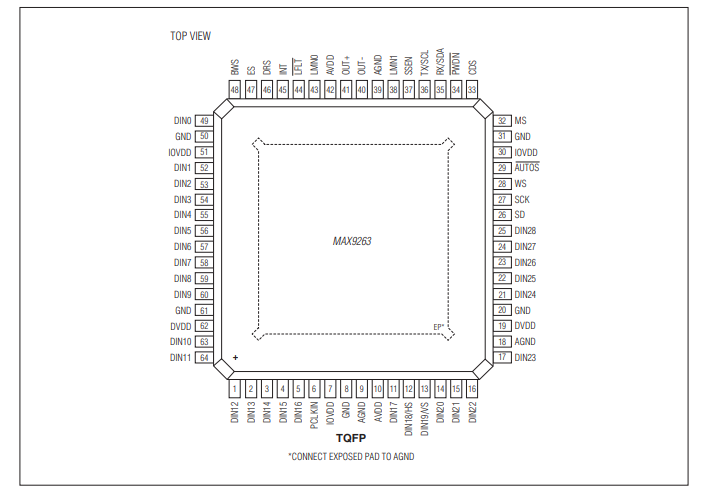

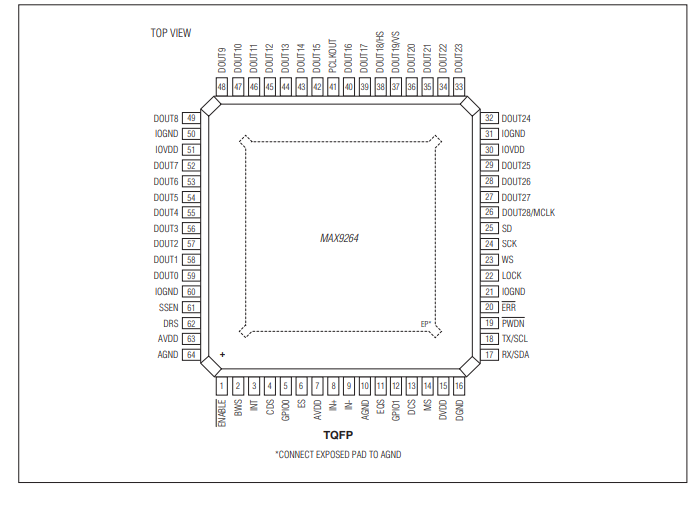

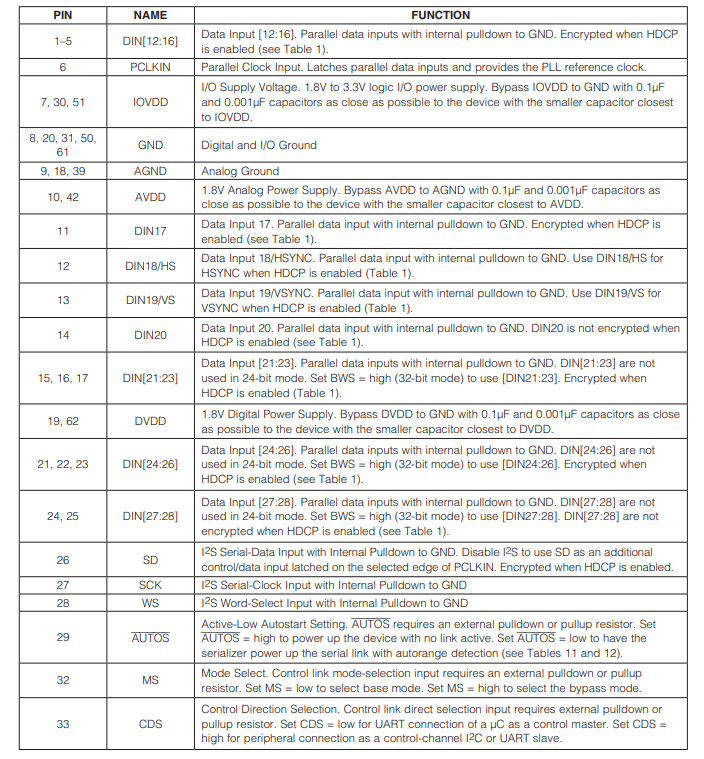

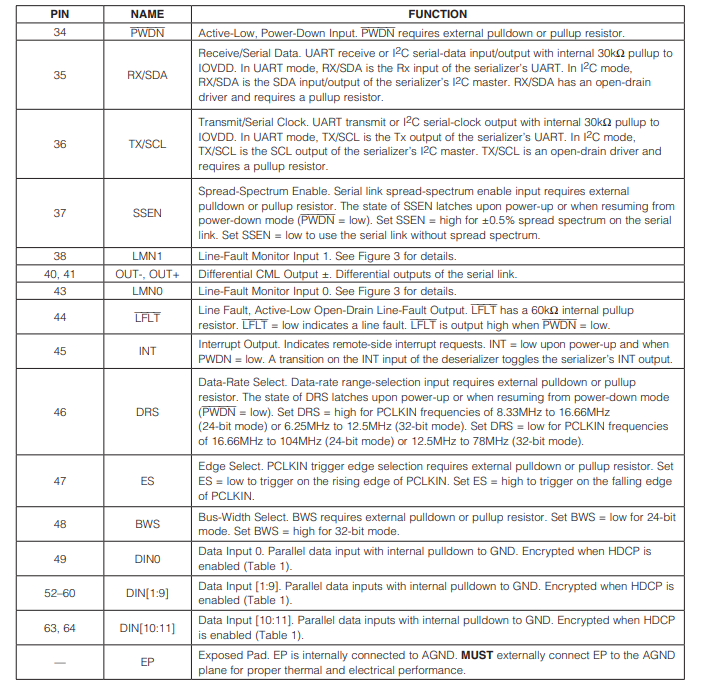

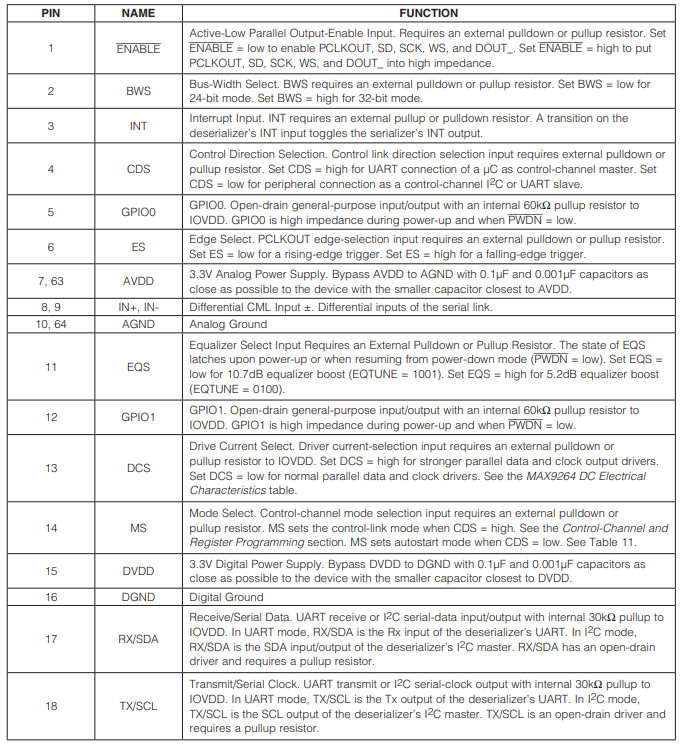

引脚配置描述

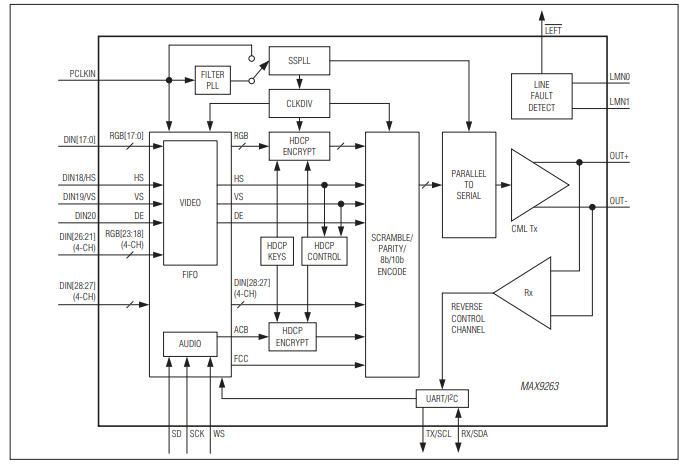

框图

应用信息

错误检查

解串器会检查串行链路是否存在错误,并将检测到的解码错误数量存储在8位寄存器DECERR(0x0D)中。如果在短时间内(错误率大于1/4)检测到大量8b/10b解码(或奇偶性)错误,解串器会失去锁定并停止错误计数。然后,解串器会尝试重新锁定串行数据。成功锁定后,DECERR会重置;通过UART成功读取DECERR时,或者启用自动错误重置功能时,DECERR也会重置。解串器在解码或测试期间不检查奇偶性错误,DECERR会重置为0x00。

解串器有一个漏极开路的ERR输出。在正常运行期间,当解码错误数量超过错误阈值ERRTHR(0x0C)时,或者至少检测到1个PRBS错误时,该输出会置为低电平。ERR在DECERR读取、视频链路锁定或自动错误重置时重新置为高电平。

自动错误重置

重置错误的默认方法是读取解串器中相应的错误寄存器(0x0D、0x0E)。自动错误重置会清除解码错误计数器DECERR,并且ERR输出在~1μs后变为低电平。自动错误重置通过AUTORESET(0x06、D6)进行禁用。启用自动错误重置后,在设备处于PRBS测试模式时,自动错误重置不会运行。

PRBS自测试

串行器/解串器链路包含一个PRBS模式生成器和误码率验证功能。首先,在解串器中禁用毛刺滤波器(设置DISVSFILT、DISHSFILT = 1)。接下来,在解串器中禁用VSYNC/HSYNC反相(设置INVVSYNC、INVHSYNC = 0)。然后,设置PRBSEN = 1(0x04、D5)在串行器中启用。然后,解串器通过将PRBSEN = 0(0x04、D5)设置为0来启动PRBS测试。然后,串行器通过将PRBSEN = 0设置为0来退出PRBS自测试。解串器使用一个8位寄存器(0x0E)来对检测到的错误进行计数。控制链接还控制错误计数的开始和停止。在PRBS模式下,设备的错误输出不反映串行器和解串器的ERR输出结果,而是反映PRBS错误。

高速串行链路两端的微控制器(双微控制器控制)

通常,微控制器位于串行器端或解串器端,用于视频显示应用或图像传感应用。对于前者,串行器的两个CDS引脚都设置为低电平;对于后者,CDS引脚都设置为高电平。但是,如果串行器和解串器的CDS引脚都为高电平,则串行器/解串器连接到两个微控制器。在这种情况下,任一微控制器都可以与串行器或解串器通信。

如果两端的微控制器同时使用控制链路,可能会发生争用。串行器/解串器不提供避免争用的机制。串行器/解串器在通信失败时会发送确认帧。用户可以实施更高层协议来避免争用。此外,串行链路上的微控制器通信需要UART。在不需要时,微控制器可以通过FWDDCEN和REVDDCEN位(0x04、D1:0)在串行器/解串器中禁用正向和反向控制通道。UART通信通过串行链路停止。

在双微控制器操作期间,只要任一微控制器的CDS引脚状态发生变化,就不再会出现微控制器之间的争用。如果链路恢复,相应状态将如“链路启动过程”部分所述。

例如,双微控制器可用于图像传感应用,一个微控制器处于睡眠模式并等待唤醒,解串器处于唤醒状态。唤醒引脚拉高后,串行器设置串行器的CDS引脚为低电平,并假定为主机控制串行器的寄存器。

HSYNC/VSYNC毛刺滤波器

解串器在HSYNC和VSYNC上包含单周期毛刺滤波器。这消除了HSYNC和VSYNC中的单周期毛刺,这些毛刺可能会导致HDCP串行器和解串器之间的同步丢失,同时启用加密功能。默认情况下,毛刺滤波器通过将解串器中寄存器0x08的D[1:0]位写入来禁用HSYNC或VSYNC中的毛刺滤波器。

毛刺滤波器启用时,会抑制所有单周期宽脉冲信号。在运行PRBS误码率测试之前禁用毛刺滤波器。内部误码率检查器假定输入比特流为未改变的PRBS数据。

-

MAX9266 HDCP多媒体串行链路解串器,带有LVDS系统接口技术手册2025-05-28 1596

-

MX9259和MAX9260千兆多媒体LVDS视频传输串行链路的详细资料免费下载2018-08-24 2232

-

供应MAX9286吉比特多媒体串行链路(GMSL)解串器接收多达四个GMSL串行器的数据2018-02-02 5151

-

Maxim推出高速LVDS串行器/解串器MAX9259/MAX9260/MAX92652014-12-06 5970

-

Maxim推出高速LVDS串行器/解串器MAX9263/MAX9265/MAX92642011-04-14 4608

-

MAX9266 HDCP吉比特串行链路解串器2011-04-11 2289

-

MAX9265吉比特多媒体串行链路串行器2011-01-19 1547

-

MAX9259, MAX9260 吉比特多媒体串行链路,提供2010-06-26 1879

-

MAX9249 吉比特多媒体串行链路串行器,具有LVDS系统2010-03-28 1402

全部0条评论

快来发表一下你的评论吧 !