通过交互式对称性校验提升集成电路设计流程

制造/封装

描述

在高性能集成电路 (IC) 设计领域,对称性不仅仅是一种美学偏好,同时也是确保器件正常运行的关键因素。尤其是在模拟和射频 (RF) 设计中,对称性设计有助于电性保持一致。然而,在 IC 设计中确保对称性并非易事。在本文中,我们将探讨对称性检查的重要性、它所带来的挑战,以及如何将对称性检查提前到设计流程中,以增强验证效率,确保设计实现预期功能。

高性能 IC 中对称性的重要性

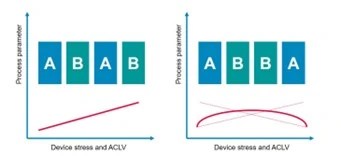

IC 设计中的对称性指的是电路元件在几何形状、电气特性等方面达到一种平衡状态。在差分对中绘制的相同 MOSFET 必须在整个布局生命周期中保持基本相同,以维持相同的电气性能(图 1)。

图 1. 器件参数匹配减少了应力和芯片长度变化 (ACLV) 的影响。

(图片来源:西门子)

这一概念在需要严格精度的电路中尤为重要,例如数据转换器、运算放大器和锁相环 (PLL)。对称结构可最小化由制造缺陷或工艺变化引起的偏差,而这些偏差可能对性能造成很大影响。任何微小的不匹配都可能导致信号失真、噪声或定时错误,从而影响 IC 的整体功能。

例如,在差分电路中,保持正负分支之间的对称性可确保在两个分支中共有的噪声相互抵消,只剩下所需的信号。同样,在 RF 电路中,对称布局有助于防止寄生元件对信号完整性产生负面影响。

为了应对这些挑战,自动对称性检查工具需要不断进化,更细致地控制对称性约束条件,并支持先进工艺技术。这些工具可以处理复杂几何形状和多层设计,确保即使在最先进的 IC 中也能保持对称性。

先进节点对称性检查的挑战

随着 IC 设计转向更小的工艺节点,布局的复杂性和高性能设计所需的更严格公差,带来了更困难的对称性检查挑战。在先进节点中,即使轻微的不对称也可能导致显著的性能下降。

此外,先进封装技术(如 2.5D 和 3D IC)的广泛应用为对称性检查增加了更多复杂性。在这些设计中,跨越多个芯片或堆叠层保持对称性对于确保信号完整性和最小化组件之间的串扰至关重要。

传统对称性检查方法

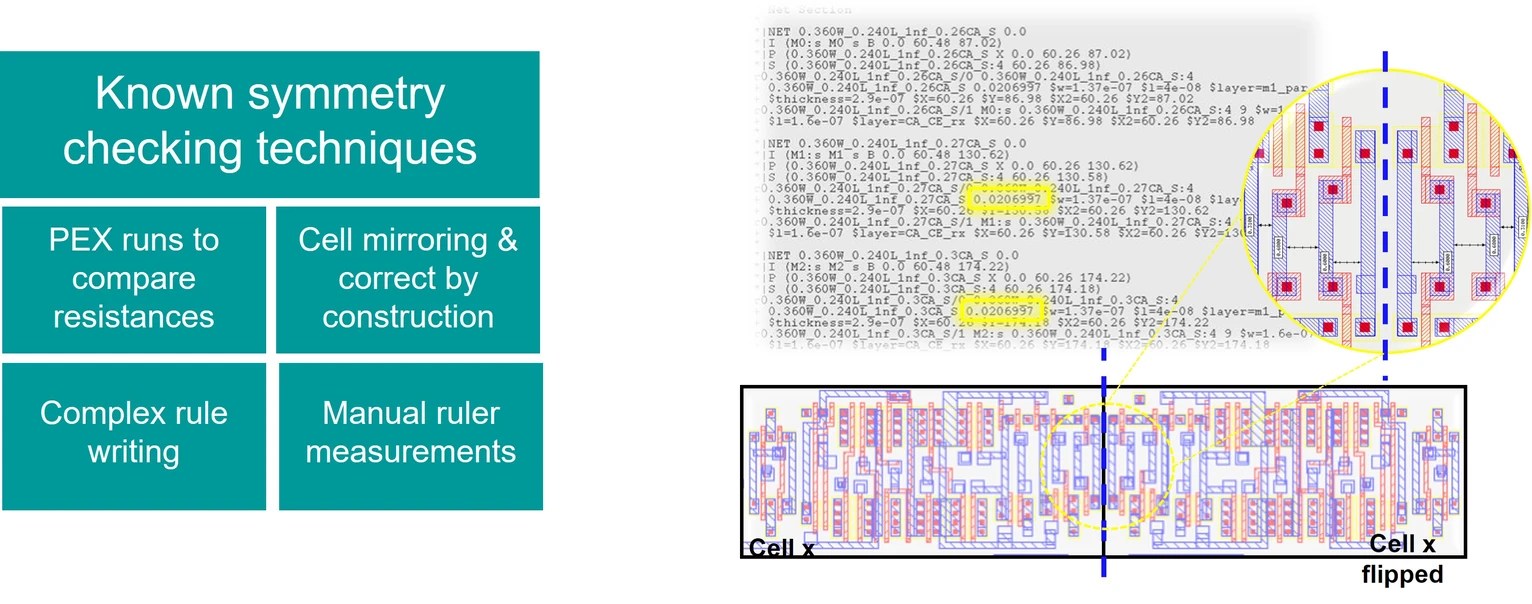

遗憾的是,传统的对称性验证方法往往存在漏洞,导致错误可能直到设计后期才会被发现,甚至是在制造之后才发现。

早期设计人员采用了几种方法来验证对称性,但每种方法都有其自身的局限性,如图 2 所示。

图 2. 传统对称性验证技术。

(来源:西门子)

手动尺规测量: 这是一种耗时且容易出错的方法,结果的质量完全取决于设计人员的细致程度。

编写复杂规则: 这种方法可以产生准确的结果,但需要大量的专业知识和时间来编写和维护对称性验证规则。

单元镜像: 设计人员基于构造对称性假设正确性。然而,在物理设计过程中,与放置相关的偏移可能会破坏对称性。

寄生参数提取: 通过在寄生参数提取过程中匹配电阻值,设计人员推断对称性。然而,提取工具内的近似可能将会导致对实际对称性的不准确假设。

这些方法各有局限,更重要的是,依赖这些方法通常意味着设计人员只能在设计过程的后期甚至是流片后才发现问题,导致成本高昂的设计更改。

将对称性检查提前到设计流程中

近年来,“左移”验证的概念在半导体行业大行其道。通过将验证任务提前到设计流程的早期阶段,设计人员可以在设计之初提前发现问题,而对称性检查就是这种方法论的理想实践之一。

从早期阶段到 signoff 的过程中进行持续验证,能够获得诸多益处:

及早发现违规问题:通过将对称性检查左移,设计人员可以在构建布局的过程中发现对称性违规。这使得调试速度更快,并有效减少设计迭代次数。

提高准确性:早期对称性检查能够确保在设计过程中持续保持对称性,进而在最终产品中实现更高的准确性和更好的性能。

提高效率:自动化对称性检查减少了手动检查的需求,使设计人员能够专注于更复杂的任务。自动化还能最小化人为错误的风险,确保更一致的结果和更快的验证周期。

这些益处叠加可以减少迭代次数、加速流片时间,并确保设计满足市场需求。

在设计环境中自动化对称性检查

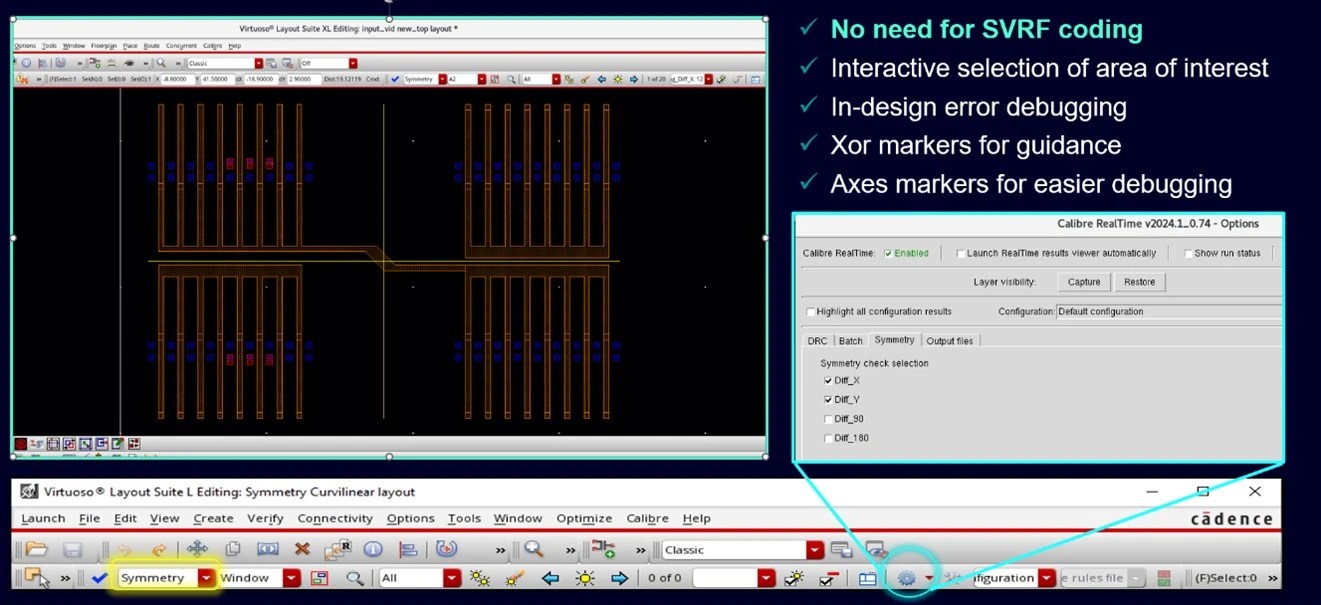

自动对称性检查解决方案使设计人员能够直接在布局中设置对称性约束,这些约束会随着设计的推进自动进行验证。实时标记违规,并即刻进行更正。自动化还使设计人员能够为设计的不同部分定义自定义对称性规则,确保布局符合每个模块的具体要求。图 3 展示了通过 Calibre RealTime 平台实现的 Calibre 交互式对称性检查,用户可以通过设计布局访问该平台。

图 3: Calibre 交互式对称性检查解决方案完全自动化,并可通过 Calibre RealTime 集成到设计环境中。

(来源:西门子)

结论

对称性对于实现高性能 IC 至关重要。通过将对称性检查左移到设计流程中,设计人员可以及早发现违规,简化验证过程,并降低成本高昂的设计迭代风险。在设计环境中能够直接访问的自动化交互式对称性检查解决方案正在促成这一转变,实现更快、更准确的 IC 设计对称结构验证,进而帮助团队设计高性能 IC,以满足当今半导体行业所要求的严格性能和可靠性标准。

- 相关推荐

- 热点推荐

- 集成电路

-

专用集成电路设计流程是什么 专用集成电路的特点有哪些2024-05-04 3071

-

如何证明波导正规模的电场磁场具有时间对称性和反对称性?2023-10-19 1651

-

国产EDA“夹缝”生存 集成电路设计和制造流程2023-09-28 3618

-

利用对称性化简求解对称电路2023-03-09 7448

-

物质和反物质不对称性与CP对称性破缺2022-10-25 3671

-

对称性对傅里叶系数的影响2022-06-21 3175

-

对称性加密算法2021-07-19 1688

-

对称性对傅立叶系数的影响有哪些2019-09-01 7364

-

芯片设计中数模混合集成电路的设计流程是怎么样的2019-08-17 18800

-

鳍式场效晶体管集成电路设计与测试2018-05-25 6227

-

机械结构对称性实例设计2018-03-10 1295

-

集成电路设计流程详解2011-10-28 24334

-

晶体对称性分析2010-08-26 840

-

基于几何对称性的颅骨复原技术2009-04-14 683

全部0条评论

快来发表一下你的评论吧 !