TPIC46L02 1.2mA/1.2mA 6 通道栅极驱动器,在短路负载、开路负载、过击压下具有低占空比 PWM数据手册

描述

TPIC46L01、TPIC46L02 和 TPIC46L03 是低侧预驱动器,提供串行输入接口和 并行输入接口,用于控制 6 个外部场效应晶体管 (FET) 电源开关,如 Texas Instruments TPIC 系列电源阵列。这些器件主要为低频 开关、电感负载应用,如螺线管和继电器。每个通道的故障状态都可用 采用串行数据格式。每个驱动器通道具有独立的关断状态、开路负载检测和导通状态 负载短路/电池短路检测。电池过压和欠压检测和关断 提供。电池和输出负载故障向控制器提供实时故障报告。每个通道还 为外部 FET 提供感应电压瞬态保护。

*附件:tpic46l02.pdf

这些器件通过串行输入接口或并行输入接口提供对输出通道的控制。 启用任一接口输出的命令将启用相应的通道 GATE 输出到 外部 FET。当控制设备之间的信号数量 并且必须最小化预驱动器,并且运行速度并不重要。在 Predriver 必须非常快速或异步响应,建议使用 Parallel Input 接口。

对于串行作,控制器件必须将 CS 从高电平转换为低电平,以激活串行输入接口。 发生这种情况时,SDO 使能,故障数据被锁存到串行输入接口中,FLT 标志为 刷新。

数据通过 SDI 在 SCLK 的低到高转换中同步进入串行寄存器。每个数据字符串必须 由 8 位数据组成。在多个设备级联在一起的应用程序中,数据字符串必须 每个设备由 8 位组成。高数据位打开相应的输出通道,低数据位转动 它关闭。当串行输入数据被同步输入到器件中时,该器件的故障数据从 SDO 中同步输出。故障数据 由电池过电压(位 8)、电池不足电压(位 7)(不在 TPIC46L03)和 shorted/open-load flags (位 1-6) 用于 6 个 output 通道中的每一个。故障数据中的逻辑高位表示 一个 FAULT 和一个 LOGIC-LOW 位表示该通道上不存在 FAULT。设置或清除故障寄存器位 异步地反映硬件的当前状态。当 CS 转换时,必须存在故障 从高到低,在串行故障数据中捕获和报告。无法在序列中捕获新故障 当 CS 为低电平时注册。在所有串行数据都已 clocking到器件之后,CS 必须转换为高电平。 CS 的低到高转换将串行数据的最后 6 位传输到输出缓冲区,将 SDO 置于 high-impedance 状态,并清除并重新启用 fault register。TPIC46L01/L02/L03 旨在 允许多个设备的串行输入接口级联在一起,以简化串行接口到 控制器。串行输入数据流经器件,并跟随 SDO 传入的故障数据传出 SDO 级联配置。

对于并行作,数据直接从并行输入接口 (IN0-IN5) 异步传输到 相应的 GATE 输出。并行控制不需要 SCLK 或 CS。并行输入上的 1 会打开 相应的 channel on,其中 0 将其关闭。请注意,串行接口或并行接口都可以 启用频道。在并联作下,故障数据仍必须通过串行数据接口收集。

预驱动器监控每个通道的漏极电压,以检测负载短路或负载开路故障情况 分别处于 on 和 off 状态。这些器件提供了使用内部生成的 故障参考电压或外部提供的 VCOMP 用于故障检测。内部故障参考为 通过将 VCOMPEN 连接到 GND 来选择,并且通过连接 VCOMPEN 来选择外部基准 到 V 抄送 .当通道导通时,将漏极电压与故障参考电压进行比较,以检测 短路负载情况以及当通道关闭时检测开路负载情况。当负载短路故障时 使用 TPIC46L01 或 TPIC46L03 发生,通道关闭,故障信号也被发送到 FLT 至于 serial fault-register 位。当使用 TPIC46L02 时发生负载短路故障时,通道 只要存在故障,就会转换为低占空比、脉宽调制 (PWM) 信号。 短路负载条件必须至少在短路负载抗尖刺时间 t 内存在 (STBDG) ,以便 标记为故障。故障信号以及串行故障寄存器位被发送到 FLT。有关故障检测的更多详细信息 作在本数据资料的 Device Operation 部分介绍。

TPIC46L01 和 TPIC46L02 提供电池过电压和电池不足电压保护 条件,与 output channels 的状态无关。TPIC46L03 提供电池过载保护 电压条件与输出通道的状态无关当电池电压大于 过压阈值或小于欠压阈值(TPIC46L03 除外,它没有 欠压阈值),所有通道都被禁用,故障信号被发送到 FLT 以及相应的 故障寄存器位。一旦电池电压故障得到纠正,输出将恢复正常工作。 当出现电池过压/电池不足电压情况时,设备会报告电池故障,但会禁用 开路和短路负载情况的故障报告。开路和短路负载情况的故障报告为 在纠正 Battery Fault 情况后重新启用。

这些器件在所有通道上提供感应瞬态保护。漏极电压被箝位以保护 FET。该箝位电压由 V 之和定义抄送以及外部 FET 的导通电压。预驱动因素 还提供栅源电压 (V GS系列 ) clamp 保护功率 FET 的 GATE 源极端子免受 超过其额定电压。

这些器件在除 CS 之外的所有输入上提供下拉电阻。CS 上使用了上拉电阻。

特性

- 6 通道 Serial-In/Parallel-In 低侧 Pre-FET 驱动器

- 设备可以级联

- 内部 55V 电感负载钳位和 V

GS系列用于外部功率 FET 的保护夹 - 在所有漏极端子上提供独立的负载短路/电池短路故障检测

- 独立的关断状态开路负载故障检测

- 电池过压锁定保护和故障报告

- 用于 TPIC46L01 和 TPIC46L02 的电池欠压锁定保护

- 异步漏极开路故障标志

- 器件输出可与多个外部器件进行有线或运算

- 通过串行输出端子返回故障状态

- 器件内部全局上电复位

- 具有迟滞的高阻抗 CMOS 兼容输入

- TPIC46L01 和 TPIC46L03 在发生负载短路故障时禁用栅极输出

- TPIC46L02 当发生负载短路故障时,将栅极输出转换为低占空比 PWM 模式

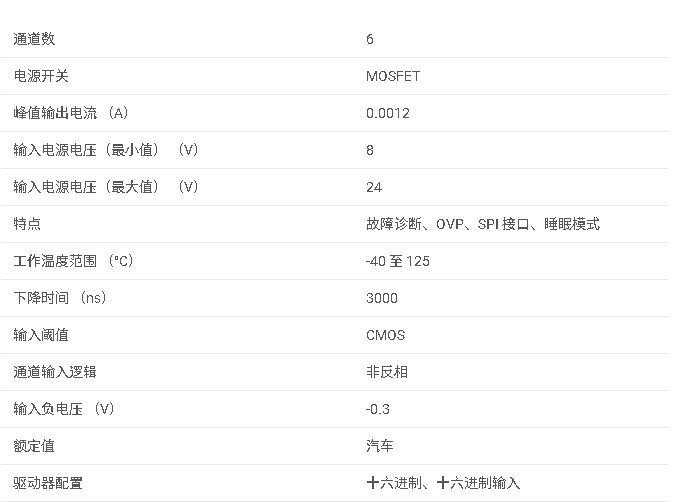

参数

一、产品概述

- 产品名称: TPIC6L

- 类型: 通道串行/并行低侧预驱动器

- 特点:

- 个独立的低侧预驱动通道

- 串行和并行输入接口

- 电池过压和欠压保护

- 短路负载/短路到电池故障检测

- 开路负载故障检测

- 电感负载保护和VGS保护钳位

二、功能特性

- 控制接口:

- 串行接口(通过SCLK、CS、SDI、SDO)

- 并行接口(通过IN0-IN)

- 故障检测与报告:

- 过压、欠压、短路负载、开路负载故障检测

- 故障状态通过串行输出返回

- 实时故障标志输出(FLT)

- 保护特性:

- 5V电感负载钳位

- VGS保护钳位

- 短路负载故障时,输出进入低占空比PWM模式

三、封装与引脚

- 封装类型: SSOP(DB)

- 引脚数量:

- 主要引脚功能:

- CS: 芯片选择,低电平有效

- SDI: 串行数据输入

- SCLK: 串行时钟

- SDO: 串行数据输出

- FLT: 故障标志输出,开漏

- GATE0-GATE: 6个栅极驱动输出

- DRAIN0-DRAIN: 6个漏极输入,用于故障检测

- VCC: 逻辑电源电压

- VBAT: 电池电源电压

- GND: 地

四、电气特性

- 供电电压:

- VCC: 4.5V至.V

- VBAT: 8V至4V(正常操作),最高0V

- 输出特性:

- 栅极驱动电压范围: 取决于VBAT

- 最大输出电流(推拉): .mA至2.5mA

- 故障检测电压:

- 短路/开路负载检测电压: .V至1.4V(典型)

- 过压/欠压阈值:

- 过压关断阈值: 2V至6V

- 欠压关断阈值(TPIC6L/L): 4.1V至.V

五、操作原理

- 串行数据操作:

- 通过CS激活串行接口,数据在SCLK的上升沿通过SDI移入,在下降沿从SDO移出。

- 故障数据在CS的下降沿锁存到串行寄存器。

- 并行数据操作:

- 数据直接从并行输入(IN0-IN)异步传输到相应的GATE输出。

- 故障处理:

- 检测到短路负载故障时,TPIC6L将输出转换为低占空比PWM信号,以保护FET免受过热。

- 过压或欠压时,所有通道被禁用,并发送故障信号。

六、应用信息

- 典型应用:

- 适用于低频开关应用,如电磁阀、继电器等电感负载。

- 布局建议:

- 建议将驱动器靠近FET的栅极放置,以减少振荡。

- 对于长输出路径,建议在栅极附近串联一个小电阻。

七、封装与材料信息

- 提供了多种封装选项,包括TPICL2DBR、TPICL2DBRG等。

- 提供了详细的封装尺寸、磁带和卷盘信息。

-

DRV8860 38-V 8通道串行接口低侧驱动器技术文档总结2025-10-17 922

-

TPIC46L01 1.2mA/1.2mA 6 通道栅极驱动器数据手册2025-05-22 781

-

6通道串行和并行低端前置FET驱动器TPIC46L01、TPIC46LO2和TPIC46LO3数据表2024-03-19 417

-

为200mA负载电流实现6W汽车LED驱动器参考设计2022-09-22 1207

-

如何为200mA负载电流实现6W汽车LED驱动器2022-09-08 579

-

TPIC44L02 4 通道串联/并联低侧前置 FET 驱动器2019-01-08 260

-

为继电器、LED、步进电机提供 16 通道低侧驱动器的参考设计资料下载2018-07-24 2578

-

串行接口双路 8 通道中继、LED、步进驱动器2015-04-13 2092

-

TPIC46L01,pdf (6-Channel Seria2010-05-31 586

全部0条评论

快来发表一下你的评论吧 !