TPIC44L02 1.2mA/1.2mA 4 通道栅极驱动器,在短路、开路负载、过击球电压下具有低占空比 PWM数据手册

描述

TPIC44L01、TPIC44L02 和 TPIC44L03 是提供串行和并行的低侧预驱动器 用于控制四个外部 FET 电源开关的输入接口,例如 TI TPIC 系列 电源阵列。这些器件主要用于低频开关、电感 负载应用,如螺线管和继电器。每个通道的故障状态在 serial-data 格式。每个驱动器通道具有独立的关断状态开路负载检测和 ON-state-short-load-short-load/short-to-battery detection--导通状态短路/电池短路检测。电池过压和欠压检测 并在 TPIC44L01/L02 上提供关机功能。在 TPIC44L03 驱动程序上,仅过度使用 提供 VOLTAGE SHUTDOWN。每个通道还提供感应电压瞬态保护 用于外部 FET。

*附件:tpic44l02.pdf

这些器件通过串行输入接口或并行输入接口提供对输出通道的控制。 启用来自任一接口的输出的命令将启用相应的通道门输出到 外部 FET。当控制设备与 必须最小化预驱动器,并且运行速度并不重要。在预驱动程序 必须非常快速或异步响应,建议使用并行输入接口。

对于串行作,控制器件必须将 CS 从高电平转换为低电平,以激活串行输入接口。 发生这种情况时,SDO 使能,故障数据被锁存到串行接口中,并刷新故障标志。

数据通过 SDI 在 SCLK 的低到高转换中同步进入串行寄存器。每个数据字符串必须 至少包含四位数据。在多个设备级联在一起的应用程序中, 对于每个设备,数据必须由 4 位组成。高数据位打开相应的输出通道,低 数据位将其关闭。当串行输入数据被同步输入到器件中时,该器件的故障数据从 SDO 中同步输出。 故障数据包括四个输出中每个输出的短路负载和开路负载标志(位 0x963)的故障标志 渠道。故障数据中的高位表示故障,低位表示不存在故障 渠道。故障寄存器位是异步设置或清除的,以反映硬件的当前状态。故障 当 CS 从高电平转换为低电平时,必须存在,才能在串行故障数据中捕获和报告。 当 CS 为低电平时,无法在 serial register 中捕获新故障。CS 必须在所有 串行数据已 clocked 到 device 中。CS 的低到高转换传输 serial 的最后四位 数据到输出缓冲器将 SDO 置于高阻抗状态,并清除并重新启用故障寄存器。这 TPIC44L01/L02/L03 旨在允许多个设备的串行输入接口级联 一起简化了控制器的串行接口。串行输入数据流经设备,并且 在级联配置中跟随故障数据传出 SDO。

对于并行作,数据直接从并行输入接口 IN0-IN3 传输到相应的 GATE(0x963) 异步输出。并行控制不需要 SCLK 或 CS。并行输入上的 A 1 转动 相应的 channel on,其中 0 将其关闭。请注意,串行输入接口或并行输入 interface 可以启用一个频道。在并联作下,故障数据仍必须通过串行数据收集 接口。

预驱动器监控每个通道的漏极电压,以检测负载短路或负载开路故障情况 分别处于 on 和 off 状态。这些器件提供了使用内部生成的 故障参考电压或通过 VCOMP 外部提供的故障参考电压进行故障检测。这 通过将 VCOMPEN 连接到 GND 来选择内部故障参考,外部参考通过 将 VCOMPEN 连接到 V 抄送 .当通道转动时,将漏极电压与故障参考进行比较 on 检测负载短路情况,当通道关闭时检测负载开路情况。当短路 使用 TPIC44L01 或 TPIC44L03 发生故障,通道关闭并向控制器发送故障标志 device 以及 serial fault register bits。如果在使用 TPIC44L02 时发生故障,则通道 只要存在故障,就会转换为低占空比、脉宽调制 (PWM) 信号。 短路负载故障条件必须至少在短路负载抗尖峰脉冲时间 t 内存在 (STBDG) ,以标记 视为错误。故障标志被发送到控制器件以及串行故障寄存器位。有关故障的更多详细信息 检测作在本数据资料的 Device Operation 部分介绍。

这些器件提供保护,防止电池过电压和电池电压不足的情况,无论 输出通道的状态。当电池电压大于或低于过电压阈值时 低于欠压阈值时,所有通道都被禁用并产生故障标志。电池电压故障 不会在串行故障数据中报告。一旦电池电压故障,输出将恢复正常工作 已更正。当出现电池过剩/电池不足电压情况时,设备会报告 Battery Fault,但禁用负载开路和短路情况的故障报告。open- 和 在 battery fault 条件得到纠正后,shorted-load 条件将重新启用。

这些器件在所有通道上提供感应瞬态保护。漏极电压被箝位以保护 FET。箝位电压由 V 之和定义抄送和外部 FET 的导通电压。预驱动因素 还提供栅源电压 (V GS系列 ) clamp 来保护功率 FET 的栅源端子免受 超过其额定电压。提供外部低电平有效 RESET 以清除 装置。GATE(0x963) 输出在 RESET 被拉低后被禁用。

这些器件在除 CS 和 RESET 之外的所有输入上提供下拉电阻。CS 上使用了上拉电阻 和 RESET 进行设置。

特性

- 4 通道 Serial-In 并联输入低侧 Pre-FET 驱动器

- 设备是可级联的

- 内部 55V 电感负载钳位和 V

GS系列用于外部功率 FET 的保护夹 - 在所有漏极端子上提供独立的负载短路/电池短路故障检测

- 独立的 OFF 状态开路负载故障检测

- 电池过压锁定保护和故障报告

- TPIC44L01 和 TPIC44L02 的电池欠压锁定保护

- 异步漏极开路故障标志

- 器件输出可与多个器件进行有线 OR 运算

- 通过串行输出端子返回故障状态

- 器件内部全局上电复位和外部 RESET 端子

- 具有迟滞的高阻抗 CMOS 兼容输入

- TPIC44L01 和 TPIC44L03 在发生负载短路故障时禁用栅极输出

- TPIC44L02 在发生负载短路故障时将栅极输出转换为低占空比 PWM 模式

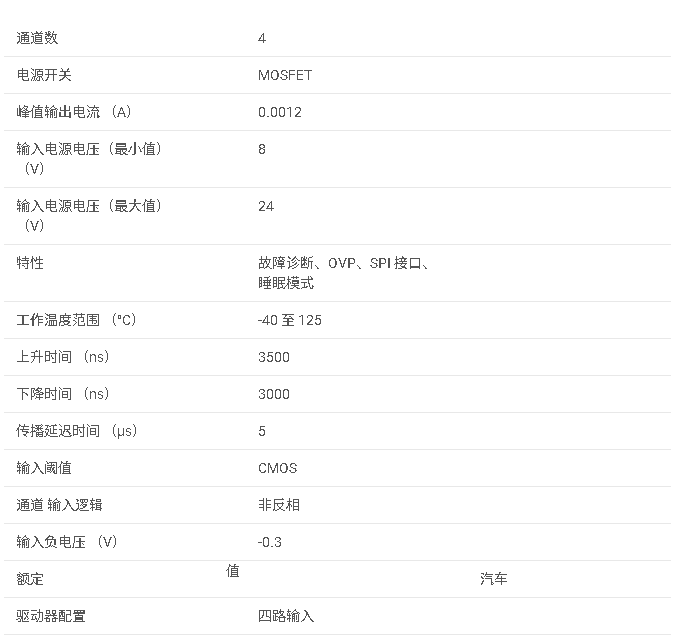

参数

-

DRV8860 38-V 8通道串行接口低侧驱动器技术文档总结2025-10-17 608

-

4 通道 LED 背光驱动器,具有集成升压和高频直接 PWM 调光 skyworksinc2025-07-25 87

-

TPIC46L02 1.2mA/1.2mA 6 通道栅极驱动器,在短路负载、开路负载、过击压下具有低占空比 PWM数据手册2025-05-22 570

-

4-30V 输入、1.2A 固定输出同步降压驱动器2024-05-13 3213

-

4通道串行和并行高侧PRE-FET驱动器TPIC44H01数据表2024-04-09 299

-

具有-5V输入电压能力的20V、4A双通道低侧栅极驱动器UCC27444数据表2024-03-22 408

-

4通道串行和并行低端前置FET驱动器TPIC44L01、TPIC44LO2和TPIC44L03数据表2024-03-19 379

-

如何与MAX3736紧凑型激光驱动器接口2023-01-10 1576

-

TPIC44L01 4 通道串联/并联低侧前置 FET 驱动器2019-01-08 578

-

为继电器、LED、步进电机提供 16 通道低侧驱动器的参考设计资料下载2018-07-24 2520

-

TPIC44L01,pdf (4-Channel Seria2010-05-31 721

全部0条评论

快来发表一下你的评论吧 !