锁存器Latch和触发器Flip-flop有何区别

电子说

描述

锁存器Latch概述

锁存器(Latch)是一种对脉冲电平敏感的存储单元电路,它们可以在特定输入脉冲电平作用下改变状态。锁存,就是把信号暂存以维持某种电平状态。锁存器的最主要作用是缓存,其次完成高速的控制器与慢速的外设的不同步问题,再其次是解决驱动的问题,最后是解决一个I/O口既能输出也能输入的问题。锁存器是利用电平控制数据的输入,它包括不带使能控制的锁存器和带使能控制的锁存器。

锁存器Latch结构

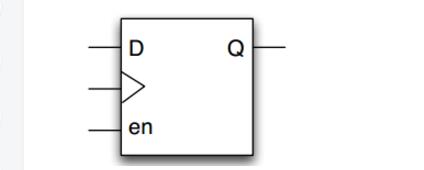

latch:锁存器,是由电平触发,结构图如下:

锁存器latch的优缺点

优点:

1、面积比ff小

门电路是构建组合逻辑电路的基础,而锁存器和触发器是构建时序逻辑电路的基础。门电路是由晶体管构成的,锁存器是由门电路构成的,而触发器是由锁存器构成的。也就是晶体管-》门电路-》锁存器-》触发器,前一级是后一级的基础。latch完成同一个功能所需要的门较触发器要少,所以在asic中用的较多。

2、速度比ff快

用在地址锁存是很合适的,不过一定要保证所有的latch信号源的质量,锁存器在CPU设计中很常见,正是由于它的应用使得CPU的速度比外部IO部件逻辑快许多。

缺点:

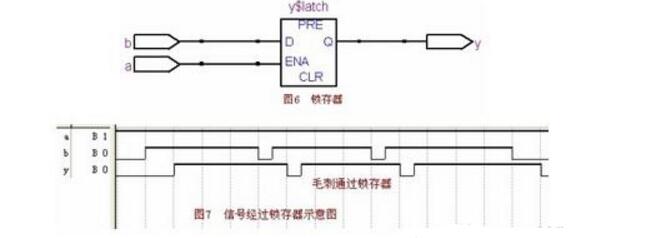

1、电平触发,非同步设计,受布线延迟影响较大,很难保证输出没有毛刺产生

2、latch将静态时序分析变得极为复杂

触发器Flip-flop结构

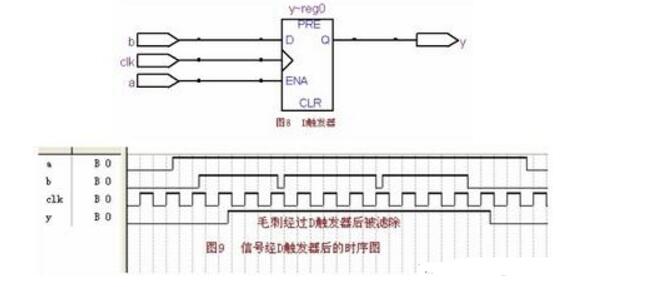

lip-flop:触发器,是时钟边沿触发,可存储1bitdata,是register的基本组成单位,结构图如下:

flip-flop的优缺点

优点:

1、边沿触发,同步设计,不容易受毛刺的印象

2、时序分析简单

缺点:

1、面积比latch大,消耗的门电路比latch多

锁存器Latch和触发器flipflop的区别

1、锁存器Latch和触发器flipflop

锁存器能根据输入端把结果自行保持;触发器是指由时钟边沿触发的存储器单元;由敏感信号(电平,边沿)控制的锁存器就是触发器;

2、写电路时,产生锁存器的原因

if语句中,没有写else,默认保持原值,产生锁存器,可能不是想要的结果;

case语句中,没有写完整default项,也容易产生锁存器;

例子:

always@(aorb)

begin

if(a)q=b;

end

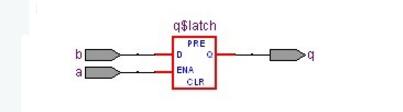

产生了锁存器,如下

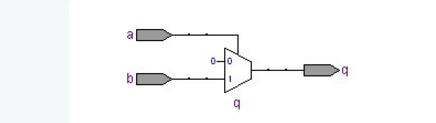

没有锁存器的情况

always@(aorb)

begin

if(a)q=b;

elseq=0;

end

3、避免使用D锁存器,尽量使用D触发器

D锁存器

moduletest_latch(y,a,b);

outputy;inputa;inputb;regy;

always@(aorb)begin

if(a==1’b1)

y=b;

endendmodule

D触发器

moduletest_d(y,clk,a,b);

outputy;inputclk;inputa;inputb;regy;

always@(posedgeclk)begin

if(a==1‘b1)

y=b;

endendmodule

从图8可知,例10对应的电路是D触发器。信号a被综合成D触发器的使能端,只有在时钟上沿到来且a为高时,b信号的值才能传递给a;只要在时钟上升沿期间信号b是稳定,即使在其他时候b还有毛刺,经过D触发器后数据是稳定的,毛刺被滤除。

-

d触发器和d锁存器的区别是什么2024-08-28 3638

-

t触发器与d触发器的区别和联系2024-08-11 6644

-

锁存器和触发器的主要区别是什么2024-07-23 2964

-

触发器与锁存器的区别在哪?2023-12-04 2630

-

怎么用NICE接口读取FPGA上FLIP-FLOP中的数据?2023-08-16 487

-

锁存器与触发器的区别2020-11-29 26359

-

Verilog基本功--flipflop和latch以及register的区别2019-08-27 5227

-

寄存器、锁存器和触发器的区别2018-07-03 4021

-

凔海笔记之FPGA(六):触发器和锁存器2016-05-21 4359

-

锁存器、触发器、寄存器和缓冲器的区别2011-10-09 9361

全部0条评论

快来发表一下你的评论吧 !