MAX3420E USB外设控制器,SPI接口技术手册

描述

概述

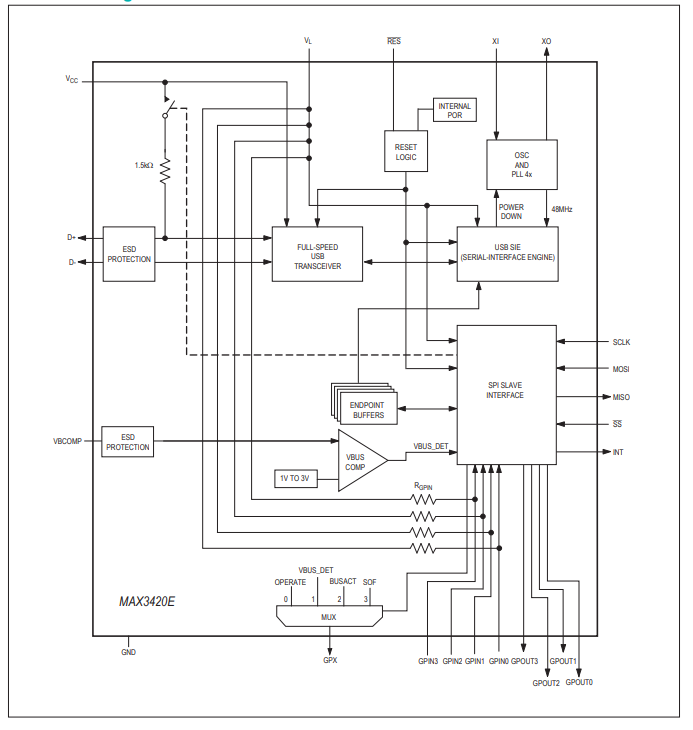

MAX3420E包含实现USB 2.0全速USB外设所需的数字逻辑电路和模拟电路。全速收发器具有±15kV ESD保护和可编程的USB连接和断开特性。内部的串行接口引擎(SIE)负责处理底层USB协议,如错误校验和总线重试。通过工作频率高达26MHz的SPI™接口访问寄存器组,可对MAX3420E进行控制。利用简易的3线或4线SPI接口,可为任何SPI主机(微处理器、ASIC和DSP等)增添USB功能。

内部电平转换器允许SPI接口工作在1.71V至3.6V的系统电压。在MAX3420E内部执行USB定时操作,并在操作完成后提供中断,因此,SPI主机无需定时器来满足USB定时要求。MAX3420E包括4路通用输入及输出,因此所有采用I/O引脚实现SPI接口的微处理器都能再次利用I/O引脚,并获得额外的引脚。

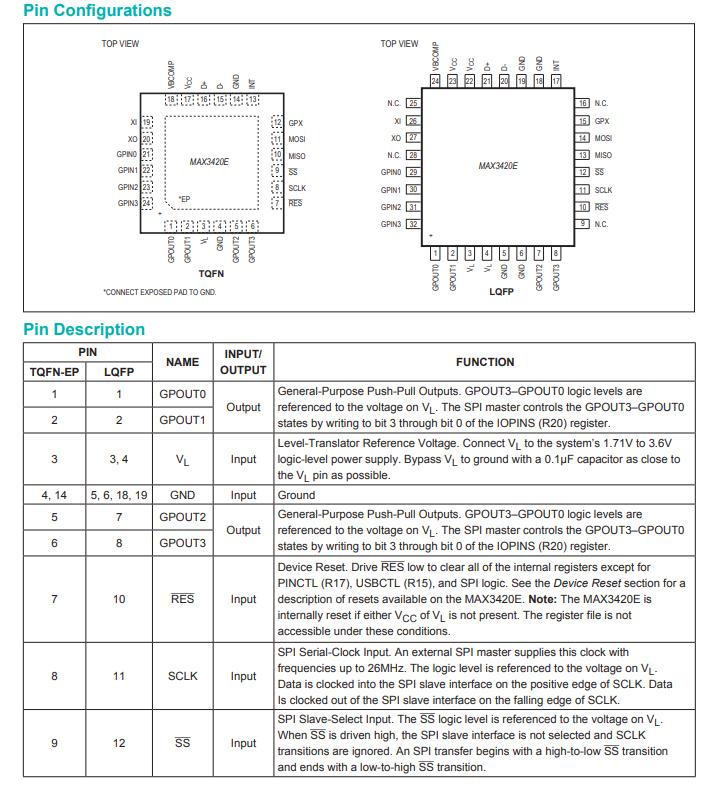

MAX3420E工作在扩展级-40°C至+85°C温度范围,采用32引脚LQFP封装(7mm x 7mm)和节省空间的24引脚TQFN封装(4mm x 4mm)。

数据表:*附件:MAX3420E USB外设控制器,SPI接口技术手册.pdf

应用

- 照相机

- 蜂窝电话

- 定制USB设备

- 台式路由器

- 仪表

- 微处理器和DSP

- MP3播放器

- PC外设

- PDA

- PLC

- 机顶盒

特性

- 独立于微处理器的USB解决方案

- 符合USB 2.0规范(全速工作模式)

- 内置全速USB收发器

- 固件/硬件控制内部D+上拉电阻

- 可编程的3线或4线26MHz SPI接口

- 电平转换器和V

L输入可实现独立的系统接口电压 - 内部比较器检测V

BUS,用于自供电应用 - D+、D-和VBCOMP具有ESD保护功能

- 中断输出引脚(电平或可编程边沿),可实现轮询或中断驱动的SPI接口

- 智能USB串行接口引擎(SIE)

- 自动处理USB流量控制和双缓冲

- 处理底层USB信令

- 包含定时器,可用于USB定时操作,因此SPI主机无需定时

- 内置端点FIFO

- EP0:CONTROL (64字节)

- EP1:OUT,Bulk或Interrupt,2 x 64字节(双缓冲)

- EP2:IN,Bulk或Interrupt,2 x 64字节(双缓冲)

- EP3:IN,Bulk或Interrupt (64字节)

- 双缓冲数据端点允许SPI主机和USB在同一端点上同时传输数据,从而提高了吞吐量

- SETUP数据具有自身的8字节FIFO,简化了固件

- 4路通用输入和4路通用输出

- 可节省空间的LQFP和TQFN封装

框图

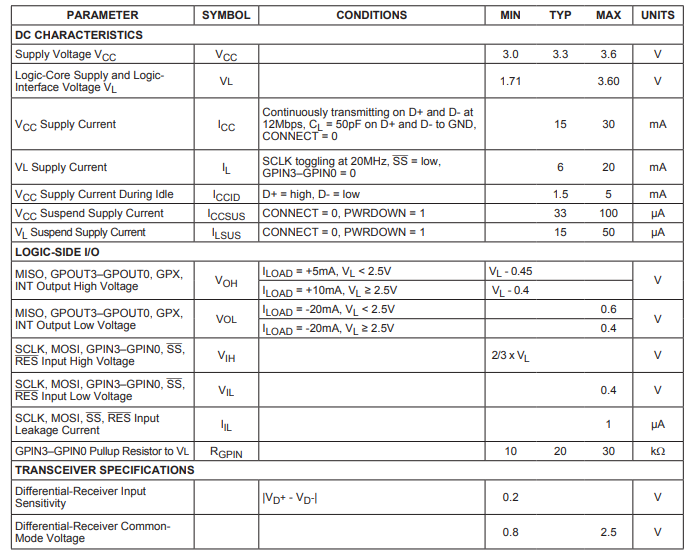

电特性

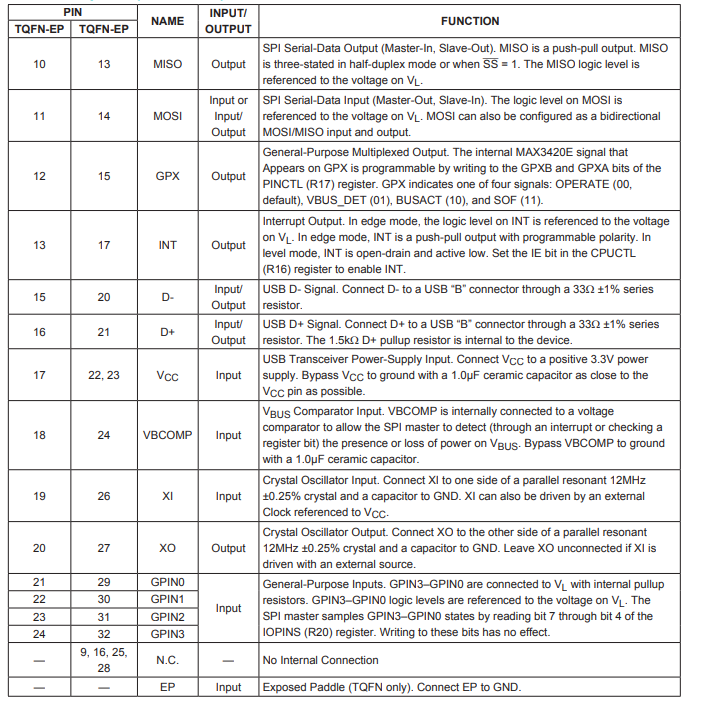

引脚配置描述

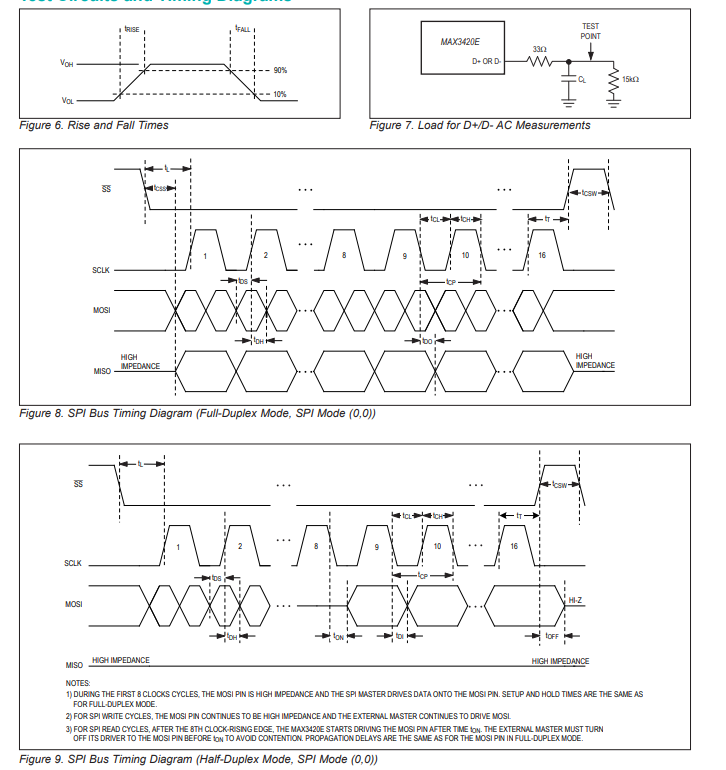

测试电路和时序图

典型工作特性

该器件包含实现符合USB 2.0规范的全速USB外设所需的数字逻辑和模拟电路。D+、D-和VBCOMP引脚提供±15kV的静电放电(ESD)保护。

MAX3420E具有内置USB收发器和一个内部1.5kΩ电阻,该电阻在寄存器位(CONNECT)的控制下连接D+和 V_{CC} 。这使得USB外设能够控制与USB主机的逻辑连接。任何SPI主机都可以通过SPI从机接口与该器件通信,SPI从机接口可在SPI模式(0,0) 或(1,1)下运行。SPI主机通过对内部寄存器进行读写来访问MAX3420E。典型的数据传输包括写入第一个字节,该字节设置寄存器地址和方向,随后再写入字节或读取数据,这些数据来自内部FIFO或MAX3420E的384字节端点缓冲区存储器。

MAX3420E包含以下端点:

- EP0 :64字节双向控制端点

- EP1 :2 x 64字节双缓冲批量/中断输出端点

- EP2 :2 x 64字节双缓冲批量/中断输入端点

- EP3 :64字节批量/中断输入端点

将EP1、EP2、EP3用作批量或中断端点严格取决于端点描述符的功能。在枚举期间,SPI主机返回给USB主机。

MAX3420E的寄存器组和SPI接口经过优化,以减少SPI通信流量。中断输出引脚INT在需要USB服务时(例如数据包到达、数据包发送或主机挂起或恢复总线活动时)通知SPI主机。双缓冲端点通过允许数据同时在USB和SPI接口上传输来维持带宽。

通过向**V_{CC}引脚施加+3.3V电源为USB收发器供电。使用1.0μF陶瓷电容尽可能靠近V_{CC}**引脚进行旁路接地。

MAX3420E的数字内核通过**V_{L}**引脚供电。**V_{L}也用作SPI接口以及所有其他输入和输出的参考电平。将V_{L}连接到系统逻辑电平电源。内部稳压器和V_{L}**允许SPI接口以及所有通用输入和输出在1.71V至3.6V的系统电压下工作。

VBCOMP

MAX3420E具有一个USB V_{bus}检测输入VBCOMP。VBCOMP引脚可承受高达6V的输入电压。使用1.0μF陶瓷电容将VBCOMP旁路接地。根据USB 2.0规范,未供电的USB设备在USB主机切断V_{bus}时,内部必须连接一个1.5kΩ上拉电阻。如果USB主机切断V_{bus} ,VBCOMP通过电压比较器连接到地(这样SPI主机可以通过中断(INT)或检查**V_{bus}位来检测V_{bus}**的丢失)。

-

MAX3421E USB外设/主机控制器,SPI接口技术手册2025-05-22 1826

-

MAX3420E外设控制器的中断系统,看完你就明白了2021-04-19 1104

-

MAX3420E与SPI主控制器构成USB外设器件的中断系统分析2020-04-25 1092

-

MAX3420E全速u***接口芯片与Ez USB相比如何2019-03-01 2082

-

基于SPI芯片MAX3420的USB控制器接口设计2018-11-20 1751

-

MAX3420E系统调试步骤2018-08-24 2027

-

MAX3420E USB外设控制器,SPI接口2011-01-19 1341

-

MAX3420E信息卡2009-04-29 672

-

MAX3420E系统调试2009-04-25 1448

-

MAX3420E的USB杖举程序(及其他)2009-04-23 674

全部0条评论

快来发表一下你的评论吧 !