PCIe总线基本概念,高速串行总线取代传统并行总线是一个大的趋势

电子说

描述

PCIe总线 - - -

PCIe总线的提出可以算是代表着传统并行总线向高速串行总线发展的时代的到来。实际上,不仅是PCI总线到PCIe总线,高速串行总线取代传统并行总线是一个大的趋势。如ATA到SATA,SCSI到USB等……

不过,为了兼容之前的PCI总线设备,虽然PCIe是一种串行总线,无法再物理层上兼容PCI总线,但是在软件层上面却是兼容PCI总线的。

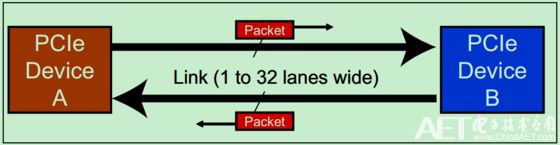

和很多的串行总线一样,PCIe采用了全双工的传输设计,即允许在同一时刻,同时进行发送和接收数据。如下图所示,设备A和设备B之间通过双向的Link相连接,每个Link支持1到32个通道(Lane)。由于是串行总线,因此所有的数据(包括配置信息等)都是以数据包为单位进行发送的。

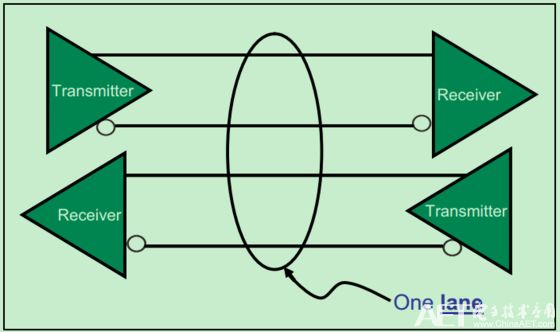

与绝大部分的高速连接一样,PCIe采用了差分对进行收发,以提高总线的性能。一个PCIe Lane的例子如下图所示:

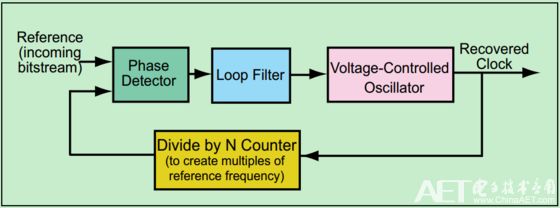

除了差分总线,PCIe还引入了嵌入式时钟的技术(Embedded Clock),即发送端不再向接收端发送时钟,但是接收端可以通过8b/10b的编码从数据Lane中恢复出时钟。一个简单的时钟恢复电路模型如下图所示:

注:PCie Gen3以及之后的版本采用了128b/130b的编码方式。

PCIe相对于PCI总线的另一个大的优势是其的Scalable Performance,即可以根据应用的需要来调整PCIe设备的带宽。如需要很高的带宽,则采用多个Lane(比如显卡);如果并不需要特别高的带宽,则只需要一个Lane就可以了(比如说网卡等)。

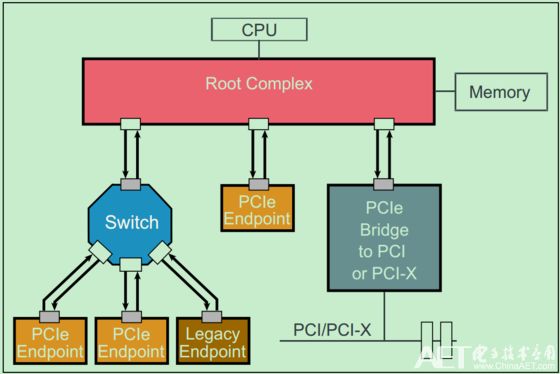

和PCI-X总线一样,由于非常高的传输速度,PCIe是一种点对点连接的总线,而不像PCI那样的共享总线。但是PCIe总线系统可以通过Switch连接多个PCIe设备,也可以通过PCIe桥连接传统的PCI和PCI-X设备。一个简单的PCIe总线系统的拓扑结构图如下所示:

注:这里的Switch实际上包含了多个类似于PCI总线中桥的概念。

图中的Root Complex经常被称为RC或者Root。在PCIe的Spec中,并没有特别详细的关于Root Complex的定义,从实际的角度来讲,可以把Root Complex理解为CPU与PCIe总线系统通信的媒介。Endpoint处于PCIe总线系统拓扑结构中的最末端,一般作为总线操作的发起者(initiator,类似于PCI总线中的主机)或者终结者(Completers,类似于PCI总线中的从机)。显然,Endpoint只能接受来自上级拓扑的数据包或者想上级拓扑发送数据包。

所谓Lagacy PCIe Endpoint是指那些原本准备设计为PCI-X总线接口的设备,但是却被改为PCIe接口的设备。而Native PCIe Endpoint则是标准的PCIe设备。其中,Lagacy PCIe Endpoint可以使用一些在Native PCIe Endpoint禁止使用的操作,如IO Space和Locked Request等。Native PCIe Endpoint则全部通过Memory Map来进行操作,因此,Native PCIe Endpoint也被称为Memory Mapped Devices(MMIO Devices)。

-

干货总结|手把手教你读懂CAN总线#汽车CAN总线 #总线传输 #高速串行总线 #总线解码安泰小课堂 2025-09-11

-

高速并行总线的工作原理是什么 高速并行总线有哪些2024-10-06 2692

-

并行总线和串行总线的区别2023-12-07 6409

-

高速PCB并行总线和串行总线2022-12-29 3029

-

总线的基本概念及其分类简析2022-02-16 1591

-

串行总线的优缺点优点2021-10-15 9915

-

CAN总线的发送基本概念2021-08-19 1893

-

Pcie串行总线介绍#高速接口我是Coder 2021-08-11

-

pcie总线基础知识 精选资料推荐2021-07-29 933

-

高速串行总线与并行总线的差别是什么?2021-05-12 1524

-

并行总线和高速串行总线的布线要求2020-10-21 6203

-

PCB设计必备知识:并行总线VS串行总线2020-07-29 3271

-

PCIE总线2016-03-02 3048

-

基于PCIE/104总线的高速数据接口设计2011-08-17 8945

全部0条评论

快来发表一下你的评论吧 !