pfc电路中用mos管需要注意哪些事项?

电子说

描述

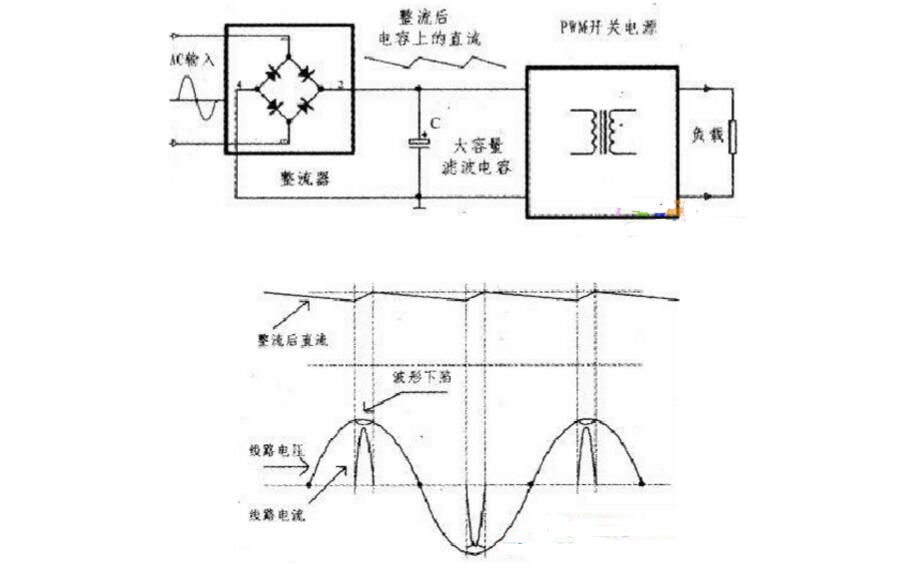

PFC电路的基本结构和工作原理

上图为未加入PFC电路的整流电路的原理方框图,下图为工作波形。由以上分析我们可以看出.未加入PFC电路的整流电路稳定工作以后,只有在市电电压的正负峰值附近二极管才导通,产生脉冲电流。造成离线电源功率因数降低的原因在于电流的导通角太小,在半个周期内远远小于180°,提高功率因数就要设法使电流的波形在整个周期内追踪电压的波形。

既然造成导通角太小的原因是整流器后面接人的大容量滤波电容,有源PFC电路基本思想就是在整流器和大容量滤波电容之间加入一级初级调整,把两者进行隔离,此PFC初级调整变换器输出一个基本稳定的DC电压,同时其输入电流能按照和市电一样的正弦规律变化。

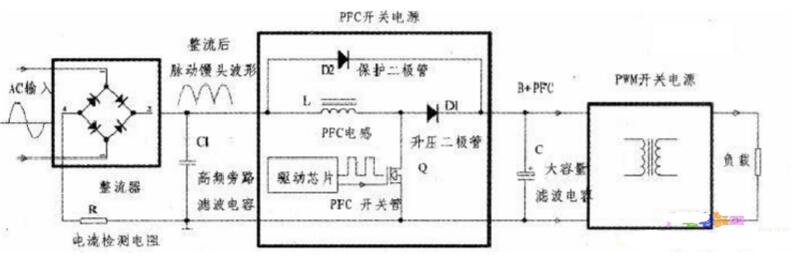

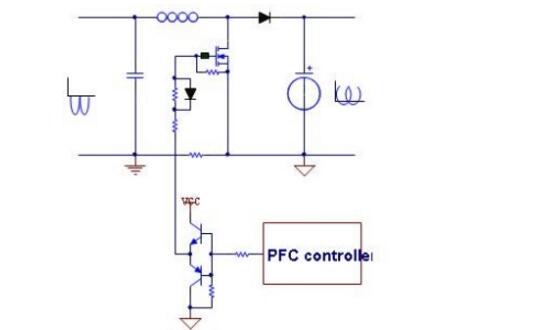

下图所示电路为加入PFC电路的基本结构和工作原理。通过比较,我们可以比较明确看出PFC电路在电源电路结构中的位置和作用。尽管PFC电路的具体形式繁多,不尽相同,工作模式也不一样(CCM电流连续型、DCM不连续型、CRM临界型),但基本的结构大同小异,大部分都是采用升压的boost拓扑结构,因为这种电路形式优点比较多。这也是一种典型的升压开关电路,基本的思想就是前面说的把整流电路和大滤波电容分割,通过控制PFC开关管的导通使输入电流能跟踪输入电压的变化。工作原理并不复杂,彻底搞清楚这个基本电路的原理,就能触类旁通,给独立分析电路打下基础。在这个电路中.PFC电感L在MOS开关管0导通时储存能量,在开关管截止时.电感L上感应出右正左负的电压,将导通时储存的能量通过升压二极管Dl对大的滤波电容充电,输出能量,只不过其输入的电压是没有经过滤波的脉动电压。值得注意的是,平板电视大部分PFC电感L上大都并联着一个二极管D2,该二极管D2具有保护作用。

大家知道:PFC电路后面大的储能滤波电容C和PFC电感L是串联的,由于电感L上的电流不能突变,就对大的滤波电容C的浪涌电流起了限制作用。

并联保护分流二极管D2.由于没有电感的限制作用,对滤波电容的冲击反而会更大,但它可以保护升压二圾管,特别是PFC开关管。Dl是快速恢复二极管(由于开关管是在电感电流不为零的时候关断的,需要承受更大的应力,要求二极管有极低甚至为零的反向恢复电流),承受浪涌电流的能力较弱。减小反向恢复电流和提高浪涌电压承载力是相互牵制的,而D2所采用的是普通的整流二极管,承受浪涌电流的能力很强,如1N5407的额定电流3A.浪涌电流可达200A。

该保护二极管D2表面上降低的是对PFC电感和升压二极管的浪涌冲击,但实际上还有一个重要的作用:保护PFC开关管。

在开机的瞬间,滤波电容的电压尚未建立,由于要对大电容充电.通过PFC电感的电流相对比较大。如果在电源开关接通的瞬间是在正弦波的最大值时,对电容充电的过程中PFC电感L有可能会出现磁饱和的情况,此时PFC电路工作就麻烦了,在磁饱和的情况下,流过PFC开关管的电流就会失去限制,烧坏开关管。为防止悲剧发生,一种方法是对PFC电路工作的工作时序加以控制,即当对大电容的充电完成以后,再启动PFC电路:另一种比较简单的办法就是在PFC线圈到升压二极管上并联一只二极管旁路。启动的瞬间,给大电容的充电提供另一个支路,防止大电流流过PFC线圈造成饱和,过流损坏开关管,保护开关管,同时该保护二极管D2也分流了升压二极管D1上的电流,保护了升压二极管。另外,D2的加入使得对大电容充电过程加快.其上的电压及时建立,也能使PFC电路的电压反馈环路及时工作,减小开机时PFC开关管的导通时间.使PFC电路尽快正常工作。‘所以,综上所述,以上电路中二极管D2的作用是在开机瞬间或负载短路、PFC输出电压低于输入电压的非正常状况下给电容提供充电路径,防止PFC电感磁饱和对PFCMOS管造成的危险,同时也减轻了PFC电感和升压二极管的负担,起到保护作用。在开机正常工作以后,由于D2右面为B+PFC输出电压,电压比左面高,D2呈反偏截止状态,对电路的工作没有影响,D2可选用可承受较大浪涌电流的普通大电流的整流二极管。在有些电源中,PFC后面的电容容量不大,也有的没有接入保护二极管D2,但如果PFC后面是使用大容量的滤波电容,此二极管是不能减少的,对电路的安全性有着重要的意义。

MOS管的结构及工作原理

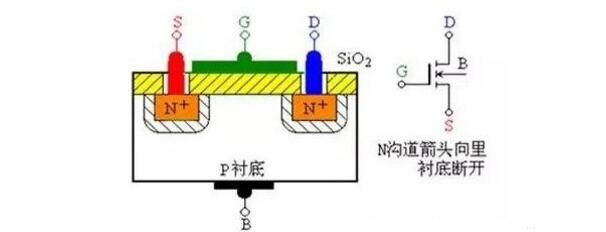

1、结构和符号(以N沟道增强型为例)

在一块浓度较低的P型硅上扩散两个浓度较高的N型区作为漏极和源极,半导体表面覆盖二氧化硅绝缘层并引出一个电极作为栅极。

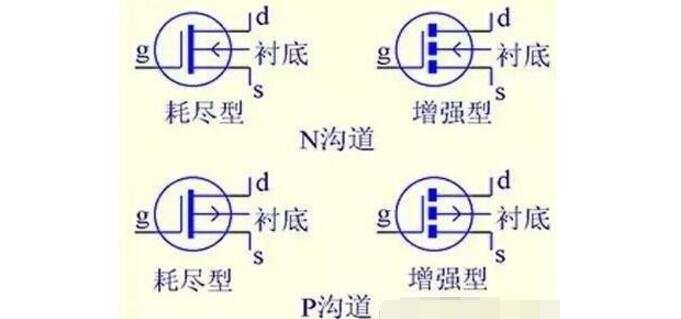

其他MOS管符号

2、工作原理(以N沟道增强型为例)

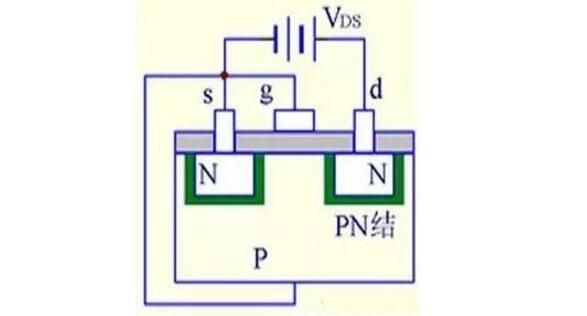

(1)VGS=0时,不管VDS极性如何,其中总有一个PN结反偏,所以不存在导电沟道。

VGS=0,ID=0

VGS必须大于0

管子才能工作。

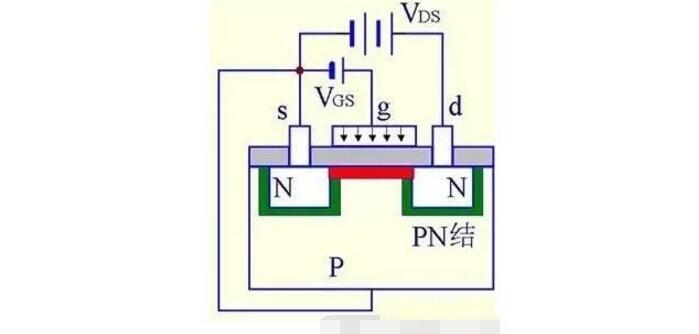

(2)VGS》0时,在Sio2介质中产生一个垂直于半导体表面的电场,排斥P区多子空穴而吸引少子电子。当VGS达到一定值时P区表面将形成反型层把两侧的N区沟通,形成导电沟道。

VGS》0→g吸引电子→反型层→导电沟道

VGS↑→反型层变厚→VDS↑→ID↑

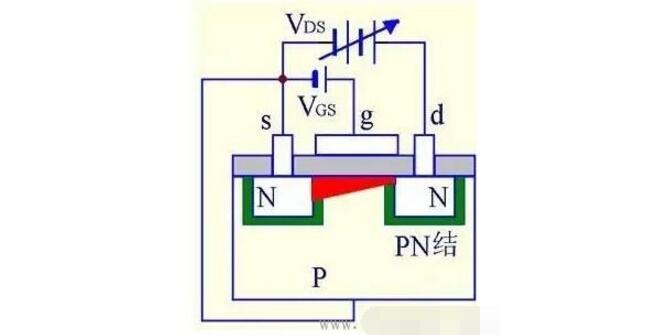

(3)VGS≥VT时而VDS较小时:

VDS↑→ID↑

VT:开启电压,在VDS作

用下开始导电时的VGS°

VT=VGS—VDS

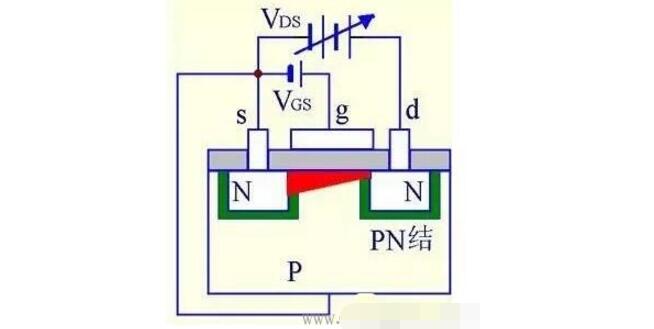

(4)VGS》0且VDS增大到一定值后,靠近漏极的沟道被夹断,形成夹断区。

VDS↑→ID不变

MOS的PFC驱动电路设计及注意事项

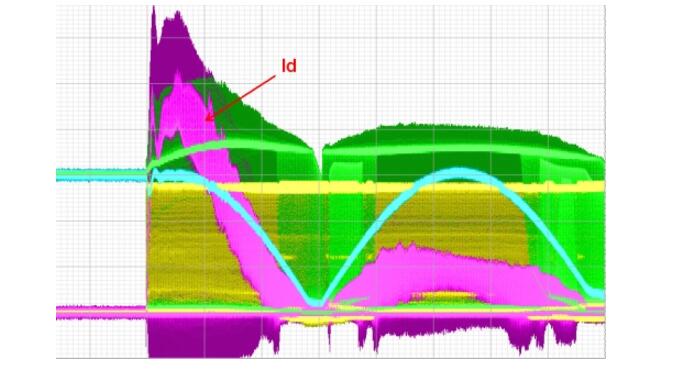

PFC是电源拓扑中对MOS要求比较高的拓扑之一,这是因为:(1)PFC有比较宽的输入电压范围。现代电源大都要求在90-264V的全范围交流电压下工作,这意味着MOS既要有足够的耐压等级又要能承受较大电流;(2)PFC的控制环路速度比较慢,为了平滑100Hz/120Hz的交流整流纹波,PFC反应时间必须达到数十ms。如果控制电路和IC没有专门进行优化,启动过程往往会产生很大的冲击电流,冲击电流可达正常工作时的5-10倍;(3)在缺乏欠压保护的PFC中,当交流电压降到低于90V很多时,电路仍有可能继续工作,这也会产生很高的开关峰值电流,导致干扰和应力超出正常范围。图6为典型的PFC电路,图7为PFC启动时,MOSFET漏极的冲击电流示意图。

图6:典型的PFC电路

图7:PFC启动,MOSFET漏极的冲击电流

MOSFET的驱动电路已经有很多成熟的方案。在实际应用中,出于成本考虑,很多驱动电路都采用比较简单的芯片直驱方案。但是在大功率和性能要求比较高的应用中,驱动电路的设计对MOSFET的可靠性和系统的性能仍有很大影响。

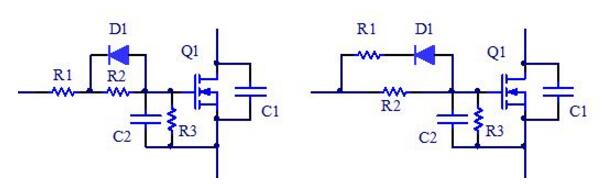

图8:MOSFET两种基本驱动电路结构

在图8中是最常见的MOSFET驱动电路,R1,R2是Rg,左图R1+R2是驱动电压上升时的充电电阻,R1单独作为放电电阻,右图R2单独作为充电电阻,R1和R2并联作为放电电阻。R3是驱动自放电电阻。C1和C2分别是外加的Cds和Cgs电容。

(1)dv/dt的控制策略和注意事项

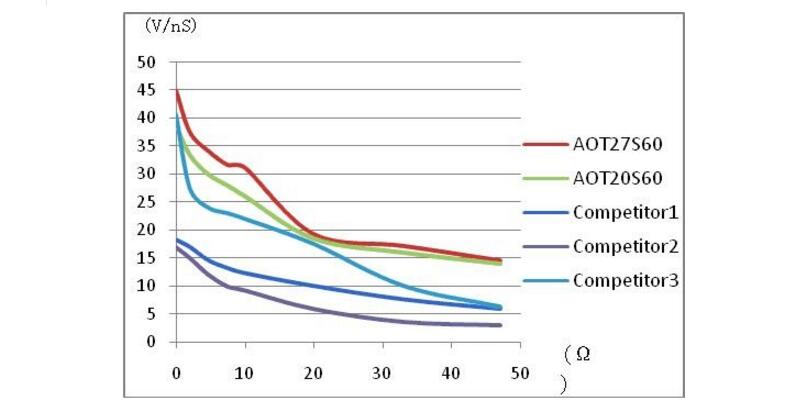

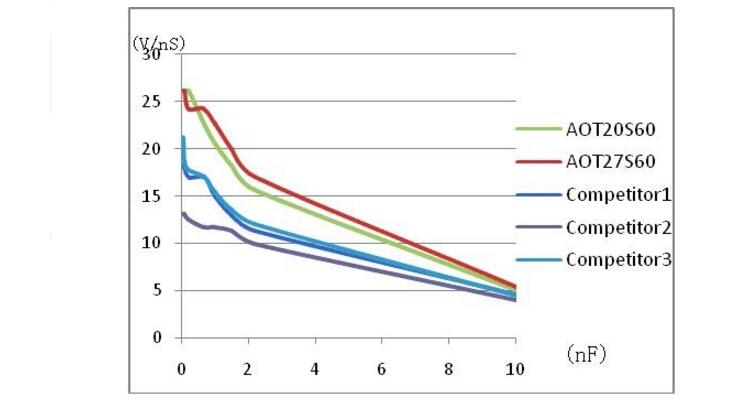

影响dv/dt的因素有MOS自身特性、开关时的电流峰值,以及驱动电路的Rg等。由于AlphaMOS的Ciss特别小,适当的增大Cgs也是有效改善dv/dt的方法。

虽然MOSFET本身可承受的dv/dt和di/dt很高,但是根据经验数据表明,通过改变Rg和Cgs,控制dv/dt不超过20V/ns,对应的di/dt不超过200A/ns,在实际电路中能有较好的工作状态。在效率允许的情况下,dv/dt小于10V/ns,di/dt小于100A/ns更有利于可靠性,如图9和图10所示。

PFC应用中存在宽输入电压范围,输入电压跳变,以及响应时间慢等特点,容易出现比较大的冲击电流。在这种应用中需要特别注意控制峰值电流,同样的驱动参数下,峰值电流越大,开关的dv/dt和di/dt越大。要根据实际应用中的最大峰值电流来调整驱动参数。在设计中,要监测最大冲击电流下的开关波形,以确定是否需要调整驱动参数,使MOSFET工作在较好的状态。

通过漏源极增加额外的电容也可以比较容易地减小dv/dt。在正激有源拑位,桥式软开关,谐振类电路中,合适的漏源极电容有助于开关状态的优化。而在PFC和反激类电路中则需要小心处理,要和效率进行适当的平衡。在效率允许的范围内,通过增大漏源极电容还可以有效地减少EMI。

图9:MOSFET关断dv/dt与放电电阻关系

图10:MOSFET关断dv/dt与Cgs关系

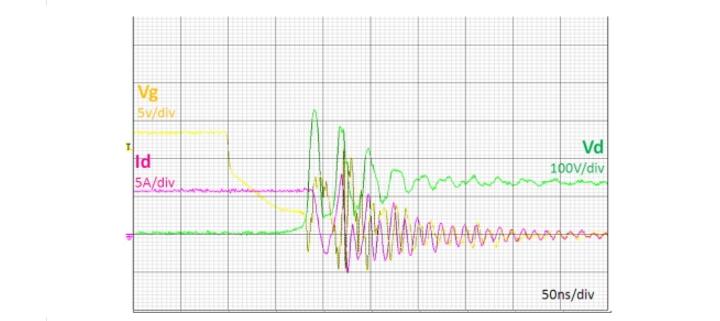

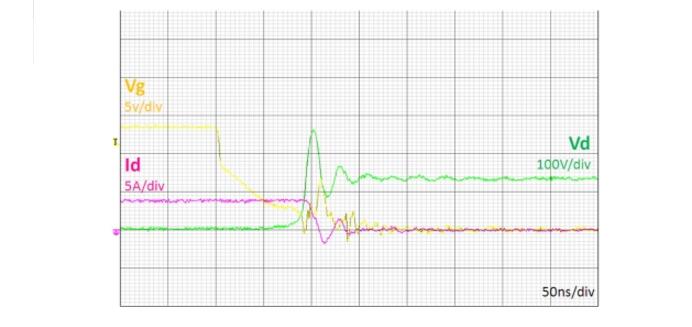

(2)减少通过Cgd耦合对驱动的干扰

由于AlphaMOS的高速开关特性,以及极低的Ciss和Crss,AlphaMOS更容易受layout不良而导致驱动受到干扰。这种干扰往往是由于高频高压的走线和驱动走线靠的太近。使得漏极的高dv/dt信号通过耦合放大的Cgd进入驱动信号。如图11和图12所示。

图11:PFCMOSFET驱动被干扰

图12:PFCMOSFET驱动正常

(3)驱动端加磁珠

驱动端加磁珠是种简单合理的方法,可以抑制驱动端受干扰产生的尖刺。建议将磁珠放置在尽可能靠近MOS驱动端的位置。TO220等插件封装可以采用套管式磁珠,贴片封装的MOS可以采用类似贴片电阻大小的SMD磁珠。选取磁珠需要查阅其数据手册,确保可以通过至少3A的电流,其峰值抑制频率应在30-100MHz。通常情况下磁珠并不会对驱动波形产生影响,当MOS上流过很大电流导致干扰突然增大时,磁珠才起作用。

(4)合理放置驱动元器件的位置

对于有图腾柱驱动或者三极管辅助放电的驱动电路,起到辅助和增强作用的电路元件要尽可能靠近MOS。特别是地线,要直接单点与MOS的源级连接,一定要尽量避免在驱动的地线回路上有主功率部分的电流通过,否则,主功率回路中的大电流会耦合到驱动回路中,造成驱动的误开通和误关断。控制芯片的驱动信号则要远离高压高频走线。由于芯片的地线往往远离MOS的源级,因此只有在小功率的应用中采用芯片直接驱动。较大功率或干扰信号强的应用还是建议带有驱动增强的辅助驱动电路。

-

买电动车需要注意什么及注意事项2010-06-27 37882

-

MOS管栅极驱动电路设计注意事项2023-08-03 3557

-

使用VCA810需要注意的事项?2024-09-24 490

-

选择多路模拟开关需要注意哪些事项?2019-08-08 4330

-

使用MOS管的注意事项2020-06-28 2509

-

设计PCB板有哪些需要注意的事项?2021-04-23 2051

-

配置DMA前需要注意哪些事项?2021-12-13 1497

-

MOS场效应晶体管使用注意事项:2009-03-11 1214

-

数码相机充电电池使用需要注意的问题和事项2009-11-04 2944

-

笔记本拆装时需要注意的重要事项2010-01-25 861

-

CMOS集成电路使用要注意的事项2010-03-05 3338

-

地埋灯的安装需要注意哪些事项?2023-04-14 2107

-

车规级mos管选型需要注意哪些参数2023-03-28 2046

-

螺杆支撑座在使用中需要注意的事项2023-04-10 1433

-

设计软板pcb需要注意哪些事项2023-12-19 1290

全部0条评论

快来发表一下你的评论吧 !