一文读懂Cadence® Sigrity™产品QIR2 新增功能

电子说

描述

▍本文描述了Cadence® Sigrity™产品QIR2 的新增功能。

XtractIM

本节介绍Cadence® Sigrity™ 2017 QIR2版本中XtractIM™的新增功能。

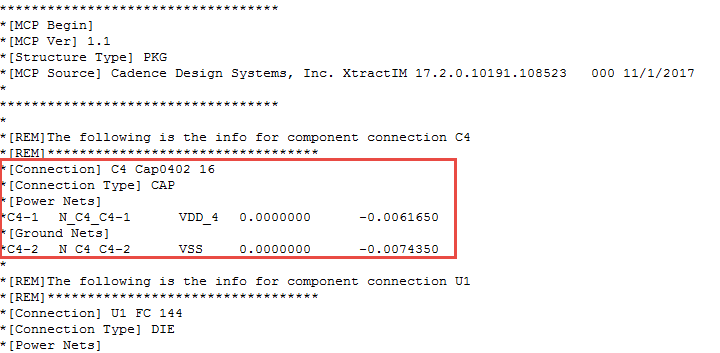

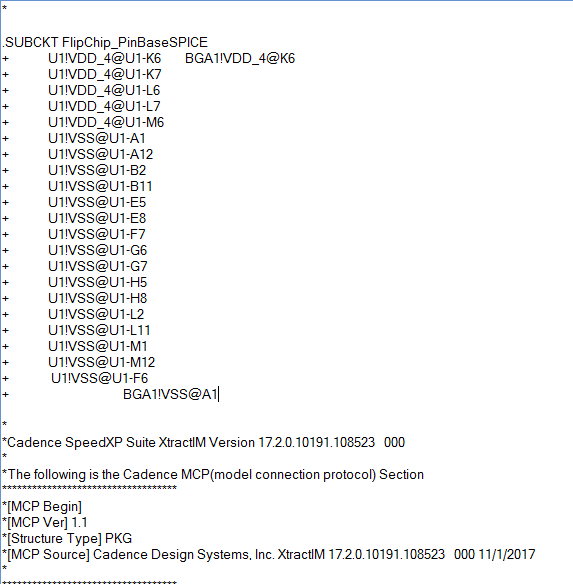

在MCP header中添加了去耦电容引脚

在该版本中,去耦电容的引脚信息被添加到由XtractIM生成的SPICE模型的MCPheader中。

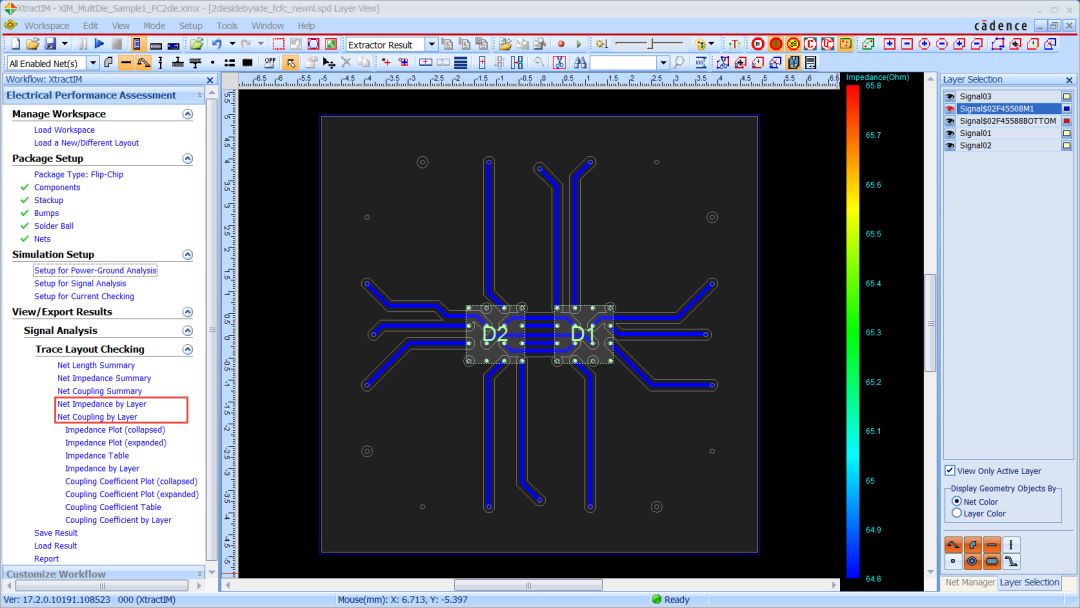

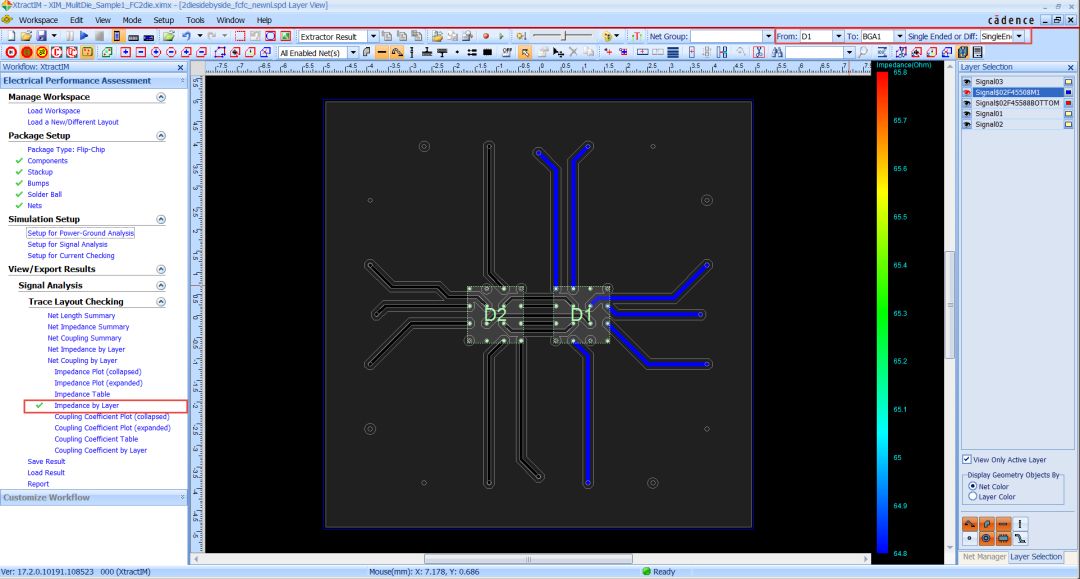

添加了新的选项来显示所有网络的阻抗和耦合结果,用于多Die封装设计

在该版本中,EPA模式中增加了一个新选项,用于显示多Die IC封装设计中所有网络的阻抗和耦合系数。

在以前的版本中,每层每次只能显示一个DIE到BGA的阻抗结果。

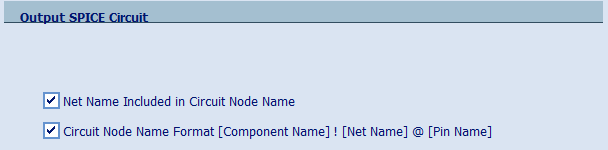

基于引脚的SPICE模型中增加了用于电路节点命名的新选项

在该版本中,添加了一个新的选项Circuit Node Name Format [Component] ! [Net Name] @ [Pin Name] 以提供另一种方法来定义电路节点名称的分隔符号。

选择此选项时,元器件名称和网络名称由!分隔,网络名称和引脚名称由@分隔。

在以前的版本中,基于引脚的SPICE模型中用于电路节点命名规则的分隔符号是下划线(_)。例如,U1_U1-A1。

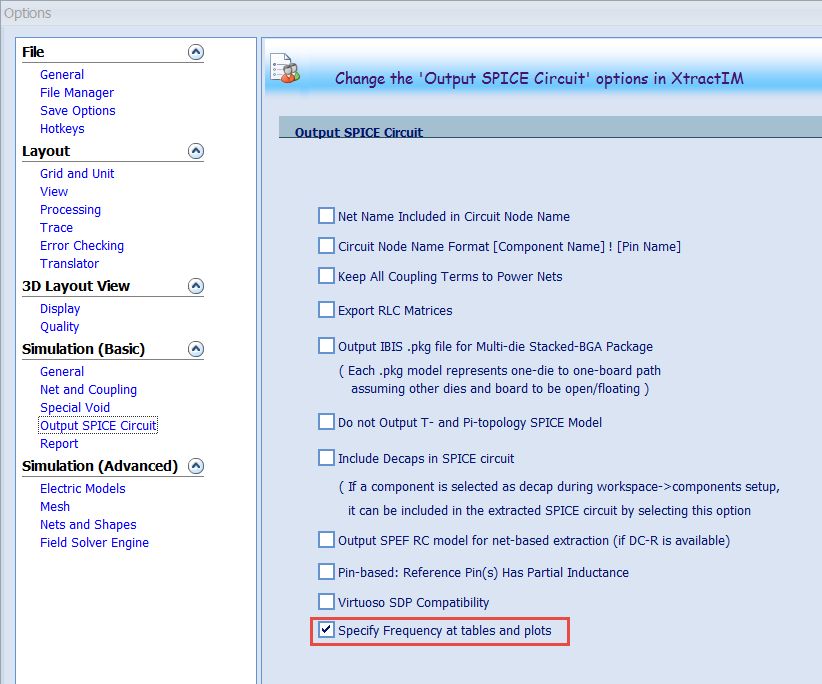

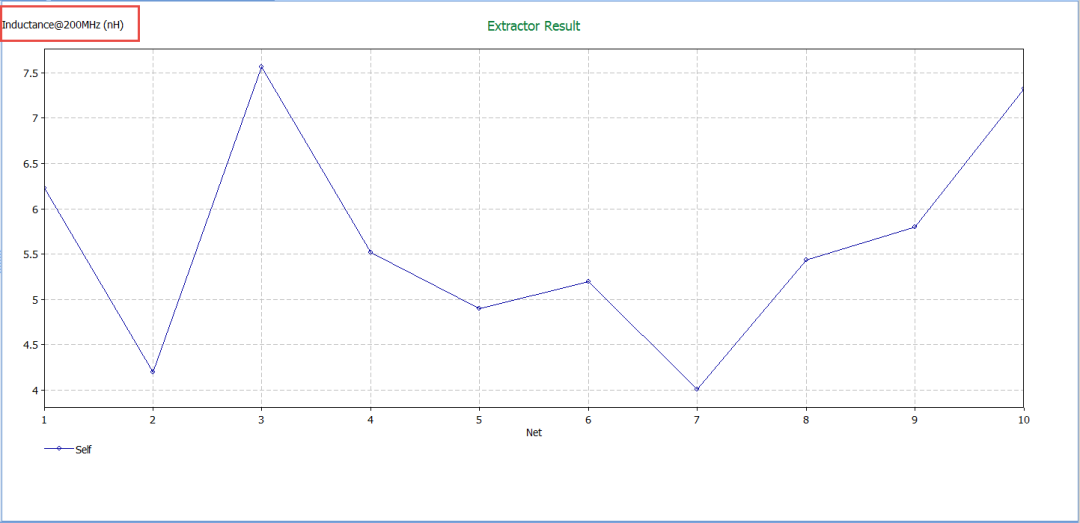

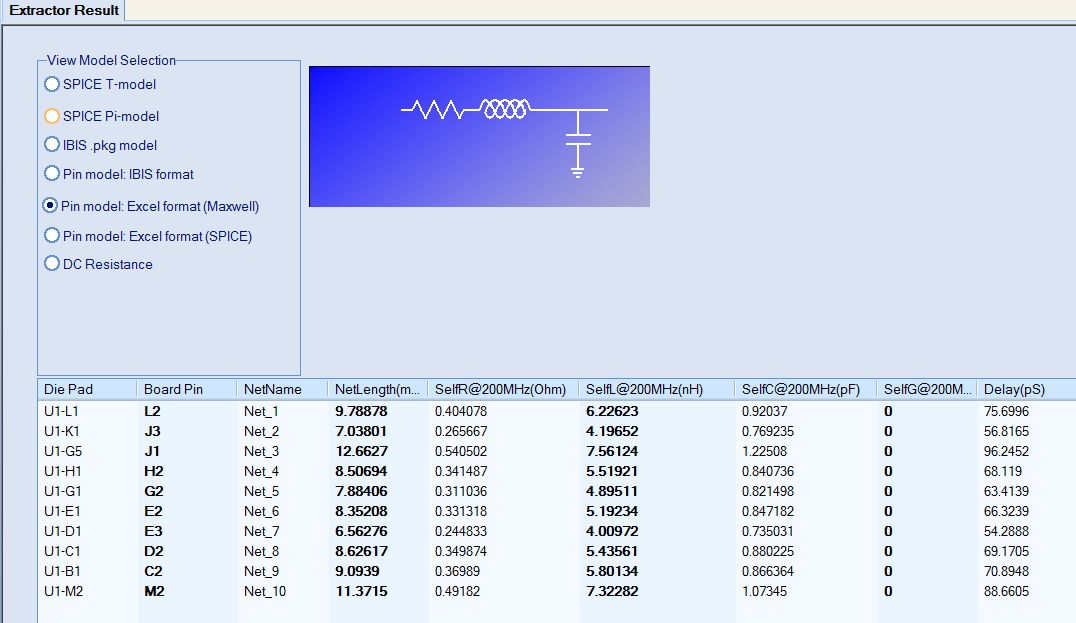

添加新选项用于在RLC报告中显示提取频率

新增加了在表格和图形结果中显示频率的选项,用于以GUI或者report方式查看仿真结果时,显示RLGC提取频率。

每个网络的RLC:

RLC表格:

添加了新的Tcl命令

模型提取模式中添加了以下新的Tcl命令:

-

导出耦合项的阈值

-

优化的带宽

-

电路拓扑

-

提取的频率范围

-

-

Cadence_Sigrity_Seminar2013-05-15 3560

-

2015 Cadence OrCAD, Allegro以及Sigrity新技术研讨会-Invatation2015-05-19 5132

-

一文读懂接口模块的组合应用有哪些?2021-05-17 2435

-

一文读懂什么是NEC协议2021-10-15 2667

-

Cadence发布创新Sigrity 2017快速实现PCB电源完整性签核2017-02-07 1664

-

Cadence® Sigrity™ 2017 OptimizePI™ QIR2 版本中的新增功能2018-04-28 7513

-

Cadence发布Cadence Sigrity 2018版本,可帮助设计团队进一步缩短PCB设计周期2018-07-25 15262

-

Cadence发布下一代Sigrity X产品,将系统分析加快10倍2021-03-17 2988

-

电源完整性之Cadence Sigrity Power DC_IR_Drop仿真2021-11-09 1837

-

一文读懂MCU的特点、功能及如何编写2021-12-05 1357

-

2022 Sigrity SPB 17.4 版本更新 I SystemSI 为GDDR6接口增加基于JEDEC自动化分析功能2022-10-09 4930

-

2022 SPB 17.4 版本更新 I Sigrity SystemPI 允许自定义搭建链路进行系统级PDN和电源纹波分析2022-11-17 5135

-

一文读懂,什么是BLE?2023-11-27 4868

-

利用Sigrity Aurora进行PCB布线后的仿真分析-阻抗及寄生参数析2024-02-26 8035

-

一文读懂新能源汽车的功能安全2024-09-04 724

全部0条评论

快来发表一下你的评论吧 !