W55MH32高性能以太网单片机开发课件 第十四章 ADC(上篇)

W55MH32高性能以太网单片机开发课件 第十四章 ADC(上篇)

描述

单芯片解决方案,开启全新体验——W55MH32 高性能以太网单片机

W55MH32是WIZnet重磅推出的高性能以太网单片机,它为用户带来前所未有的集成化体验。这颗芯片将强大的组件集于一身,具体来说,一颗W55MH32内置高性能Arm® Cortex-M3核心,其主频最高可达216MHz;配备1024KB FLASH与96KB SRAM,满足存储与数据处理需求;集成TOE引擎,包含WIZnet全硬件TCP/IP协议栈、内置MAC以及PHY,拥有独立的32KB以太网收发缓存,可供8个独立硬件socket使用。如此配置,真正实现了All-in-One解决方案,为开发者提供极大便利。

在封装规格上,W55MH32 提供了两种选择:QFN68和QFN100。

W55MH32Q采用QFN68封装版本,尺寸为8x8mm,它拥有36个GPIO、3个ADC、12通道DMA、17个定时器、2个I2C、3个串口、2个SPI接口(其中1个带I2S接口复用)、1个CAN以及1个USB2.0。在保持与同系列其他版本一致的核心性能基础上,仅减少了部分GPIO以及SDIO接口,其他参数保持一致,性价比优势显著,尤其适合网关模组等对空间布局要求较高的场景。紧凑的尺寸和精简化外设配置,使其能够在有限空间内实现高效的网络连接与数据交互,成为物联网网关、边缘计算节点等紧凑型设备的理想选择。 同系列还有QFN100封装的W55MH32L版本,该版本拥有更丰富的外设资源,适用于需要多接口扩展的复杂工控场景,软件使用方法一致。

此外,本W55MH32支持硬件加密算法单元,WIZnet还推出TOE+SSL应用,涵盖TCP SSL、HTTP SSL以及MQTT SSL等,为网络通信安全再添保障。

为助力开发者快速上手与深入开发,基于W55MH32Q这颗芯片,WIZnet精心打造了配套开发板。开发板集成WIZ-Link芯片,借助一根USB C口数据线,就能轻松实现调试、下载以及串口打印日志等功能。开发板将所有外设全部引出,拓展功能也大幅提升,便于开发者全面评估芯片性能。

第十四章 ADC(上篇)

1ADC简介

12 位 ADC 是一种逐次逼近型模拟数字转换器。它有多达 18 个通道,可测量 16 个外部和 2 个内部信号源。各通道的 A/D 转换可以单次、连续、扫描或间断模式执行。ADC 的结果可以左对齐或右对齐方式存储在 16 位数据寄存器中。

模拟看门狗特性允许应用程序检测输入电压是否超出用户定义的高/低阀值。ADC 的输入时钟不得超过 14MHz,它是由 PCLK2 经分频产生。

1.1 ADC主要特征

W55MH32的ADC的主要特征如下:

12 位分辨率

- ⚪转换结束、注入转换结束和发生模拟看门狗事件时产生中断

- ⚪单次和连续转换模式

- ⚪从通道 0 到通道 n 的自动扫描模式

- ⚪自校准

- ⚪带内嵌数据一致性的数据对齐

- ⚪采样间隔可以按通道分别编程

- ⚪规则转换和注入转换均有外部触发选项

- ⚪间断模式

- ⚪双重模式(带 2 个或以上 ADC 的器件)

- ⚪ADC 转换时间:时钟为 56MHz 时为 1μs(时钟为 72MHz 为 1.17μs)

- ⚪ADC 供电要求:2.4V 到 3.6V

- ⚪ADC 输入范围:VREF-≤VIN≤VREF+

- ⚪规则通道转换期间有 DMA 请求产生。下图是 ADC 模块的方框图。

注意: 如果有 VREF-引脚,必须和 VSSA 相连接

1.2 ADC功能描述

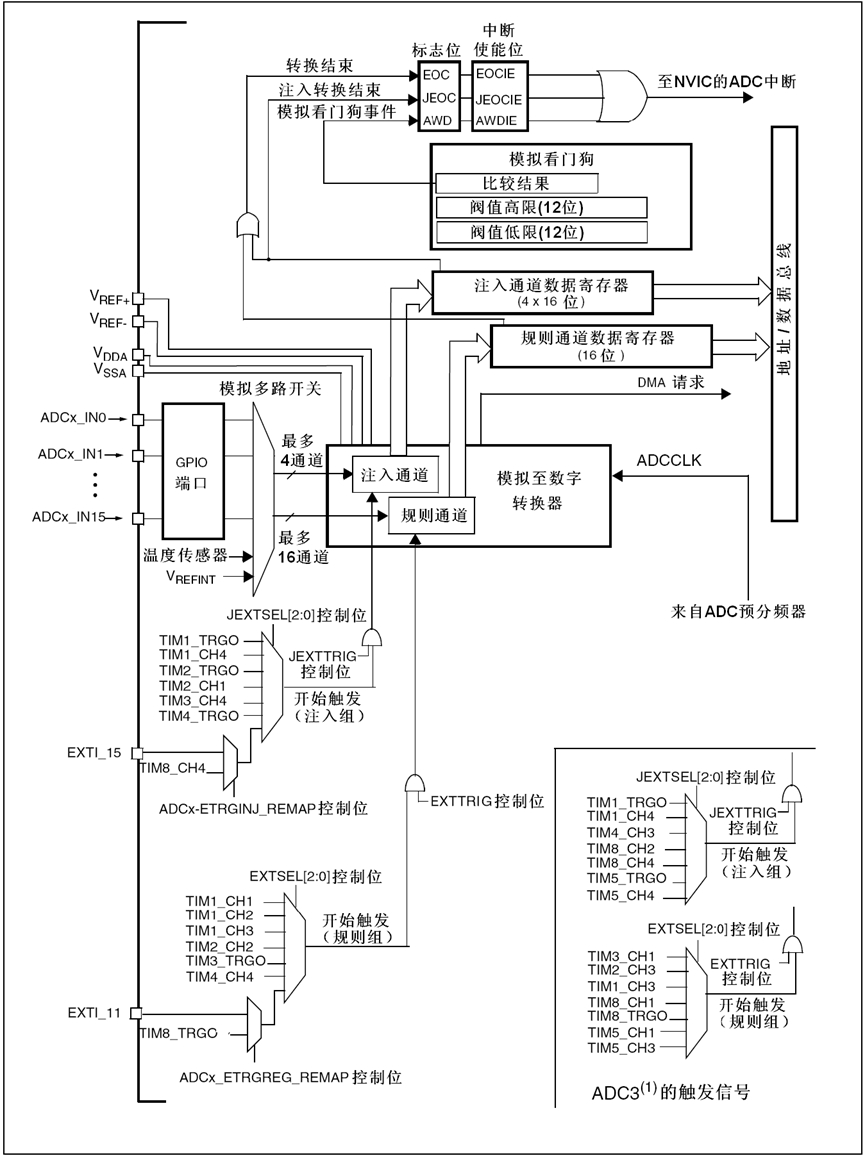

ADC功能框图如下:

单个 ADC 框图

1.ADC3 的规则转换和注入转换触发与 ADC1 和 ADC2 的不同。

| 名称 | 信号类型 | 注解 |

| VREF+ | 输入,模拟参考正极 | ADC 使用的高端 / 正极参考电压,2.4V ≤ VREF+ ≤ VDDA |

| VDDA(*) | 输入,模拟电源 | 等效于 VDO 的模拟电源:2.4V ≤ VDDA ≤ VDD (3.6V) |

| VREF- | 输入,模拟参考负极 | ADC 使用的低端 / 负极参考电压,VREF- ≈ VSSA |

| VSSA(*) | 输入,模拟电源地 | 等效于 VSS 的模拟电源地 |

| ADC_IN[15:0] | 模拟输入 | 16 个 ADC 模拟通道 |

1.VDDA 和 VSSA 应该分别连接到 VDD 和 VSS。

1.3 ADC开关控制

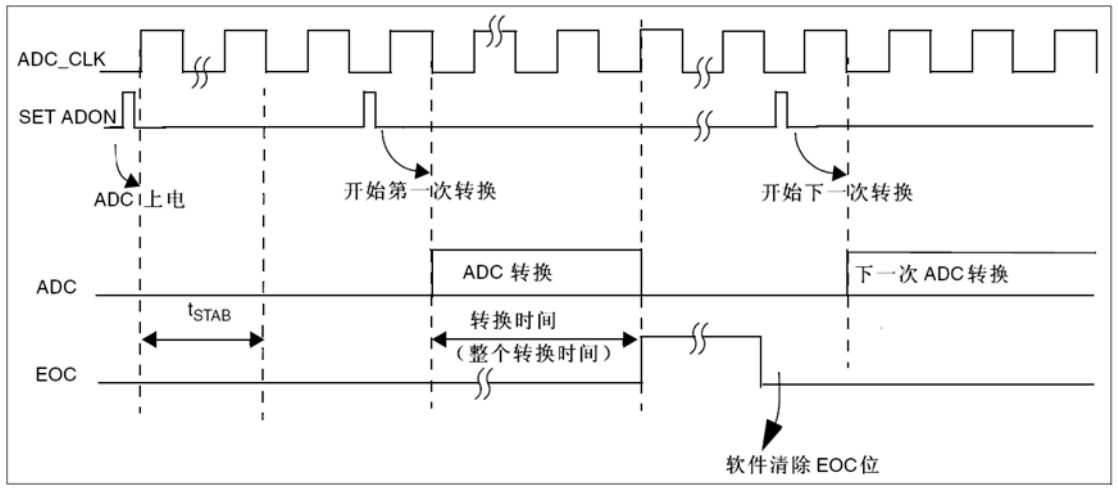

通过设置 ADC_CR2 寄存器的 ADON 位可给 ADC 上电。当第一次设置 ADON 位时,它将 ADC 从断电状态下唤醒。ADC 上电延迟一段时间后(tSTAB),再次设置 ADON 位时开始进行转换。

通过清除 ADON 位可以停止转换,并将 ADC 置于断电模式。在这个模式中,ADC 几乎不耗电(仅几个μA)。

1.4 ADC时钟

由时钟控制器提供的 ADCCLK 时钟和 PCLK2(APB2 时钟)同步。RCC 控制器为 ADC 时钟提供一个专用的可编程预分频器,详见第 6 节-复位和时钟控制(RCC)。

2 模式选择

2.1 通道选择

有 16 个多路通道。可以把转换组织成两组:规则组和注入组。在任意多个通道上以任意顺序进行的一系列转换构成成组转换。例如,可以如下顺序完成转换:通道 3、通道 8、通道 2、通道 2、通道 0、通道 2、通道 2、通道 15。

规则组由多达 16 个转换组成。规则通道和它们的转换顺序在 ADC_SQRx 寄存器中选择。规则组中转换的总数应写入 ADC_SQR1 寄存器的 L[3:0]位中。

注入组由多达 4 个转换组成。注入通道和它们的转换顺序在 ADC_JSQR 寄存器中选择。注入组里的转换总数目应写入 ADC_JSQR 寄存器的 L[1:0]位中。

如果 ADC_SQRx 或 ADC_JSQR 寄存器在转换期间被更改,当前的转换被清除,一个新的启动脉冲将发送到 ADC 以转换新选择的组。

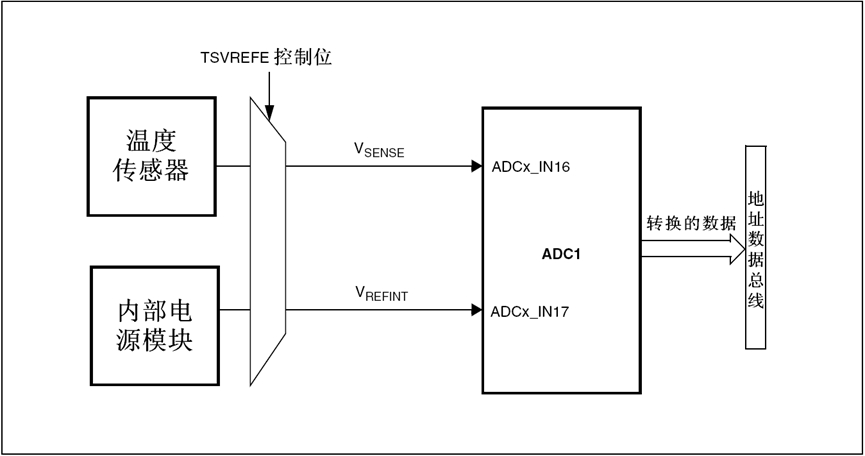

温度传感器/VREFINT 内部通道

温度传感器和通道 ADC1_IN16 相连接,内部参照电压 VREFINT 和 ADC1_IN17 相连接。可以按注入或规则通道对这两个内部通道进行转换。

注意:温度传感器和 VREFINT 只能出现在主 ADC1 中。

2.2 单次转换模式

单次转换模式下,ADC 只执行一次转换。该模式既可通过设置 ADC_CR2 寄存器的 ADON 位(只适用于规则通道)启动也可通过外部触发启动(适用于规则通道或注入通道),这时 CONT 位为 0。一旦选择通道的转换完成:

如果一个规则通道被转换:转换数据被储存在 16 位 ADC_DR 寄存器中EOC(转换结束)标志被设置如果设置了 EOCIE,则产生中断。

如果一个注入通道被转换:转换数据被储存在 16 位的 ADC_DRJ1 寄存器中JEOC(注入转换结束)标志被设置如果设置了 JEOCIE 位,则产生中断。然后 ADC 停止。

2.3 连续转换模式

在连续转换模式中,当前面 ADC 转换一结束马上就启动另一次转换。此模式可通过外部触发启动或通过设置 ADC_CR2 寄存器上的 ADON 位启动,此时 CONT 位是 1。

每个转换后:如果一个规则通道被转换:转换数据被储存在 16 位的 ADC_DR 寄存器中EOC(转换结束)标志被设置如果设置了 EOCIE,则产生中断。

如果设置了 JEOCIE 位,则产生中断。

2.4 时序图

如下图所示,ADC 在开始精确转换前需要一个稳定时间 tSTAB。在开始 ADC 转换和 14 个时钟周期后,EOC 标志被设置,16 位 ADC 数据寄存器包含转换的结果。

时序图

2.5 模拟看门狗

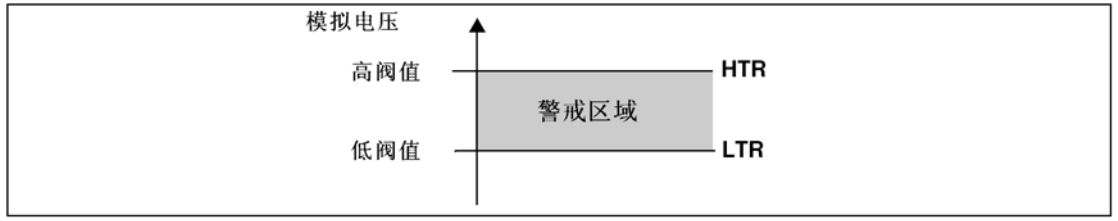

如果被 ADC 转换的模拟电压低于低阀值或高于高阀值,AWD 模拟看门狗状态位被设置。阀值位于ADC_HTR 和 ADC_LTR 寄存器的最低 12 个有效位中。通过设置 ADC_CR1 寄存器的 AWDIE 位以允许产生相应中断。

阀值独立于由 ADC_CR2 寄存器上的 ALIGN 位选择的数据对齐模式。通过配置 ADC_CR1 寄存器,模拟看门狗可以作用于 1 个或多个通道。

模拟看门狗警戒区

模拟看门狗通道选择

| 模拟看门狗警戒的通道 | ADC_CR1 寄存器控制位 | ||

| AWDSGL 位 | AWDEN 位 | JAWDEN 位 | |

| 无 | 任意值 | 0 | 0 |

| 所有注入通道 | 0 | 0 | 1 |

| 所有规则通道 | 0 | 1 | 0 |

| 所有注入和规则通道 | 0 | 1 | 1 |

| 单一的 (1) 注入通道 | 1 | 0 | 1 |

| 单一的 (1) 规则通道 | 1 | 1 | 0 |

| 单一的 (1) 注入或规则通道 | 1 | 1 | 1 |

2.6 扫描模式

此模式用来扫描一组模拟通道。

扫描模式可通过设置 ADC_CR1 寄存器的 SCAN 位来选择。一旦这个位被设置,ADC 扫描所有被ADC_SQRX 寄存器(对规则通道)或 ADC_JSQR(对注入通道)选中的所有通道。在每个组的每个通道上执行单次转换。在每个转换结束时,同一组的下一个通道被自动转换。如果设置了 CONT 位,转换不会在选择组的最后一个通道上停止,而是再次从选择组的第一个通道继续转换。

如果设置了 DMA 位,在每次 EOC 后,DMA 控制器把规则组通道的转换数据传输到 SRAM 中。而注入通道转换的数据总是存储在 ADC_JDRx 寄存器中。

2.7 注入通道管理

触发注入

清除 ADC_CR1 寄存器的 JAUTO 位,并且设置 SCAN 位,即可使用触发注入功能。

1. 利用外部触发或通过设置 ADC_CR2 寄存器的 ADON 位,启动一组规则通道的转换。

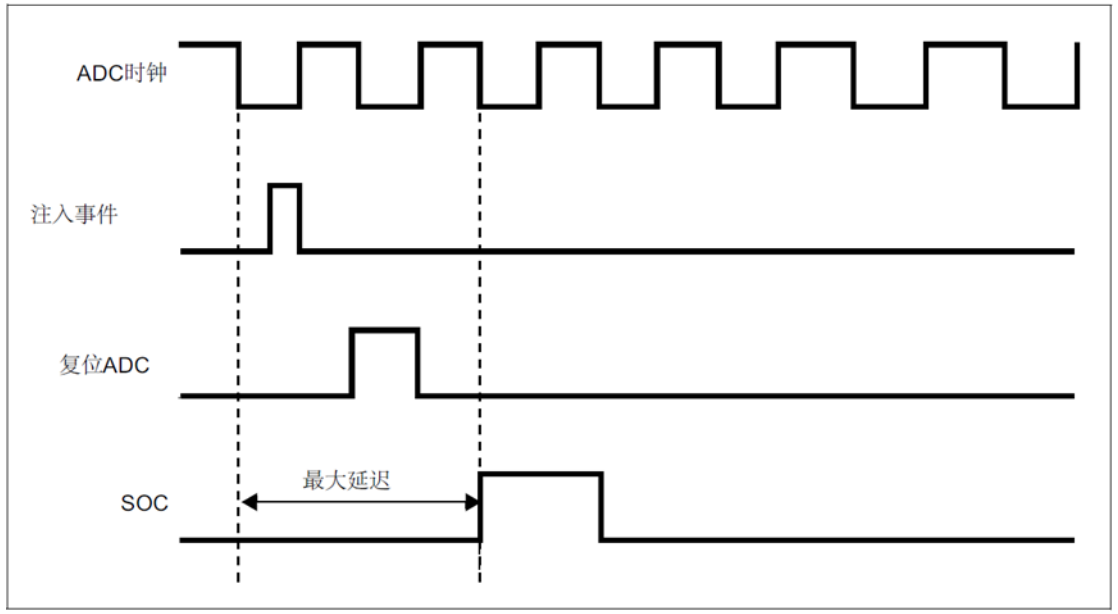

2. 如果在规则通道转换期间产生一外部注入触发,当前转换被复位,注入通道序列被以单次扫描方式进行转换。

3. 然后,恢复上次被中断的规则组通道转换。如果在注入转换期间产生一规则事件,注入转换不会被中断,但是规则序列将在注入序列结束后被执行。

注: 当使用触发的注入转换时,必须保证触发事件的间隔长于注入序列。例如:序列长度为 28 个ADC 时钟周期(即 2 个具有 1.5 个时钟间隔采样时间的转换),触发之间最小的间隔必须是 29 个ADC 时钟周期。

自动注入

如果设置了 JAUTO 位,在规则组通道之后,注入组通道被自动转换。这可以用来转换在ADC_SQRx 和 ADC_JSQR 寄存器中设置的多至 20 个转换序列。

在此模式里,必须禁止注入通道的外部触发。

如果除 JAUTO 位外还设置了 CONT 位,规则通道至注入通道的转换序列被连续执行。对于 ADC 时钟预分频系数为 4 至 8 时,当从规则转换切换到注入序列或从注入转换切换到规则序列时,会自动插入 1 个 ADC 时钟间隔;当 ADC 时钟预分频系数为 2 时,则有 2 个 ADC 时钟间隔的延迟。

注意: 不可能同时使用自动注入和间断模式。

注入转换延时

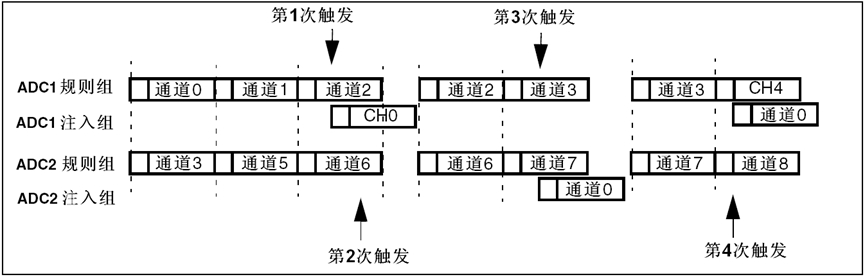

2.8 间断模式

规则组

此模式通过设置 ADC_CR1 寄存器上的 DISCEN 位激活。它可以用来执行一个短序列的 n 次转换(n<=8),此转换是 ADC_SQRx 寄存器所选择的转换序列的一部分。数值 n 由 ADC_CR1 寄存器的DISCNUM[2:0]位给出。

一个外部触发信号可以启动 ADC_SQRx 寄存器中描述的下一轮 n 次转换,直到此序列所有的转换完成为止。总的序列长度由 ADC_SQR1 寄存器的 L[3:0]定义。

举例:

n=3,被转换的通道=0、1、2、3、6、7、9、10

第一次触发:转换的序列为 0、1、2

第二次触发:转换的序列为 3、6、7

第三次触发:转换的序列为 9、10,并产生 EOC 事件

第四次触发:转换的序列 0、1、2

注意: 当以间断模式转换一个规则组时,转换序列结束后不自动从头开始。当所有子组被转换完成,下一次触发启动第一个子组的转换。在上面的例子中,第四次触发重新转换第一子组的通道 0、1 和 2。

注入组

此模式通过设置 ADC_CR1 寄存器的 JDISCEN 位激活。在一个外部触发事件后,该模式按通道顺序逐个转换 ADC_JSQR 寄存器中选择的序列。一个外部触发信号可以启动 ADC_JSQR 寄存器选择的下一个通道序列的转换,直到序列中所有的转换完成为止。总的序列长度由 ADC_JSQR 寄存器的 JL[1:0]位定义。

举例:

n=1,被转换的通道=1、2、3

第一次触发:通道 1 被转换

第二次触发:通道 2 被转换

第三次触发:通道 3 被转换,并且产生 EOC 和 JEOC 事件

第四次触发:通道 1 被转换

注意: 1.当完成所有注入通道转换,下个触发启动第 1 个注入通道的转换。在上述例子中,第四个触发重新转换第 1 个注入通道 1。

2.不能同时使用自动注入和间断模式。

3.必须避免同时为规则和注入组设置间断模式。间断模式只能作用于一组转换。

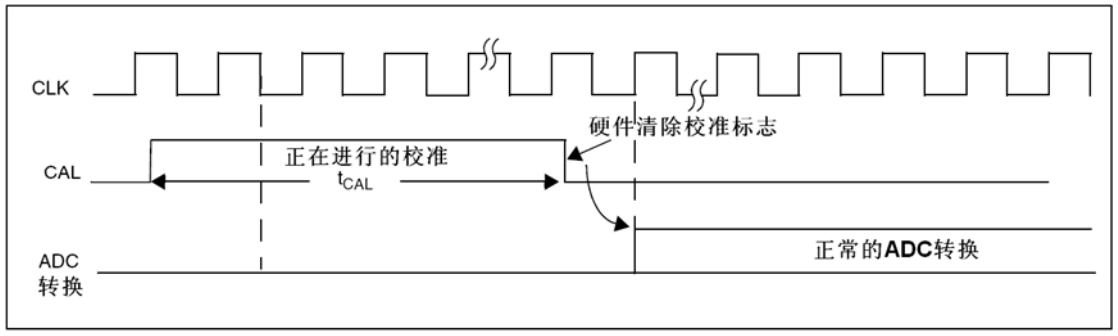

3 校准

ADC 有一个内置自校准模式。校准可大幅减小因内部电容器组的变化而造成的准精度误差。在校准期间,在每个电容器上都会计算出一个误差修正码(数字值),这个码用于消除在随后的转换中每个电容器上产生的误差。

通过设置 ADC_CR2 寄存器的 CAL 位启动校准。一旦校准结束,CAL 位被硬件复位,可以开始正常转换。建议在上电时执行一次 ADC 校准。校准阶段结束后,校准码储存在 ADC_DR 中。

注意:1.建议在每次上电后执行一次校准。

2.启动校准前,ADC 必须处于关电状态(ADON='0')超过至少两个 ADC 时钟周期。

校准时序图

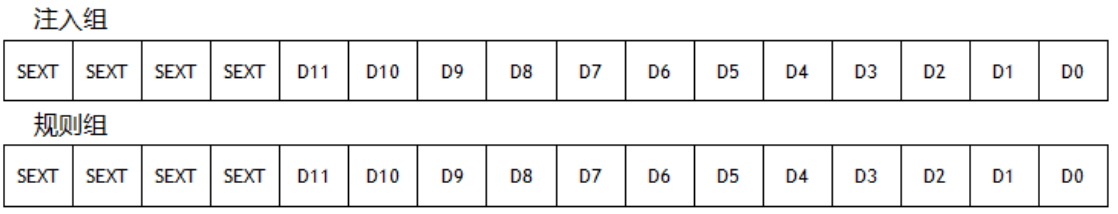

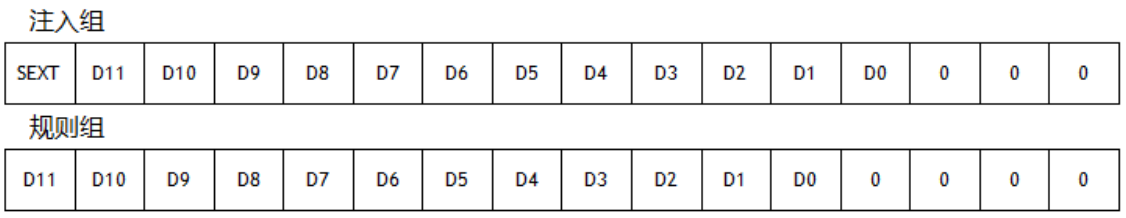

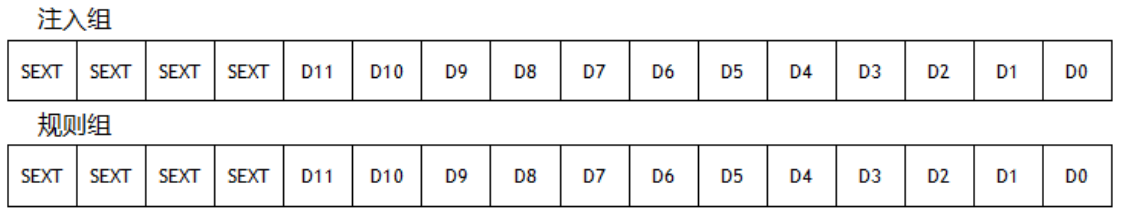

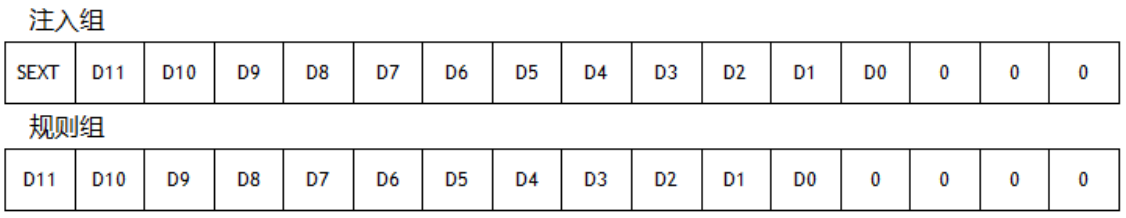

3.1 数据对齐

ADC_CR2 寄存器中的 ALIGN 位选择转换后数据储存的对齐方式。数据可以左对齐或右对齐,如

注入组通道转换的数据值已经减去了在 ADC_JOFRx 寄存器中定义的偏移量,因此结果可以是一个负值。SEXT 位是扩展的符号值。

对于规则组通道,不需减去偏移值,因此只有 12 个位有效。

数据右对齐

数据左对齐

3.2 可编程的通道采样时间

ADC 使用若干个 ADC_CLK 周期对输入电压采样,采样周期数目可以通过 ADC_SMPR1 和ADC_SMPR2 寄存器SMP[2:0]位更改。每个通道可以分别用不同的时间采样。

总转换时间如下计算:

TCONV=采样时间+12.5 个周期

例如:

当 ADCCLK=14MHz,采样时间为 1.5 周期

TCONV=1.5+12.5=14 周期=1μs

3.3 外部触发转换

转换可以由外部事件触发(例如定时器捕获,EXTI 线)。如果设置了 EXTTRIG 控制位,则外部事件就能够触发转换。EXTSEL[2:0]和 JEXTSEL2:0]控制位允许应用程序选择 8 个可能的事件中的某一个,可以触发规则和注入组的采样。

注意: 当外部触发信号被选为 ADC 规则或注入转换时,只有它的上升沿可以启动转换。

表 ADC1 和 ADC2 用于规则通道的外部触发

| 触发源 | 类型 | EXTSSEL[2:0] |

| TIM1_CC1 事件 | 来自片上定时器的内部信号 | 000 |

| TIM1_CC2 事件 | 001 | |

| TIM1_CC3 事件 | 010 | |

| TIM2_CC2 事件 | 011 | |

| TIM3_TRGO 事件 | 100 | |

| TIM4_CC4 事件 | 101 | |

| EXTI 线 11/TIM8_TRGO事件(1) | 外部引脚/来自片上定时器的内部信号 | 110 |

| SWSTART | 软件控制位 | 111 |

(1)对于规则通道,选中 EXTI 线路 11 或 TIM8_TRGO 作为外部触发事件,可以分别通过设置 ADC1和 ADC2 的 ADC1_ETRGREG_REMAP 位和 ADC2_ETRGREG_REMAP 位实现。

表 ADC1 和 ADC2 用于注入通道的外部触发

| 触发源 | 连接类型 | JEXTSE[2:0] |

| TIM1_TRGO 事件 | 来自片上定时器的内部信号 | 000 |

| TIM1_CC4 事件 | 001 | |

| TIM2_TRGO 事件 | 010 | |

| TIM2_CC1 事件 | 011 | |

| TIM3_CC4 事件 | 100 | |

| TIM4_TRGO 事件 | 101 | |

| EXTI 线 15/TIM8_CC4 事件 (1) | 外部引脚 / 来自片上定时器的内部信号 | 110 |

| SWSTART | 软件控制位 | 111 |

(2)为注入信道选择外部触发器 EXTIline15 或 TIM8-CC4 事件是通过分别为 ADC1 和 ADC2 配置ADC1ETRGINJREMAP 和 ADC2 ETRGINJ·REMAP 来完成的。

表 ADC3 用于规则通道的外部触发

| 触发源 | 连接类型 | EXTSSEL[2:0] |

| TIM3_CC1 事件 | 来自片上定时器的内部信号 | 000 |

| TIM2_CC3 事件 | 001 | |

| TIM1_CC3 事件 | 010 | |

| TIM8_CC1 事件 | 011 | |

| TIM8_TRGO 事件 | 100 | |

| TIM5_CC1 事件 | 101 | |

| TIM5_CC3 事件 | 110 | |

| SWSTART | 软件控制位 | 111 |

表 ADC3 用于注入通道的外部触发

| 触发源 | 连接类型 | JEXTSE[2:0] |

| TIM1_TRGO 事件 | 来自片上定时器的内部信号 | 000 |

| TIM1_CC4 事件 | 001 | |

| TIM4_CC3 事件 | 010 | |

| TIM8_CC2 事件 | 011 | |

| TIM8_CC4 事件 | 100 | |

| TIM5_TRGO 事件 | 101 | |

| TIM5_CC4 事件 | 110 | |

| JSWSTART | 软件控制位 | 111 |

软件触发事件可以通过对寄存器 ADC_CR2 的 SWSTART 或 JSWSTART 位置'1'产生。规则组的转换可以被注入触发打断。

3.4 DMA请求

因为规则通道转换的值储存在一个仅有的数据寄存器中,所以当转换多个规则通道时需要使用DMA,这可以避免丢失已经存储在 ADC_DR 寄存器中的数据。只有在规则通道的转换结束时才产生 DMA 请求,并将转换的数据从 ADC_DR 寄存器传输到用户指定的目的地址。

注: 只有 ADC1 和 ADC3 拥有 DMA 功能。由 ADC2 转化的数据可以通过双 ADC 模式,利用 ADC1 的DMA 功能传输。

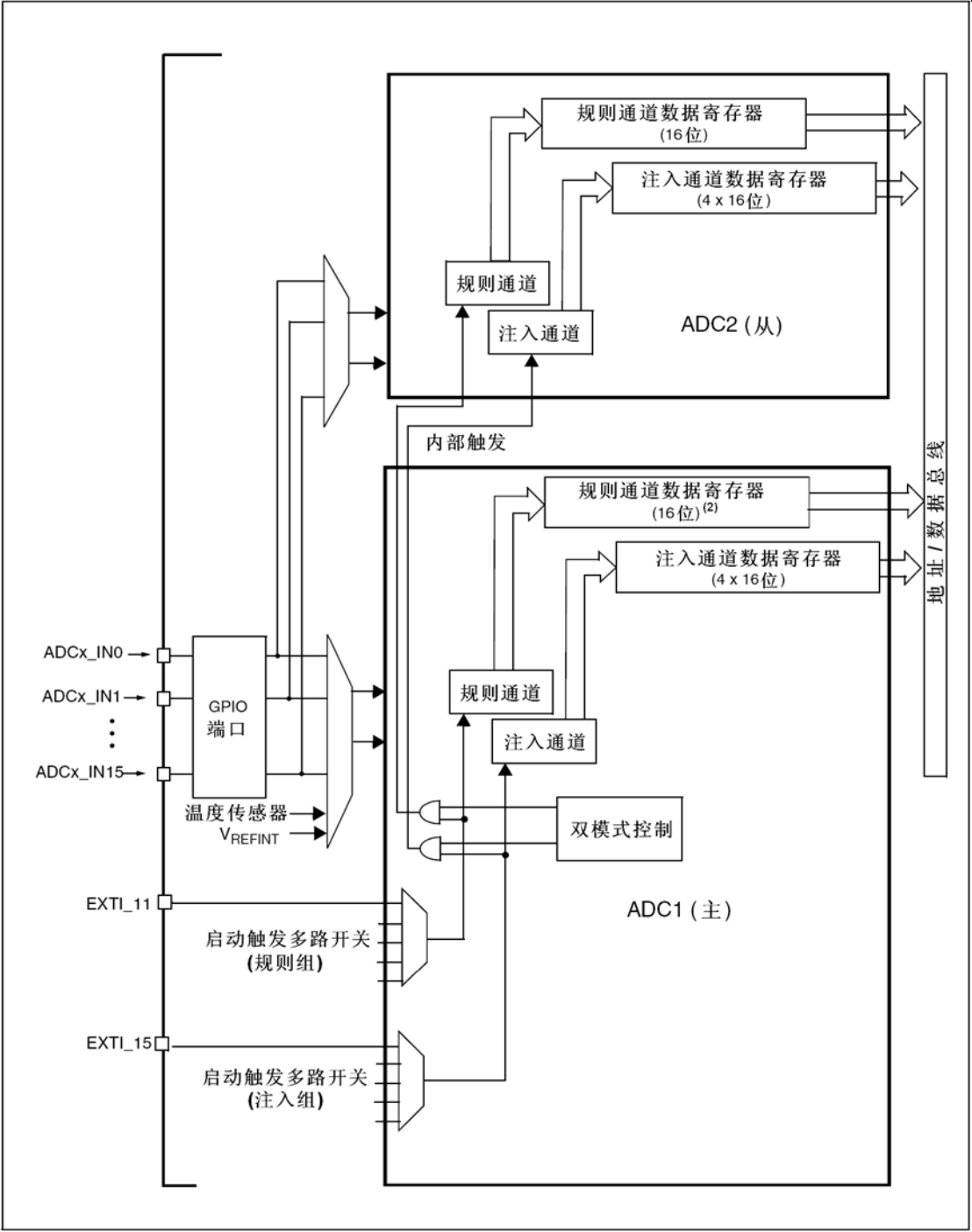

4 双ADC模式

在有 2 个或以上 ADC 模块的产品中,可以使用双 ADC 模式。在双 ADC 模式里,根据 ADC1_CR1 寄存器中 DUALMOD[2:0]位所选的模式,转换的启动可以是ADC1 主和 ADC2 从的交替触发或同步触发。

注意: 在双 ADC 模式里,当转换配置成由外部事件触发时,用户必须将其设置成仅触发主 ADC,从 ADC设置成软件触发,这样可以防止意外的触发从转换。但是,主和从 ADC 的外部触发必须同时被激活。

共有 6 种可能的模式:

- ⚪同步注入模式

- ⚪同步规则模式

- ⚪快速交叉模式

- ⚪慢速交叉模式

- ⚪交替触发模式

- ⚪独立模式

还有可以用下列方式组合使用上面的模式:

- ⚪同步注入模式+同步规则模式

- ⚪同步规则模式+交替触发模式

- ⚪同步注入模式+交叉模式

注意: 在双 ADC 模式里,为了在主数据寄存器上读取从转换数据,必须使能 DMA 位,即使不使用 DMA传输规则通道数据。

双 ADC 框图

1.外部触发信号作用于 ADC2,但在本图中没有显示。

2.在某些双 ADC 模式中,在完整的 ADC1 数据寄存器(ADC1_DR)中包含了 ADC1 和 ADC2 的规则转换数据。

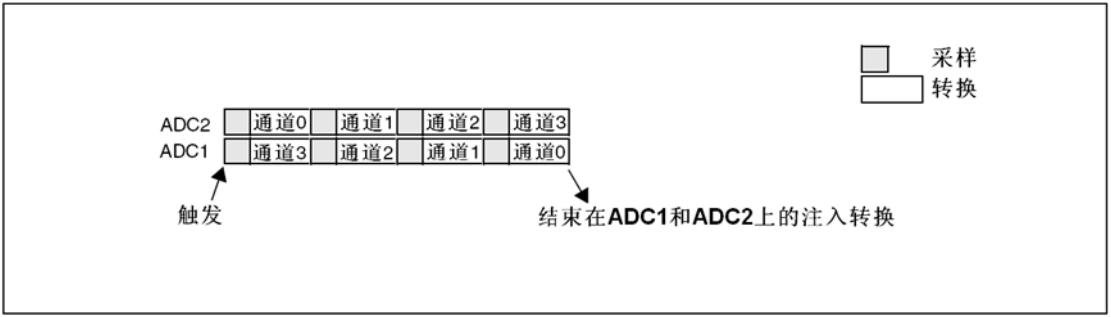

4.1 同步注入模式

此模式转换一个注入通道组。外部触发来自 ADC1 的注入组多路开关(由 ADC1_CR2 寄存器的JEXTSEL[2:0]选择),它同时给 ADC2 提供同步触发。

注意: 不要在 2 个 ADC 上转换相同的通道(两个 ADC 在同一个通道上的采样时间不能重叠)。在 ADC1 或 ADC2 的转换结束时:

转换的数据存储在每个 ADC 接口的 ADC_JDRx 寄存器中。

当所有 ADC1/ADC2 注入通道都被转换时,产生 JEOC 中断(若任一 ADC 接口开放了中断)。

注: 在同步模式中,必须转换具有相同时间长度的序列,或保证触发的间隔比 2 个序列中较长的序列长,否则当较长序列的转换还未完成时,具有较短序列的 ADC 转换可能会被重启。

在 4 个通道上的同步注入模式

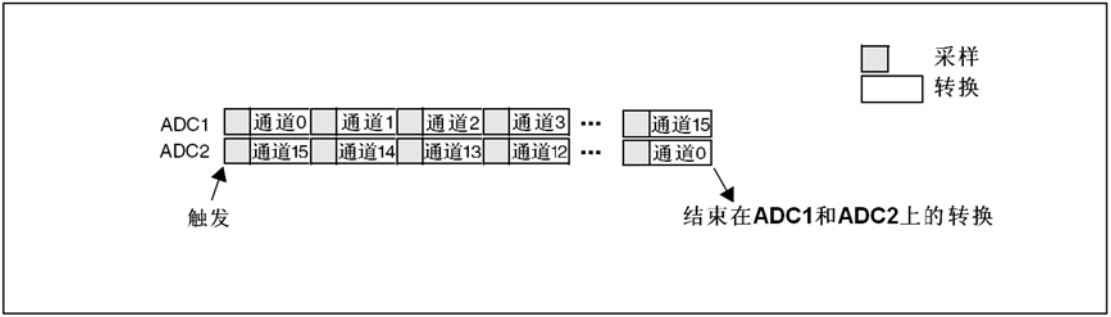

4.2 同步规则模式

此模式在规则通道组上执行。外部触发来自 ADC1 的规则组多路开关(由 ADC1_CR2 寄存器的EXTSEL[2:0]选择),它同时给 ADC2 提供同步触发。

注意: 不要在 2 个 ADC 上转换相同的通道((两个 ADC 在同一个通道上的采样时间不能重叠)。在 ADC1 或 ADC2 的转换结束时:

产生一个 32 位 DMA 传输请求(如果设置了 DMA 位),32 位的 ADC1_DR 寄存器内容传输到SRAM 中,它上半个字包含 ADC2 的转换数据,低半个字包含 ADC1 的转换数据。

当所有 ADC1/ADC2 规则通道都被转换完时,产生 EOC 中断(若任一 ADC 接口开放了中断)。

注: 在同步规则模式中,必须转换具有相同时间长度的序列,或保证触发的间隔比 2 个序列中较长的序列长,否则当较长序列的转换还未完成时,具有较短序列的 ADC 转换可能会被重启。

在 16 个通道上的同步规则模式

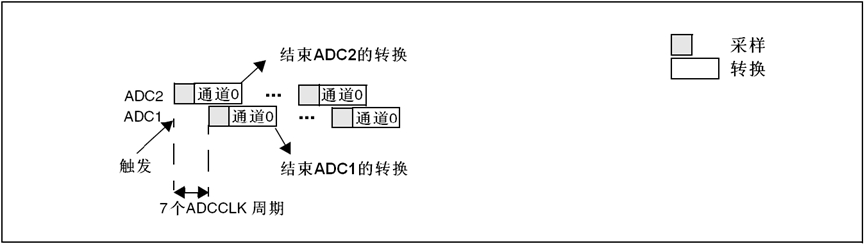

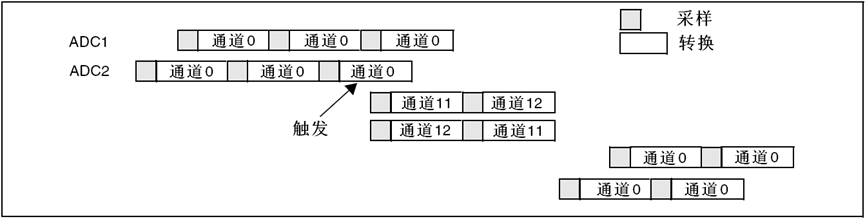

4.3 快速交叉模式

此模式只适用于规则通道组(通常为一个通道)。外部触发来自 ADC1 的规则通道多路开关。外部触发产生后:

ADC2 立即启动并且ADC1 在延迟 7 个 ADC 时钟周期后启动如果同时设置了 ADC1 和 ADC2 的 CONT 位,所选的两个 ADC 规则通道将被连续地转换。ADC1产生一个EOC中断后(由EOCIE使能),产生一个32位的DMA传输请求(如果设置了DMA位),ADC1_DR 寄存器的 32 位数据被传输到 SRAM,ADC1_DR 的上半个字包含 ADC2 的转换数据,低半个字包含 ADC1 的转换数据。

注意: 最大允许采样时间<7 个 ADCCLK 周期,避免 ADC1 和 ADC2 转换相同通道时发生两个采样周期的重叠。

在 1 个通道上连续转换模式下的快速交叉模式

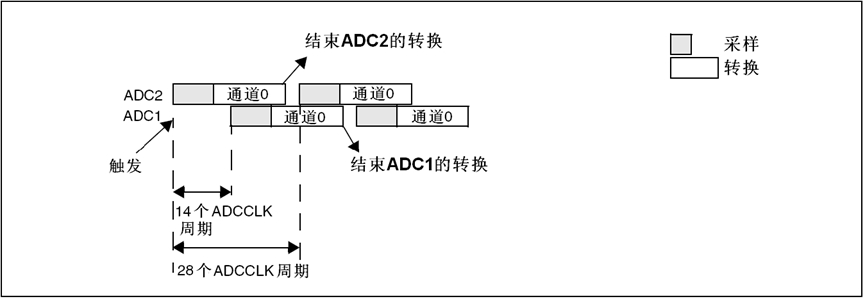

4.4 慢速交叉模式

此模式只适用于规则通道组(只能为一个通道)。外部触发来自 ADC1 的规则通道多路开关。外部触发产生后:

ADC2 立即启动并且 ADC1 在延迟 14 个 ADC 时钟周期后启动在延迟第二次 14 个 ADC 周期后 ADC2 再次启动,如此循环。

注意: 最大允许采样时间<14 个 ADCCLK 周期,以避免和下个转换重叠。ADC1产生一个EOC中断后(由EOCIE使能),产生一个32位的DMA传输请求(如果设置了DMA位),ADC1_DR 寄存器的 32 位数据被传输到 SRAM,ADC1_DR 的上半个字包含 ADC2 的转换数据,低半个字包含 ADC1 的转换数据。在 28 个 ADC 时钟周期后自动启动新的 ADC2 转换。在这个模式下不能设置 CONT 位,因为它将连续转换所选择的规则通道。

注意: 应用程序必须确保当使用交叉模式时,不能有注入通道的外部触发产生。

在 1 个通道上的慢速交叉模式

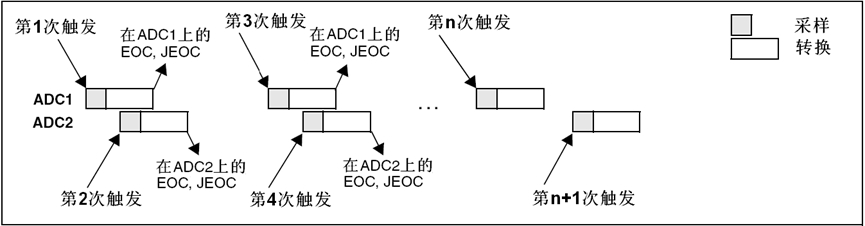

4.5 交替触发模式

此模式只适用于注入通道组。外部触发源来自 ADC1 的注入通道多路开关。

当第一个触发产生时,ADC1 上的所有注入组通道被转换。

当第二个触发到达时,ADC2 上的所有注入组通道被转换。

如此循环……

如果允许产生 JEOC 中断,在所有 ADC1 注入组通道转换后产生一个 JEOC 中断。如果允许产生JEOC 中断,在所有 ADC2 注入组通道转换后产生一个 JEOC 中断。当所有注入组通道都转换完后,如果又有另一个外部触发,交替触发处理从转换 ADC1 注入组通道重新开始。

交替触发:每个 ADC1 的注入通道组

如果 ADC1 和 ADC2 上同时使用了注入间断模式:

当第一个触发产生时,ADC1 上的第一个注入通道被转换。

当第二个触发到达时,ADC2 上的第一个注入通道被转换。

如此循环……

如果允许产生 JEOC 中断,在所有 ADC1 注入组通道转换后产生一个 JEOC 中断。如果允许产生JEOC 中断,在所有 ADC2 注入组通道转换后产生一个 JEOC 中断。

当所有注入组通道都转换完后,如果又有另一个外部触发,则重新开始交替触发过程。

交替触发:在间断模式下每个 ADC 上的 4 个注入通道

4.6 独立模式

此模式里,双 ADC 同步不工作,每个 ADC 接口独立工作。

5 混合的规则

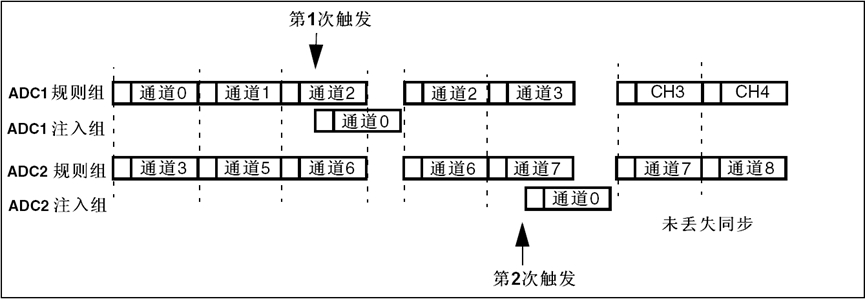

5.1 混合的规则/注入同步模式

规则组同步转换可以被中断,以启动注入组的同步转换。

注: 在混合的规则/注入同步模式中,必须转换具有相同时间长度的序列,或保证触发的间隔比 2 个序列中较长的序列长,否则当较长序列的转换还未完成时,具有较短序列的 ADC 转换可能会被重启。

5.2 混合的同步规则+交替触发模式

规则组同步转换可以被中断,以启动注入组交替触发转换。图 显示了一个规则同步转换被交替触发所中断。注入交替转换在注入事件到达后立即启动。如果规则转换已经在运行,为了在注入转换后确保同步,所有的 ADC(主和从)的规则转换被停止,并在注入转换结束时同步恢复。

注: 在混合的同步规则+交替触发模式中,必须转换具有相同时间长度的序列,或保证触发的间隔比 2个序列中较长的序列长,否则当较长序列的转换还未完成时,具有较短序列的 ADC 转换可能会被重启。

交替+规则同步

如果触发事件发生在一个中断了规则转换的注入转换期间,这个触发事件将被忽略。下图示出了这种情况的操作(第 2 个触发被忽略)。

触发事件发生在注入转换期间

5.3 混合同步注入+交叉模式

一个注入事件可以中断一个交叉转换。这种情况下,交叉转换被中断,注入转换被启动,在注入序列转换结束时,交叉转换被恢复。下图是这种情况的一个例子。

注: 当 ADC 时钟预分频系数设置为 4 时,交叉模式恢复后不会均匀地分配采样时间,采样间隔是 8 个ADC 时钟周期与 6 个 ADC 时钟周期轮替,而不是均匀的 7 个 ADC 时钟周期。

交叉的单通道转换被注入序列 CH11 和 CH12 中断

6 温度传感器

温度传感器可以用来测量器件周围的温度(TA)。

温度传感器在内部和 ADC1_IN16 输入通道相连接,此通道把传感器输出的电压转换成数字值。温度传感器模拟输入推荐采样时间是 17.1μs。当没有被使用时,传感器可以置于关电模式。

注意: 必须设置 TSVREFE 位激活内部通道:ADC1_IN16(温度传感器)和 ADC1_IN17(VREFINT)的转换。温度传感器输出电压随温度线性变化,由于生产过程的变化,温度变化曲线的偏移在不同芯片上会有不同(最多相差 45°C)。

内部温度传感器更适合于检测温度的变化,而不是测量绝对的温度。如果需要测量精确的温度,应该使用一个外置的温度传感器。

温度传感器和 VREFINT 通道框图

读温度

为使用传感器:

1. 选择 ADC1_IN16 输入通道

2. 选择采样时间为 17.1μs

3. 设置 ADC 控制寄存器 2(ADC_CR2)的 TSVREFE 位,以唤醒关电模式下的温度传感器

4. 通过设置 ADON 位启动 ADC 转换(或用外部触发)

5. 读 ADC 数据寄存器上的 VSENSE 数据结果

6. 利用下列公式得出温度

温度(°C)={(V25-VSENSE)/Avg_Slope}+25

这里:

V25=VSENSE 在 25°C 时的数值

Avg_Slope=温度与 VSENSE 曲线的平均斜率(单位为 mV/°C 或μV/°C)参考数据手册的电气

特性章节中 V25 和 Avg_Slope 的实际值。

注意: 传感器从关电模式唤醒后到可以输出正确水平的 VSENSE 前,有一个建立时间。ADC 在上电后也有一个建立时间,因此为了缩短延时,应该同时设置 ADON 和 TSVREFE 位

7 ADC中断

规则和注入组转换结束时能产生中断,当模拟看门狗状态位被设置时也能产生中断。它们都有独立的中断使能位。

注: ADC1 和 ADC2 的中断映射在同一个中断向量上,而 ADC3 的中断有自己的中断向量

ADC_SR 寄存器中有 2 个其他标志,但是它们没有相关联的中断:

JSTRT(注入组通道转换的启动)

STRT(规则组通道转换的启动)

| 中断事件 | 事件标志 | 使能控制位 |

| 规则组转换结束 | EOC | EOCIE |

| 注入组转换结束 | JEOC | JEOCIE |

| 设置了模拟看门狗状态位 | AWD | AWDIE |

8 例程设计

8.1 ADC_AnalogWatchdog例程

1.初始化部分

// 延时函数初始化(由delay.h提供)

delay_init();

// UART配置函数

void UART_Configuration(void)

{

GPIO_InitTypeDef GPIO_InitStructure;

USART_InitTypeDef USART_InitStructure;

// 使能USART1和GPIOA时钟

RCC_APB2PeriphClockCmd(RCC_APB2Periph_USART1 | RCC_APB2Periph_GPIOA, ENABLE);

// 配置TX引脚(PA9)为复用推挽输出

GPIO_InitStructure.GPIO_Pin = GPIO_Pin_9;

GPIO_InitStructure.GPIO_Mode = GPIO_Mode_AF_PP;

GPIO_InitStructure.GPIO_Speed = GPIO_Speed_50MHz;

GPIO_Init(GPIOA, &GPIO_InitStructure);

// 配置RX引脚(PA10)为浮空输入

GPIO_InitStructure.GPIO_Pin = GPIO_Pin_10;

GPIO_InitStructure.GPIO_Mode = GPIO_Mode_IN_FLOATING;

GPIO_Init(GPIOA, &GPIO_InitStructure);

// 配置串口参数:115200bps, 8位数据, 1位停止位, 无校验

USART_InitStructure.USART_BaudRate = 115200;

USART_InitStructure.USART_WordLength = USART_WordLength_8b;

USART_InitStructure.USART_StopBits = USART_StopBits_1;

USART_InitStructure.USART_Parity = USART_Parity_No;

USART_InitStructure.USART_HardwareFlowControl = USART_HardwareFlowControl_None;

USART_InitStructure.USART_Mode = USART_Mode_Rx | USART_Mode_Tx;

USART_Init(USART1, &USART_InitStructure);

USART_Cmd(USART1, ENABLE);

}

// ADC配置函数

void ADC_Configuration(void)

{

ADC_InitTypeDef ADC_InitStructure;

NVIC_InitTypeDef NVIC_InitStructure;

// 使能GPIOA和ADC1时钟

RCC_APB2PeriphClockCmd(RCC_APB2Periph_GPIOA | RCC_APB2Periph_ADC1, ENABLE);

RCC_ADCCLKConfig(RCC_PCLK2_Div8); // ADC时钟=PCLK2/8(假设PCLK2=72MHz,ADC时钟=9MHz)

ADC_DeInit(ADC1); // 复位ADC1配置

// 配置ADC为独立模式,单通道单次转换

ADC_InitStructure.ADC_Mode = ADC_Mode_Independent;

ADC_InitStructure.ADC_ScanConvMode = DISABLE; // 非扫描模式

ADC_InitStructure.ADC_ContinuousConvMode = DISABLE; // 单次转换模式

ADC_InitStructure.ADC_ExternalTrigConv = ADC_ExternalTrigConv_None; // 软件触发

ADC_InitStructure.ADC_DataAlign = ADC_DataAlign_Right; // 右对齐

ADC_InitStructure.ADC_NbrOfChannel = 1; // 转换通道数1

ADC_Init(ADC1, &ADC_InitStructure);

ADC_Cmd(ADC1, ENABLE); // 使能ADC1

// 配置NVIC中断优先级

NVIC_InitStructure.NVIC_IRQChannel = ADC1_2_IRQn;

NVIC_InitStructure.NVIC_IRQChannelPreemptionPriority = 0; // 最高抢占优先级

NVIC_InitStructure.NVIC_IRQChannelSubPriority = 0;

NVIC_InitStructure.NVIC_IRQChannelCmd = ENABLE;

NVIC_Init(&NVIC_InitStructure);

// 配置ADC通道10(PA0),采样时间239.5周期

ADC_RegularChannelConfig(ADC1, ADC_Channel_10, 1, ADC_SampleTime_239Cycles5);

// 配置模拟看门狗:监测通道10,阈值范围1024~2048(对应电压0.825V~1.65V,假设VREF=3.3V)

ADC_AnalogWatchdogSingleChannelConfig(ADC1, ADC_Channel_10);

ADC_AnalogWatchdogThresholdsConfig(ADC1, 2048, 1024);

ADC_AnalogWatchdogCmd(ADC1, ADC_AnalogWatchdog_SingleRegEnable); // 使能单通道看门狗

ADC_ITConfig(ADC1, ADC_IT_AWD, ENABLE); // 使能模拟看门狗中断

// ADC校准(关键步骤,确保转换精度)

ADC_ResetCalibration(ADC1);

while (ADC_GetResetCalibrationStatus(ADC1));

ADC_StartCalibration(ADC1);

while (ADC_GetCalibrationStatus(ADC1));

}

- ⚪延时函数初始化:调用delay_init()函数,为后续的延时操作做准备。

- ⚪UART 配置:UART_Configuration()函数用于配置 USART1,包含使能时钟、设置 GPIO 引脚、初始化串口参数(如波特率、数据位、停止位等),并且使能串口。

- ⚪ADC 配置:ADC_Configuration()函数对 ADC1 进行配置,具体操作有使能时钟、设置 ADC 时钟分频、初始化 ADC 参数(如工作模式、转换模式等)、配置模拟看门狗(设定监测通道和阈值)、使能模拟看门狗中断以及进行 ADC 校准。

2.主循环部分

int main(void)

{

RCC_ClocksTypeDef clocks;

delay_init();

UART_Configuration();

ADC_Configuration();

RCC_GetClocksFreq(&clocks);

// 打印系统时钟信息

printf("n");

printf("SYSCLK: %3.1fMhz, HCLK: %3.1fMhz, PCLK1: %3.1fMhz, PCLK2: %3.1fMhz, ADCCLK: %3.1fMhzn",

(float)clocks.SYSCLK_Frequency / 1000000, (float)clocks.HCLK_Frequency / 1000000,

(float)clocks.PCLK1_Frequency / 1000000, (float)clocks.PCLK2_Frequency / 1000000, (float)clocks.ADCCLK_Frequency / 1000000);

printf("ADC Analog Watchdog Testn");

printf("LTR: 1024, HTR: 2048n");

// 主循环:周期性触发ADC转换

while (1)

{

ADC_SoftwareStartConvCmd(ADC1, ENABLE); // 软件触发ADC转换

delay_ms(200); // 等待转换完成并延时200ms

}

}

在main函数的无限循环里,每隔 200ms 启动一次 ADC 转换。这样做的目的是周期性地对 ADC 通道进行采样。

3.中断处理部分

// 模拟看门狗中断处理函数

void ADC1_2_IRQHandler(void)

{

ADC_ITConfig(ADC1, ADC_IT_AWD, DISABLE); // 临时禁用中断,避免重复触发

if (SET == ADC_GetFlagStatus(ADC1, ADC_FLAG_AWD)) // 检查模拟看门狗标志

{

ADC_ClearFlag(ADC1, ADC_FLAG_AWD); // 清除中断标志

ADC_ClearITPendingBit(ADC1, ADC_IT_AWD); // 清除中断挂起位

// 打印触发中断的ADC值(12位精度,范围0~4095)

printf("ADC Awd is Happened. Code Value = %d rn", ADC1- >DR);

}

ADC_ITConfig(ADC1, ADC_IT_AWD, ENABLE); // 重新使能中断

}

ADC1_2_IRQHandler函数作为模拟看门狗中断的处理函数。当 ADC 值超出预设的阈值范围时,会触发该中断。在中断处理过程中,先禁用中断,接着清除中断标志和挂起位,然后打印出触发中断时的 ADC 值,最后重新使能中断。

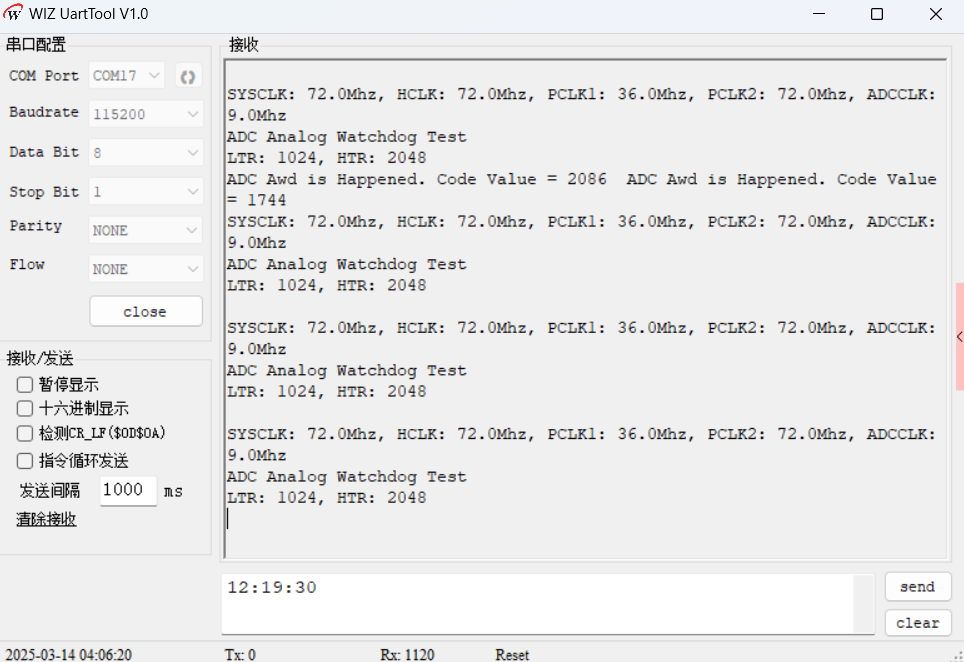

9 下载验证

9.1 ADC_AnalogWatchdog例程

实验现象分析

系统启动信息: 系统启动后,会在串口输出系统时钟频率信息,同时显示正在进行 ADC 模拟看门狗测试以及预设的下限和上限。

ADC 转换: 系统会每隔 200ms 启动一次 ADC 转换。若输入到 ADC 通道 10 的电压值处于 1024 - 2048 的范围内,不会有额外信息输出。

模拟看门狗触发:当输入到 ADC 通道 10 的电压值超出 1024 - 2048 的范围时,会触发模拟看门狗中断,在串口输出触发中断时的 ADC 值。

持续运行: 系统会持续运行,不断进行 ADC 转换,并在需要时触发模拟看门狗中断。

WIZnet 是一家无晶圆厂半导体公司,成立于 1998 年。产品包括互联网处理器 iMCU™,它采用 TOE(TCP/IP 卸载引擎)技术,基于独特的专利全硬连线 TCP/IP。iMCU™ 面向各种应用中的嵌入式互联网设备。

WIZnet 在全球拥有 70 多家分销商,在香港、韩国、美国设有办事处,提供技术支持和产品营销。

香港办事处管理的区域包括:澳大利亚、印度、土耳其、亚洲(韩国和日本除外)。

-

一文读懂:W55MH32 如何携手微信小程序与 OneNET,实现以太网灯条调色自由(软硬件开源)2025-08-08 1809

-

第十四章 W55MH32 TFTP示例2025-07-24 1289

-

第十四章 USART——串口通讯2025-06-14 2037

-

第十四章 ADC(下篇)2025-05-29 1118

-

WIZnet W55MH32以太网单片机开发教程 第十一章 通用定时器(上篇)2025-05-28 1218

-

W55MH32高性能以太网单片机教程 第九章 窗口看门狗(WWDG)2025-05-27 1065

-

第一章 W55MH32 高性能以太网单片机的学习方法概述2025-05-26 1084

-

WIZnet高性能以太网单片机W55MH32重磅发布!2025-05-07 1979

-

基于AVR高性能单片机的以太网接口设计2009-12-30 827

全部0条评论

快来发表一下你的评论吧 !