LVDS、PECL和CML输出/入结构介绍

电子说

描述

1. PECL接口

PECL 由ECL 标准发展而来,但在PECL 电路中使用的是正电源。PECL 信号的摆幅相对ECL 要小,这使得该逻辑更适合于高速数据的串行或并行连接。PECL 标准最初由Motorola 公司提出,经过很长一段时间才在电子工业领域推广开。

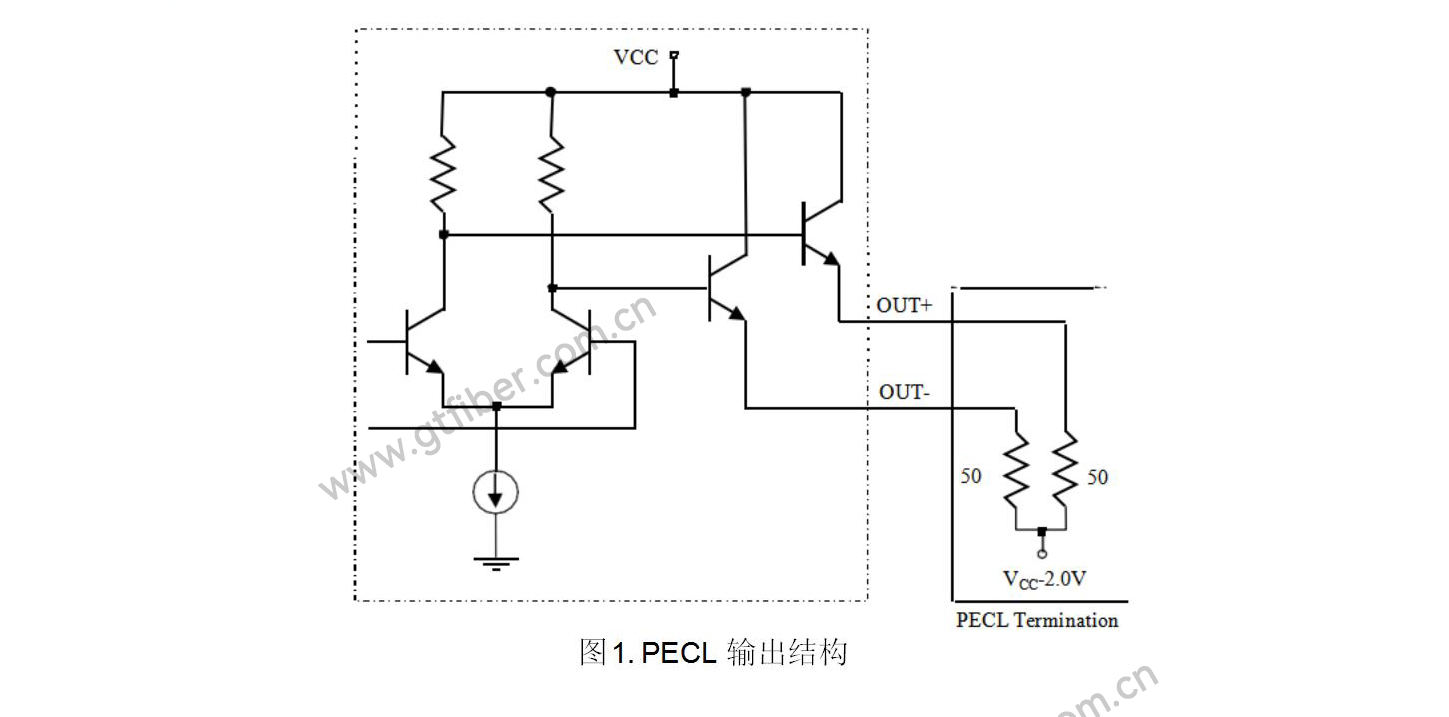

1.1 PECL输出结构

PECL 电路的输出结构如图1 所示,包含一个差分对管和一对射随器。输出射随器工作在正电源范围内,其直流电流始终存在,这样有利于提高开关速度,保持较快的关断时间。PECL 输出的适当端接是连接50Ω 电阻至(VCC-2V)电平。在这种端接条件下,OUT+与OUT-的典型值为(VCC-1.3V),输出直流电流约为14mA。PECL 结构的输出阻抗很低,典型值约为(4-5)Ω,这表明它有很强的驱动能力。但当负载与PECL 的输出端之间有一段传输线时,低阻抗造成的背向端接失配将导致信号的高频失真。

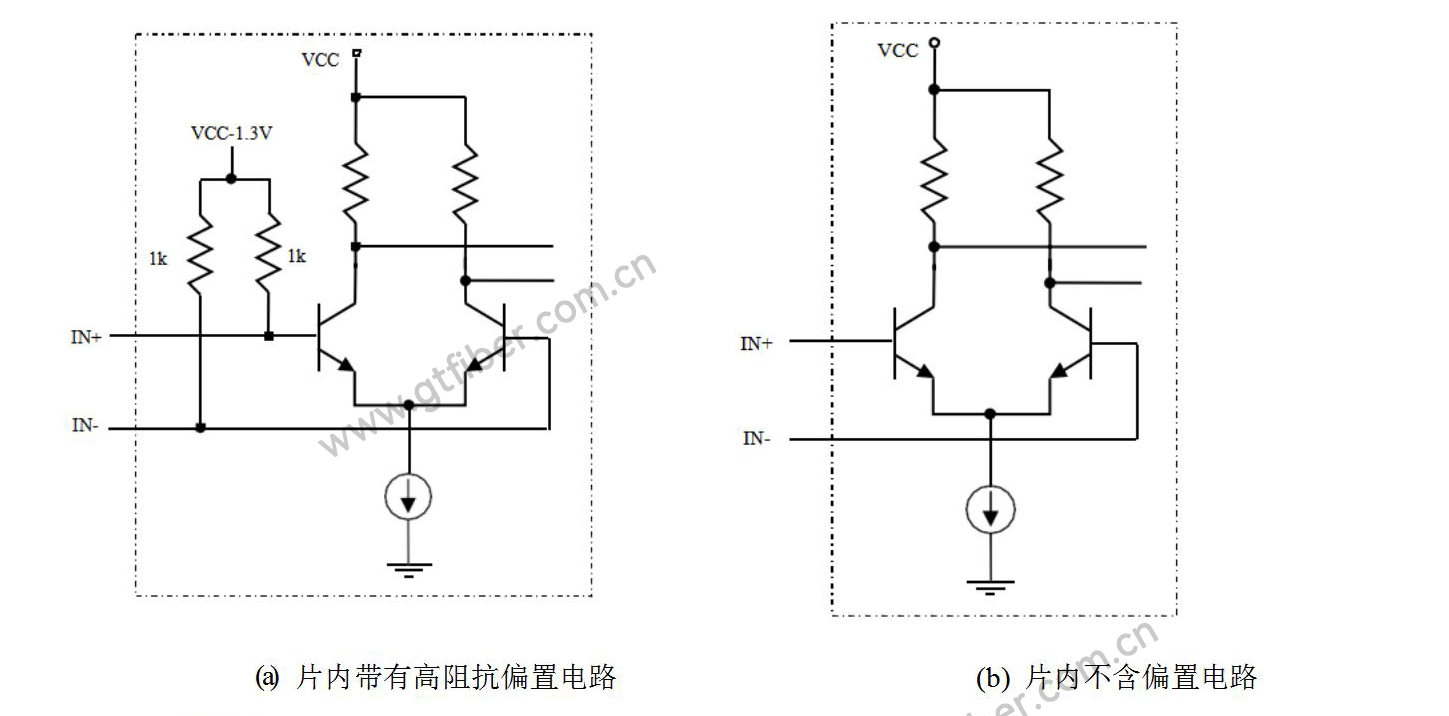

1.2 PECL输入结构

PECL 输入结构如图2 所示,它是一个具有高输入阻抗的差分对。该差分对共模输入电压需偏置到(VCC-1.3V),这样允许的输入信号电平动态范围最大。

2.CML接口

CML 是所有高速数据接口形式中最简单的一种,片内输入与输出端接减少了设置工作条件所需的外围器件数量。CML 输出所提供的信号摆幅较小,从而功耗更低。此外,50Ω 背向终端匹配减小了背向反射,从而降低了高频失真。

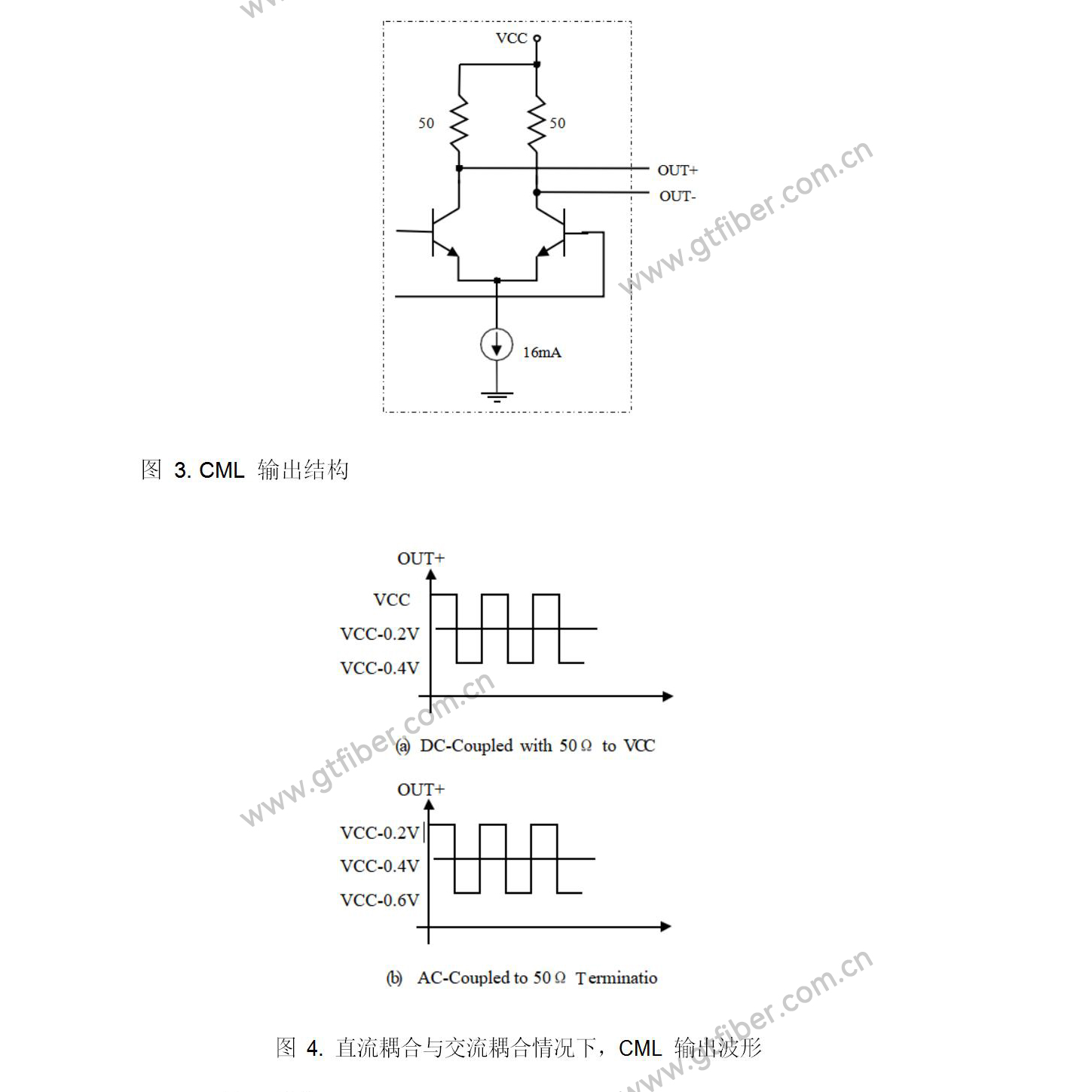

2.1 CML输出结构

CML 的输出电路形式是一个差分对管,该差分对的集电极电阻为50Ω,如图3 所示。输出信号的高低电平切换是靠共发射极差分对管的开关控制的。假定电流源的典型值为16mA,CML 输出负载为上拉至VCC的50Ω 电阻,则单端CML 输出信号的摆幅为VCC至(VCC-0.4V)。在这种情况下,CML 差分输出信号摆幅典型值为800mV,共模电压为(VCC-0.2V)。对同一个电流源来说,若CML 输出采用交流耦合至50Ω 负载,这时的直流阻抗由50Ω 集电极电阻决定。CML 输出共模电压变为(VCC-0.4V) ,差分信号摆幅仍为800mV PP 。在交流和直流耦合情况下输出波形如图4 所示。

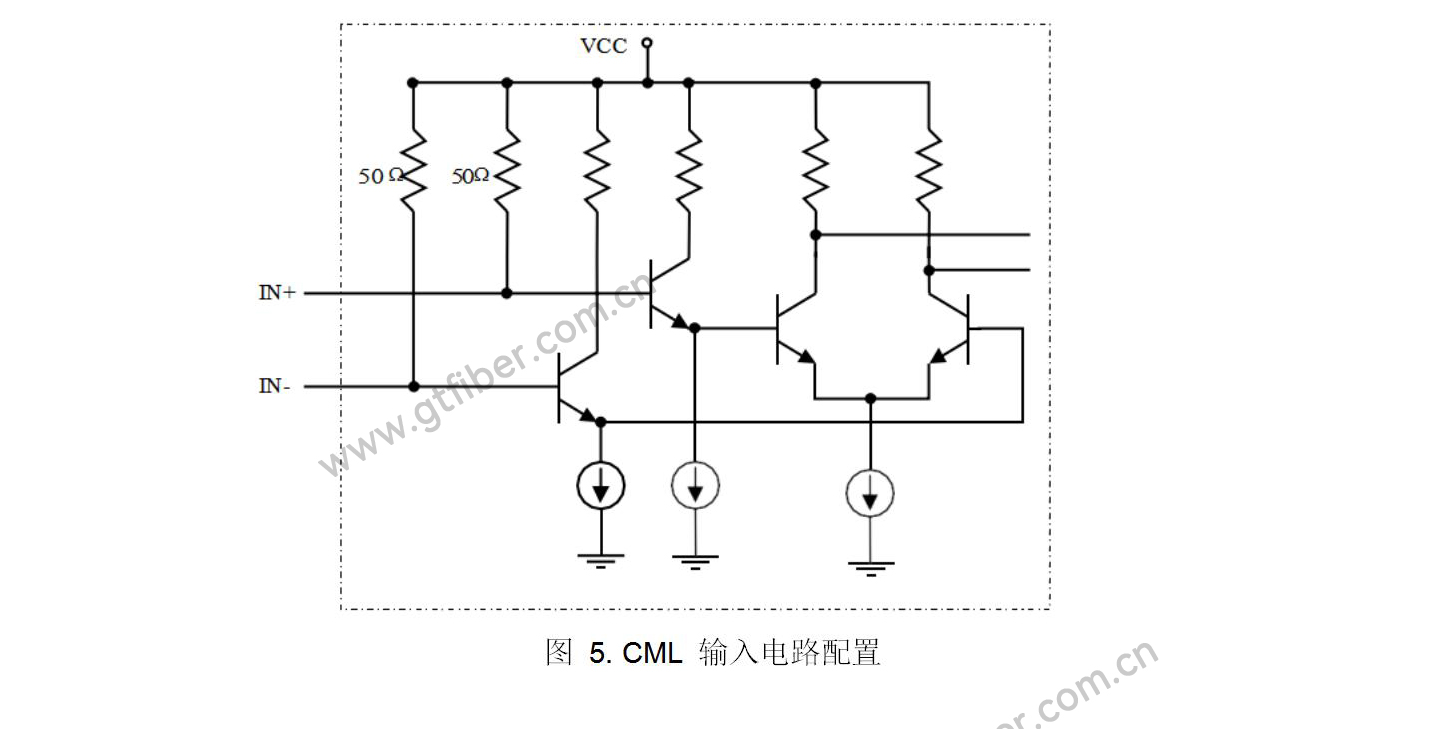

2.2 CML输入结构

CML 输入结构有几个重要特点,这也使它在高速数据传输中成为常用的方式。如图5 。

图5. CML 输入电路配置

3. LVDS****接口

LVDS 用于低压差分信号点到点的传输,该方式有若干优势,使其更具有吸引力。较小的信号摆幅使得功耗较低,一般负载阻抗为100Ω 的差分线上的电流不超过4mA。这一特征使得LVDS 适合做并行数据传输。此外信号的电平很低,从而使得该结构可以在2.5V 的低电压下工作。LVDS 输入信号电压可以从0V 到2.4V 变化,单端信号摆幅为400mV,这样允许输入共模电压从0.2V 到2.2V 范围内变化,也就是说LVDS 允许驱动器和接收器两端地电势有±1V 的落差。

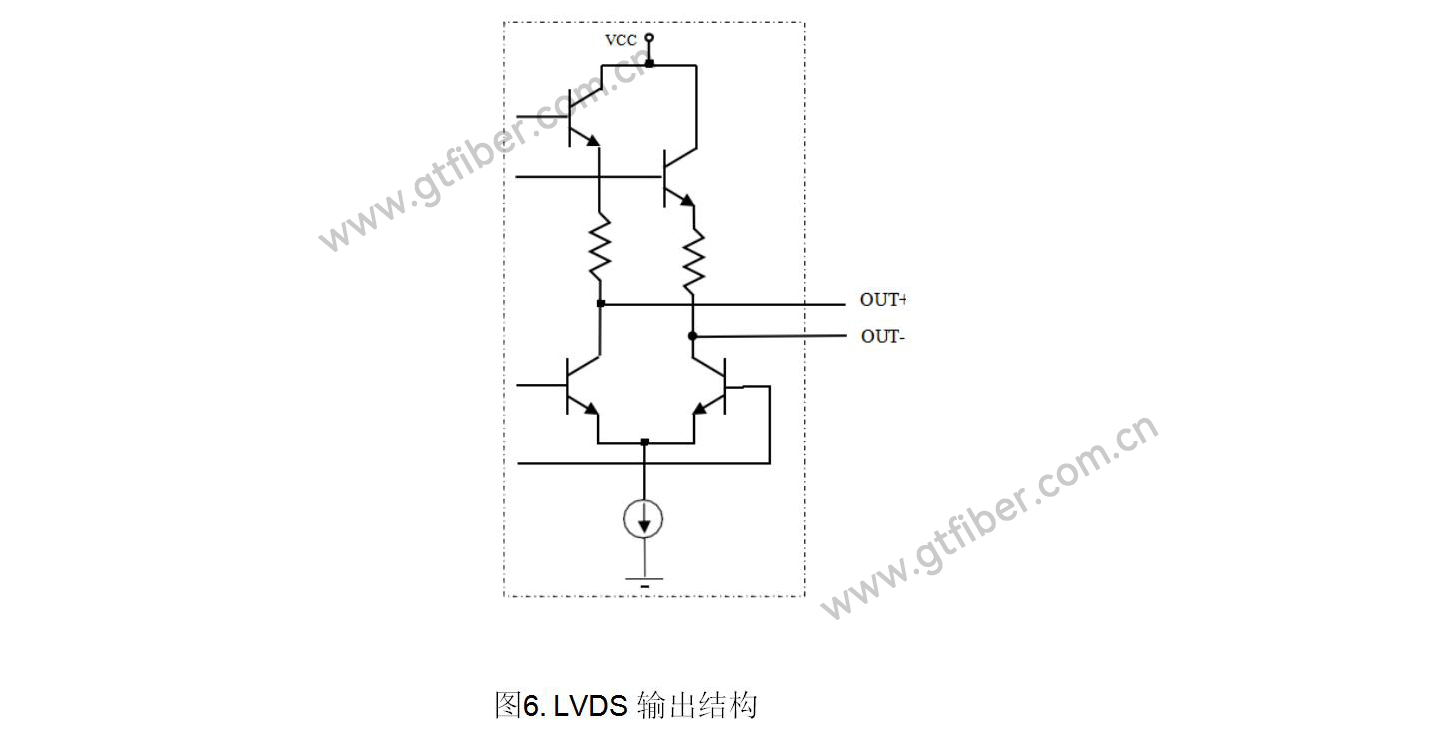

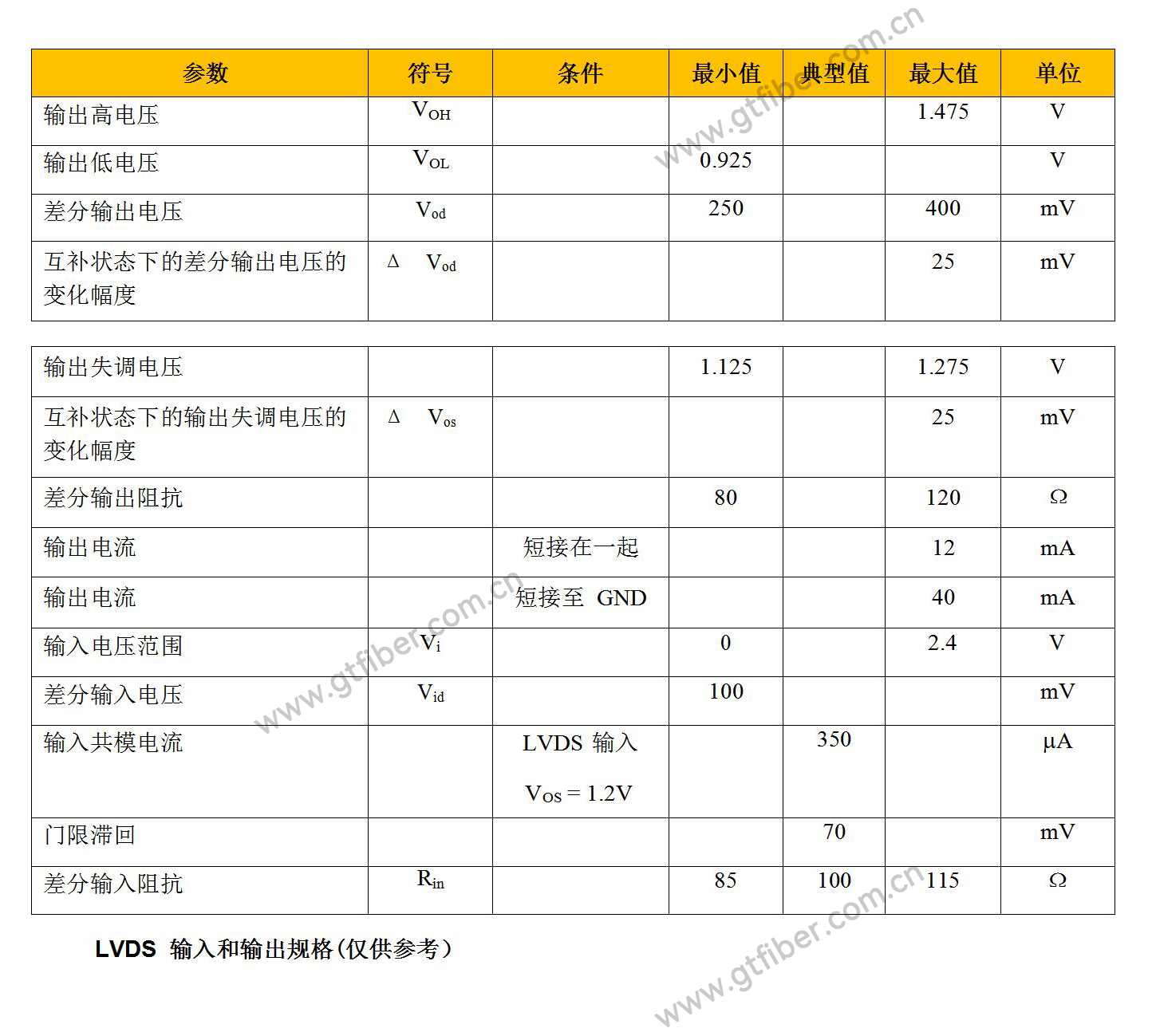

3.1 LVDS输出结构

电路如图6 所示。电路差分输出阻抗典型值为100Ω,表III 列出了其它一些输出指标。

图6. LVDS 输出结构

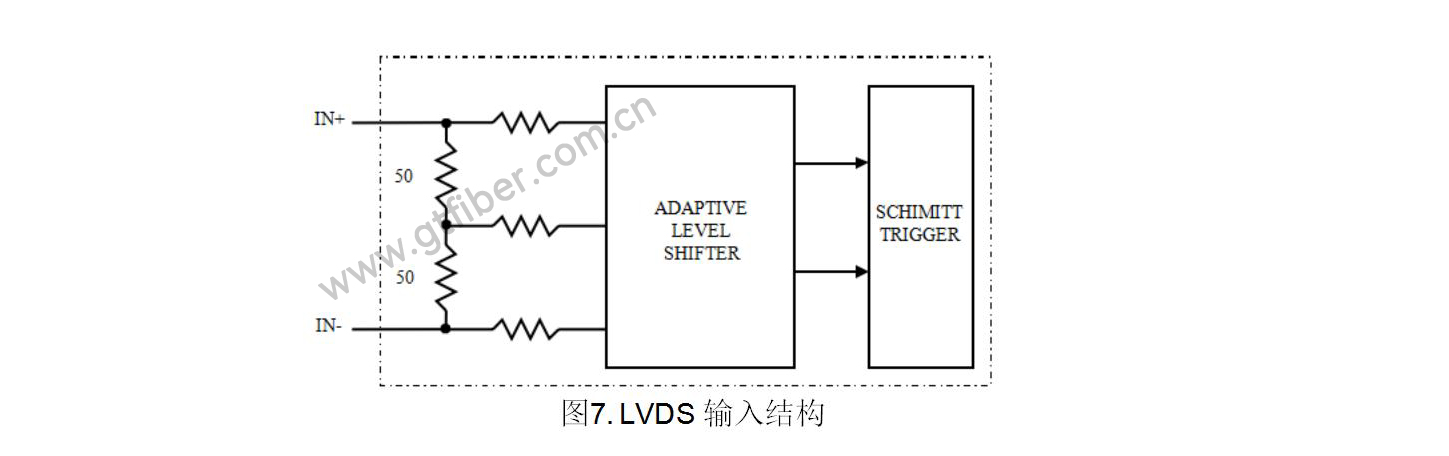

3.2 LVDS输入结构

LVDS 输入结构如图7 所示,IN+与IN-输入差分阻抗为100Ω。为适应共模电压宽范围内的变化,输入级还包括一个自适应电平转换电路,该电路将共模电压设置为一固定值,该电路后面是一个施密特触发器。施密特触发器的输入门限具有滞回特性,触发器后级是差分放大器。

-

LVPECL 与 LVDS 及 PECL 与 LVDS 的互连技术解析2025-08-08 1051

-

SN65CML100D 1.5 Gbps LVDS/LVPECL/CML-TO-CML转换器/中继器数据表2024-06-27 467

-

PECL、LVECL、CML、LVDS接口原理与应用2024-03-07 733

-

如何在LVPECL、VML、CML、LVDS和子LVDS接口之间转换2022-11-21 1065

-

获得连接:LVPECL、VML、CML、LVDS 与子 LVDS 之间的接口连接2022-11-04 764

-

差分逻辑电平,LVDS、xECL、CML、HCSL/LPHCSL、TMDS等2021-07-17 6214

-

详解信号逻辑电平标准:CMOS、TTL、LVCMOS、LVTTL、ECL、PECL、LVPECL、LVDS、CML资料下载2021-04-09 6324

-

浅谈LVDS、CML、LVPECL三种差分逻辑电平之间的互连2020-12-20 41042

-

LVPECL、VML、CML、LVDS 与LVDS之间的接口连接转换2018-09-13 15174

-

LVDS|PECL|CML2010-04-10 538

-

LVDS用户手册-包含高速CML和信号调理内容2009-10-22 4132

-

lvds是什么意思?2009-05-01 11072

-

LVDS分离器简化高速信号分配2009-04-24 1250

-

PTN3310 and PTN3311 LVDS-PECL2009-03-30 634

全部0条评论

快来发表一下你的评论吧 !