化合物半导体器件的定义和制造工艺

描述

文章来源:学习那些事

原文作者:小陈婆婆

本文介绍了化合物半导体器件的定义和工艺。

化合物半导体器件与集成技术

化合物半导体器件以Ⅲ-Ⅴ族、Ⅱ-Ⅵ族元素通过共价键形成的材料为基础,展现出独特的电学与光学特性。以砷化镓(GaAs)为例,其电子迁移率高达8500cm²/V·s,本征电阻率达10⁹Ω·cm,是制造高速、高频、抗辐射器件的理想材料。

通过材料生长与调控技术,如液相外延(LPE)、气相外延(VPE)、金属有机物化学气相沉积(MOCVD)和分子束外延(MBE),可实现能带结构的精确裁剪,形成异质结、超晶格等量子结构,为器件性能突破提供物理基础,本文分述如下:

- 化合物半导体器件中的特殊概念

- 化合物MESFET及集成工艺

- HEMT及制造工艺

- 化合物半导体HBT及制造工艺

化合物半导体器件中的特殊概念

异质结是化合物半导体器件的核心创新点。通过不同禁带宽度材料的组合,形成能带势垒或势阱,显著影响载流子输运。例如,在GaAs/AlGaAs异质结中,导带阶差ΔEc与价带阶差ΔEv的比值约为0.6-0.7,形成天然量子阱,束缚电子形成二维电子气(2DEG),迁移率可达10⁵cm²/V·s(液氦温度)。

异质结的势垒形态(方形、三角形、梯形)通过量子隧穿效应调控电流,是实现高频、高速器件的关键。

方形势垒(Abrupt Heterojunction)

形成条件:组分突变界面(如GaAs/AlGaAs)

隧穿特性:隧穿概率与势垒高度呈指数关系,适用于共振隧穿二极管(RTD)

典型应用:超高速数字电路(开关时间<1ps)

三角形势垒(Graded Heterojunction)

形成条件:组分渐变界面(如InGaAs/InP)

输运机制:热电子发射主导,适合制作异质结双极晶体管(HBT)基区

优势特征:基区渡越时间缩短至10⁻¹²s量级

梯形势垒(Digital Alloy)

结构特点:超晶格周期结构(如GaAs/AlAs多层膜)

量子效应:产生迷你带(Miniband)输运,实现负微分电阻特性

器件应用:量子阱红外探测器(QWIP),响应波长8-12μm

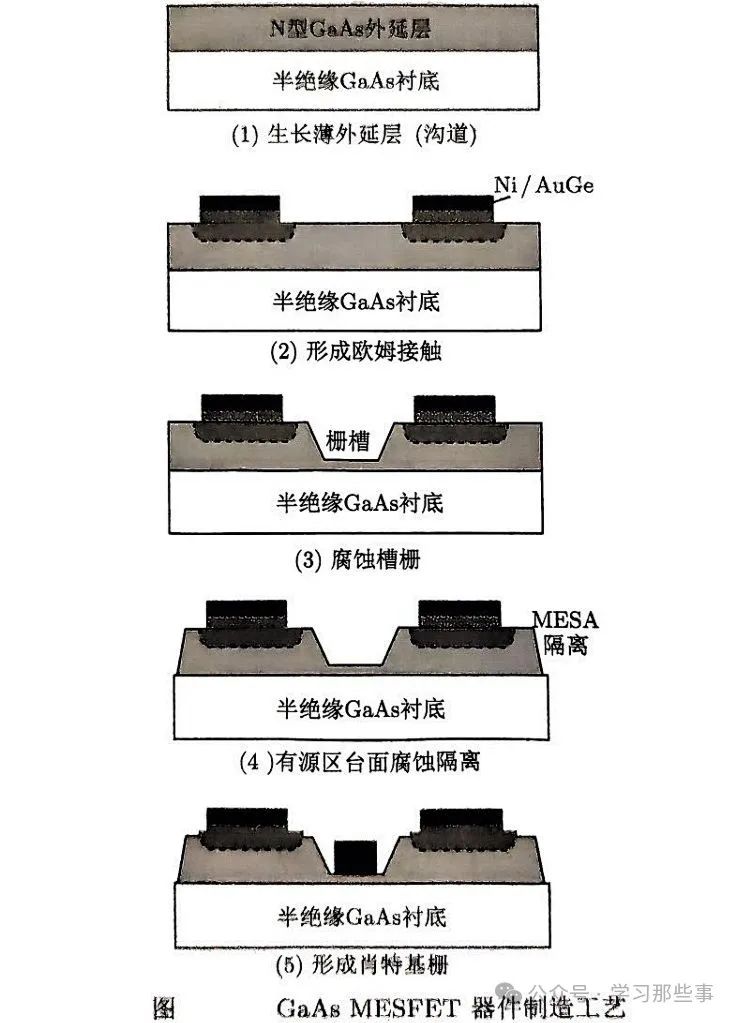

化合物MESFET及集成工艺

金属-半导体场效应晶体管(MESFET)利用肖特基势垒控制沟道载流子耗尽。GaAs MESFET通过槽栅工艺控制沟道剩余厚度,调节夹断电压(Vp),实现增强型(Vp>0)与耗尽型(Vp<0)器件。

其集成工艺包括:

外延生长:在半绝缘GaAs衬底上生长N型GaAs沟道层(MOCVD或MBE)。

源漏欧姆接触:采用AuGe/Ni/Au合金化,接触电阻<5×10⁻⁶Ω·cm²。

槽栅刻蚀:湿法腐蚀控制剩余沟道厚度(50nm),精度<5nm。

隔离工艺:离子注入形成高阻隔离区(电阻率>10⁶Ω·cm)。

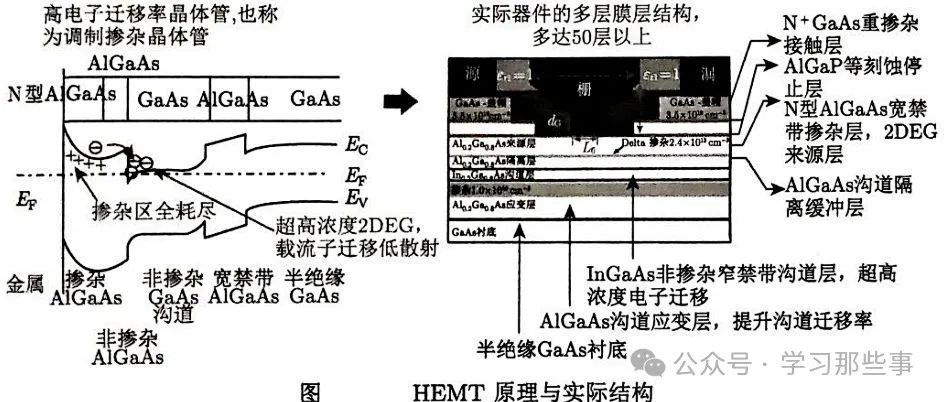

HEMT及制造工艺

高电子迁移率晶体管(HEMT)通过异质结能带工程实现2DEG的高密度输运。

其结构包括:

HJFET:插入宽禁带AlGaAs缓冲层,降低衬底漏电。

MODFET:非掺杂i-GaAs沟道与δ掺杂n⁺-AlGaAs供体层组合,形成2DEG密度3×10¹²cm⁻²。

pHEMT:引入InGaAs赝晶沟道与Delta掺杂,2DEG密度提升至5×10¹²cm⁻²,迁移率突破10⁵cm²/V·s。

制造工艺关键步骤:

MBE外延:层结构精度<0.1nm,组分波动<0.5%。

台面隔离:重离子注入(如B ^+^ ),隔离电阻>10⁷Ω。

源漏接触:AuGe/Ni/Au合金化,接触电阻0.08Ω·mm。

槽栅工艺:H3PO4基湿法腐蚀,栅长定义分辨率30nm。

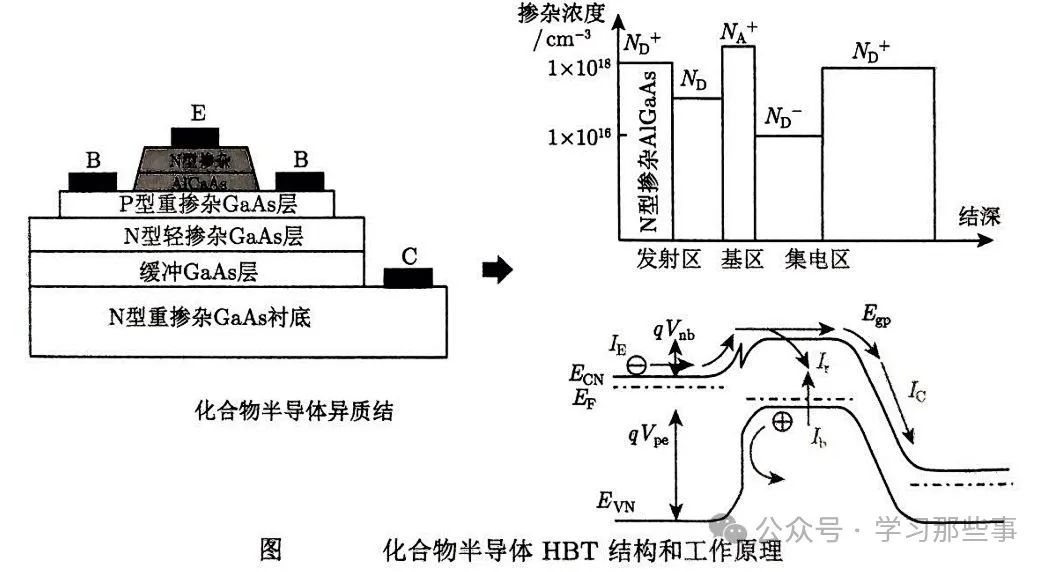

化合物半导体HBT及制造工艺

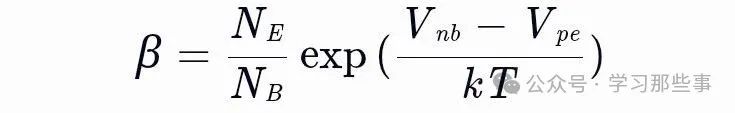

异质结双极晶体管(HBT)通过非对称能带结构提升电流增益。

其核心公式为:

其中,基区掺杂浓度NB可高达1×10²⁰cm⁻³,显著降低基区电阻。制造工艺包括:

外延生长:InGaP/GaAs体系,界面粗糙度<0.5nm。

台面隔离:重离子注入(如B ^+^ ),剂量5×10¹³cm⁻²。

基区接触:Pt/Ti/Au多层金属,接触电阻0.1Ω·mm。

发射极金属化:AuGe/Ni/Au合金化,肖特基势垒高度0.8eV。

-

半导体制造工艺之BiCMOS技术2022-09-22 4610

-

华林科纳的化合物半导体异质集成2023-08-14 1506

-

详解:半导体的定义及分类2016-11-27 8439

-

5G和电动车的兴起让化合物半导体成为新贵2019-05-06 1191

-

浅析化合物半导体技术2019-06-13 6157

-

适合用于射频、微波等高频电路的半导体材料及工艺情况介绍2019-06-27 6202

-

主流的射频半导体制造工艺介绍2019-07-29 3958

-

III-V族化合物,III-V族化合物是什么意思2010-03-04 4464

-

我国应把握5G 机遇,加速提升化合物半导体产业竞争力2018-01-13 4043

-

一文解读化合物半导体产业发展形势及前景2018-10-05 20609

-

化合物半导体应用前景及最新应用2018-11-20 19566

-

从英国化合物半导体中心看化合物半导体集群2019-04-11 6580

-

国内化合物半导体集成电路市场前景分析2020-08-19 4661

-

化合物半导体电子器件研究与进展2022-01-04 3638

-

2021年化合物半导体行业深度报告.zip2023-01-13 617

全部0条评论

快来发表一下你的评论吧 !