Allegro Skill布线功能-添加差分过孔禁布区

Allegro

7人已加入

描述

在高速PCB设计中,差分过孔之间设置禁止布线区域具有重要意义。首先它能有效减少其他信号线对差分信号的串扰,保持差分对的信号完整性。其次禁止布线区域有助于维持差分对的对称性,确保信号传输的平衡性。此外它还能优化差分信号的回流路径,降低过孔寄生效应,减少信号反射和阻抗不连续性。通过这些措施,差分信号的传输质量得以提升,从而满足高速信号传输的要求。

那么可以通过FanySkill中“布线功能-添加差分过孔禁布区”的功能快速实现其效果,以下为具体的功能操作教程。

1、执行菜单命令“FanySkill-布线-差分过孔禁布区”选项如下图1所示,或者在command对话框内输入“DVAP”快捷命令如下图2所示,都可激活添加差分过孔禁布区的功能命令。

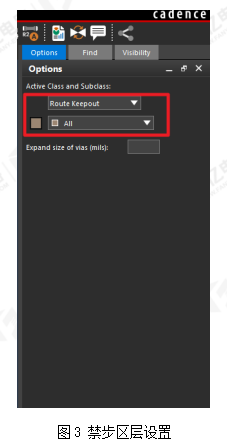

2、差分过孔禁布区命令激活后,打开“Options”参数面板,将“Active Class and Subclass”选项设置“Route Keepout”层,并且其下栏设置“All”如下图3所示,其含义为此禁步区在所有层有效。

3、“Options”参数面板中的“Expand size of vias(mils)”选项其含义为此禁步区的大小对比于过孔需要外扩多少的设置;此处推荐设置为10MIL如下图4所示,具体参数大小可按照自己的设计需求进行设置即可。

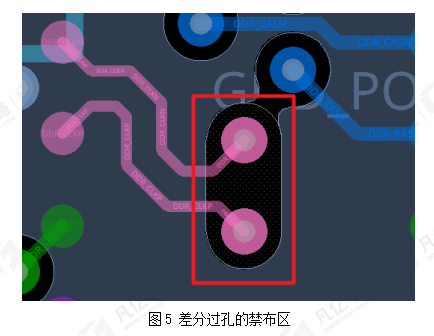

4、“Options”参数面板设置完成之后,光标点击需要设置禁步区的差分信号过孔,即可按照设置的参数大小自动在差分过孔之间形成禁布区域,如下图5所示。

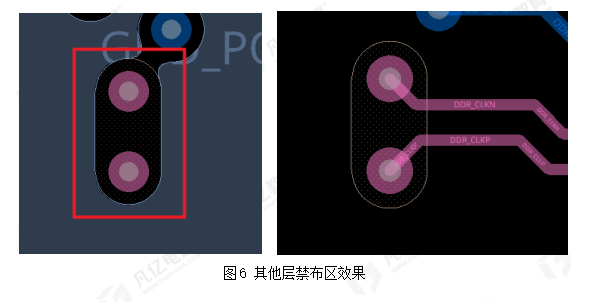

5、其他各个层的禁布区效果如下图6所示。

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

-

Allegro Skill布线功能之删除Dangling介绍2025-06-25 2582

-

Allegro Skill布线功能--过孔助手2025-06-22 2439

-

Allegro Skill布线功能-改变过孔网络介绍与演示2025-05-28 1961

-

Allegro Skill封装功能之添加禁布区介绍2025-04-07 1786

-

Cadence Allegro PCB过孔添加与设置2023-04-12 31452

-

在Allegro中如何进行skill的安装2022-10-17 6672

-

高速差分过孔产生的串扰情况仿真分析2020-08-04 5085

-

分享《YEPEDA allegro skill软件功能简介大全》pdf2019-02-28 4643

-

YEPEDA allegro skill免费学习版共享2018-09-29 11788

-

高速差分过孔之间的串扰分析及优化2018-09-04 3198

-

PCB allegro中如何替换部分过孔,或全局的过孔。2018-08-07 2634

-

高速差分过孔之间的串扰仿真分析2018-03-20 1869

-

高速差分过孔之间的串扰分析2015-12-18 5049

-

高速差分过孔的仿真分析2012-01-16 1565

全部0条评论

快来发表一下你的评论吧 !