MAX9265 HDCP吉比特多媒体串行链路串行器,带有LVDS系统接口技术手册

描述

概述

MAX9265吉比特多媒体串行链路(GMSL)串行器具有LVDS系统接口和宽带数字内容保护(HDCP)加密,用于DVD和Blu-ray™视频及音频数据的内容保护。串行器可配合任何HDCP GMSL解串器,构成数字串行链路,用于传输控制数据和HDCP加密视频及音频数据。GMSL是经过Digital Content Protection (DCP),LLC认证的HDCP技术。

数据表:*附件:MAX9265 HDCP吉比特多媒体串行链路串行器,带有LVDS系统接口技术手册.pdf

3通道模式下,对3路LVDS数据(21位)、UART控制信号和3路音频输入进行串行处理。4通道模式下,对4路LVDS数据(28位)、UART控制信号、3路音频输入以及辅助控制输入进行串行处理。3路输入用于I²S音频,支持8kHz至192kHz采样率,4位至32位采样深度。内嵌控制通道在串行器和解串器之间形成9.6kbps至1Mbps全双工、差分UART链路。电子控制单元(ECU)或微控制器(µC)可位于链路的串行器侧(通常用于视频显示)、链路的解串器侧(通常用于图像检测),或两侧。控制通道使能远端外设的ECU/µC控制,例如背光控制、触摸屏,并执行HDCP的相关操作。

串行链路信号为交流耦合的CML,8b/10b编码。为了驱动更长电缆,串行器提供可编程驱动器预加重/去加重;为了降低EMI,在串行输出提供可编程扩频功能。串行输出满足ISO 10605和IEC 61000-4-2 ESD标准。

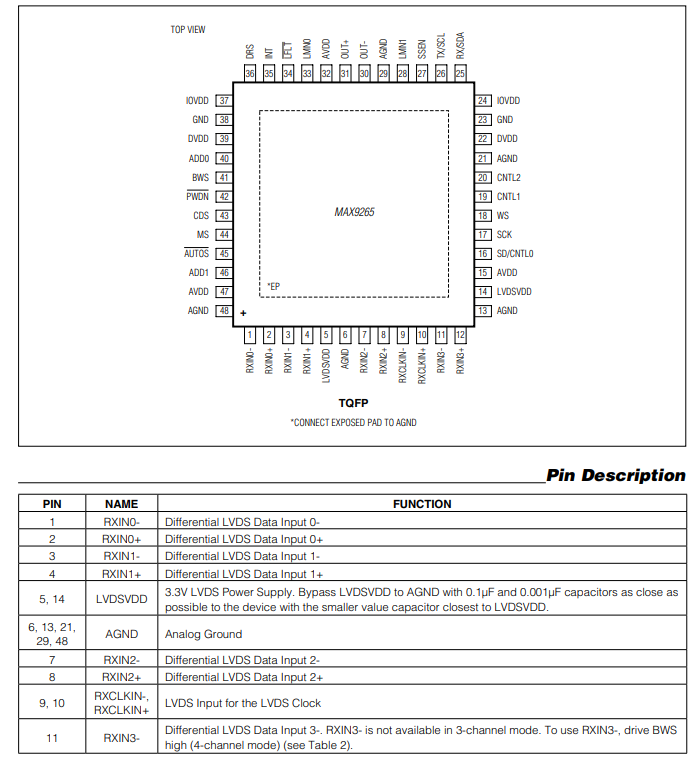

串行器采用1.8V主电源、1.8V至3.3V I/O电源,以及3.3V LVDS电源。器件提供48引脚、TQFP封装,带裸焊盘,工作在-40°C至+105°C汽车级温度范围。

应用

- 高分辨率汽车导航

- 兆像素照相系统

- 后排座信息终端

特性

- 可配合任何GMSL解串器使用

- 通过控制通道设置HDCP加密使能/禁用

- 控制信号处理所有HDCP协议事务—无需独立的控制总线

- HDCP密钥设置在非易失安全存储器

- 2.5Gbps净荷数据率(额定3.125Gbps)

- 交流耦合串行链路,带有8b/10b行编码

- 8.33MHz至104MHz (3通道LVDS)或6.25MHz至78MHz (4通道LVDS)像素时钟

- 4位至32位采样深度,8kHz至192kHz I²S音频通道支持高清音频

- 内置半/全双工双向控制通道

- 基本模式:9.6kbps至1Mbps

- 旁路模式:9.6kbps至1Mbps

- 两个3电平输入,提供9个从地址

- 中断支持触摸显示屏

- 远端I²C主机控制外设

- 可编程预加重/去加重

- 串行链路和解串器输出提供可编程扩频,降低EMI

- 自动数据率检测功能,允许“实时”改变数据率

- LVDS时钟输入可旁路PLL,用于衰减抖动

- 内置PRBS发生器,用于串行链路的BER测试

- 可检测串行链路对地、对电池短路以及开路故障

- ISO 10605和IEC 61000-4-2 ESD保护

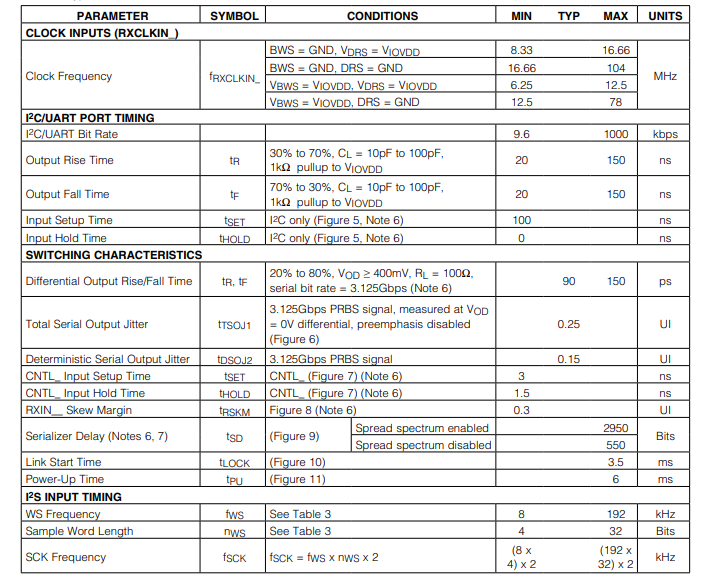

交流电气特性

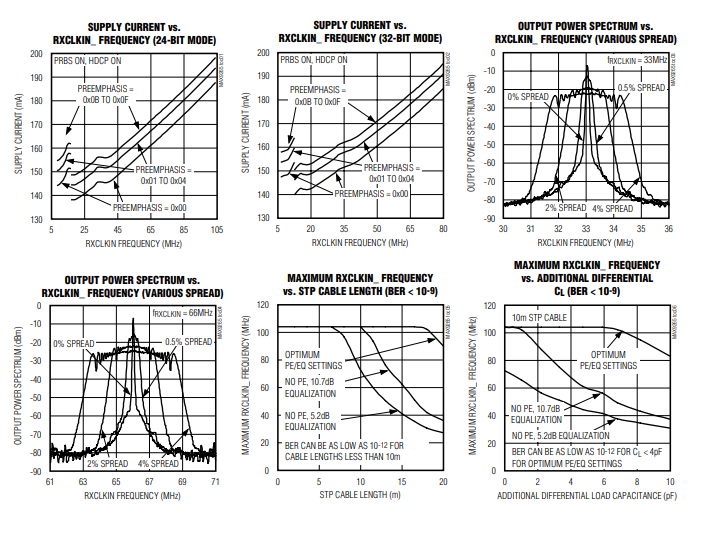

典型操作特性

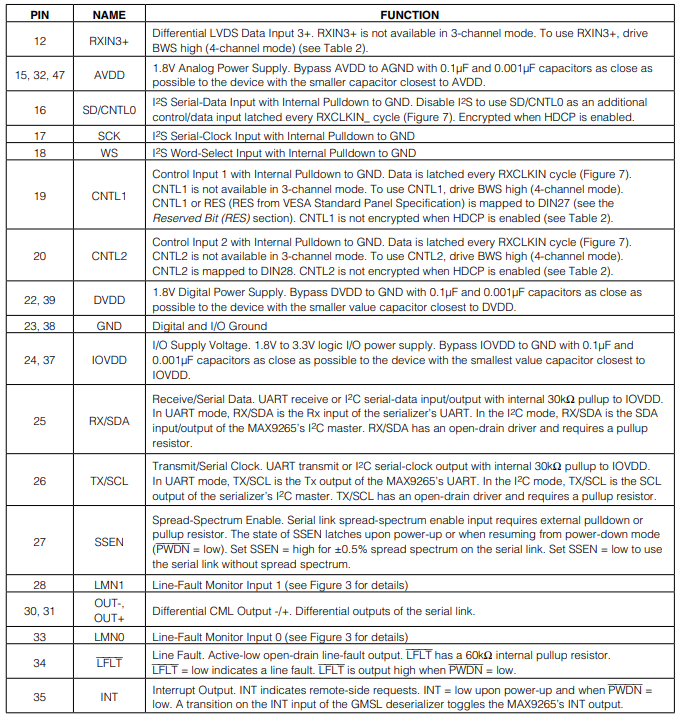

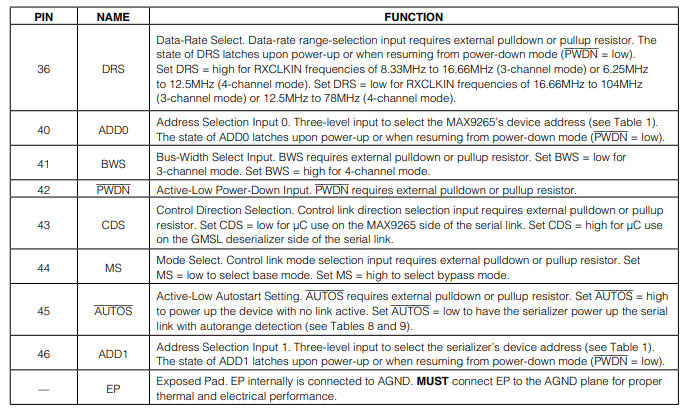

引脚配置描述

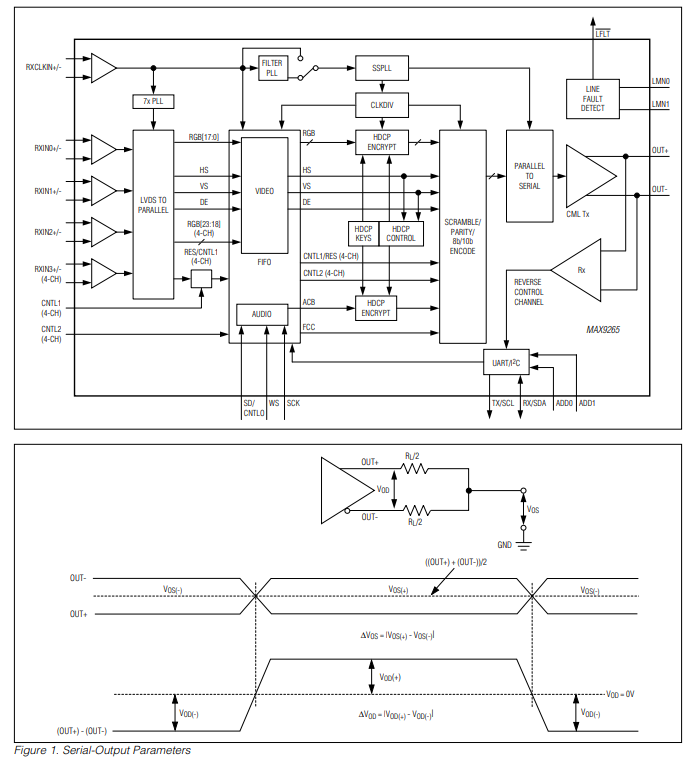

框图

详细说明

MAX9265是一款带有LVDS接口的GMSL序列化器,采用美信的GMSL技术以及HDCP技术。启用HDCP后,该序列化器会对串行链路上的视频和音频数据进行加密。禁用HDCP时,该序列化器与MAX9249 LVDS输入序列化器向后兼容。

对于15米或更长的屏蔽双绞线(STP)电缆,序列化器的最大串行净荷数据速率为2.5Gbps。序列化器的输入时钟在3通道模式下最高可达104MHz,在4通道模式下最高可达78MHz。此串行链路支持从QVGA(320 x 240)到WXGA(1280 x 800)及更高分辨率(24比特颜色深度)的多种显示面板。

3通道模式处理三条LVDS数据线(21比特)、UART控制信号以及三条音频信号。4通道模式处理四条LVDS数据线(28比特)、UART控制信号、四条音频信号以及两个辅助并行输入。这三个音频输入构成一个标准I²S接口,支持8kHz至192kHz的采样率,音频字长为4至32比特。

嵌入式控制通道采用全双工、差分9.6kbps至1Mbps UART链路连接序列化器和解序列化器,用于与HDCP相关的控制操作。此外,在控制通道中,电子控制单元(ECU)或微控制器(μC)能够远程控制外设,如背光控制、图形伽马校正、相机模块和触摸屏。ECU/μC可以位于链路的序列化器端(典型用于视频显示)、GMSL解序列化器端(典型用于图像传感),或在两端都有。基本模式通信使用I²C或GMSL UART格式与外设进行通信。旁路模式使用自定义UART格式实现全双工通信。

序列化器的预加重/去加重功能,结合GMSL解序列化器的通道均衡功能,可延长链路长度并增强链路可靠性。扩频时钟可用于降低串行输出上的电磁干扰(EMI)。CML和LVDS连接符合ISO 10605和IEC 61000 - 4 - 2 ESD保护标准。

寄存器映射

微控制器通过内部寄存器配置GMSL序列化器和解序列化器的各种工作条件。设备地址存储在寄存器0x00和0x01中。要写入序列化器或GMSL解序列化器的寄存器0x00和0x01,或更改设备地址,都需要先发送设备地址。

HDCP位图和总线宽度选择

LVDS输入有两种可选模式:3通道模式和4通道模式。在3通道模式下,RXIN3未使用。两种模式下,SD/CNTL0、SCK和WS引脚都用于I²S音频。串行器时钟(RXCLKIN)的频率对于3通道模式为8.33MHz至104MHz,对于4通道模式为6.25MHz至78MHz。表2列出了LVDS输入的位图。

该序列化器具有HDCP加密功能,在18个RGB附加比特和I²S输入上进行。四个控制模块比特具有额外的HDCP加密。控制信号(CNTL_)没有HDCP加密。SD/CNTL0在用作额外控制输入(AUDIOEN = 0)时,也没有HDCP加密。

-

MAX9266 HDCP多媒体串行链路解串器,带有LVDS系统接口技术手册2025-05-28 1529

-

MAX9263/MAX9264 HDCP千兆位多媒体串行链路串行器/解串器技术手册2025-05-22 1412

-

吉比特多媒体串行链路(GMSL)串行器MAX9277/MAX9281的主要特性2018-04-27 25089

-

供应MAX9286吉比特多媒体串行链路(GMSL)解串器接收多达四个GMSL串行器的数据2018-02-02 5141

-

Maxim推出高速LVDS串行器/解串器MAX9259/MAX9260/MAX92652014-12-06 5965

-

Maxim推出高速LVDS串行器/解串器MAX9263/MAX9265/MAX92642011-04-14 4599

-

MAX9266 HDCP吉比特串行链路解串器2011-04-11 2283

-

MAX9265吉比特多媒体串行链路串行器2011-01-19 1537

-

MAX9259, MAX9260 吉比特多媒体串行链路,提供2010-04-16 1184

-

MAX9249 吉比特多媒体串行链路串行器,具有LVDS系统2010-03-28 1400

全部0条评论

快来发表一下你的评论吧 !