一文详解干法刻蚀工艺

描述

文章来源:学习那些事

原文作者:小陈婆婆

干法刻蚀技术作为半导体制造的核心工艺模块,通过等离子体与材料表面的相互作用实现精准刻蚀,其技术特性与工艺优势深刻影响着先进制程的演进方向。

干法刻蚀理论概述

等离子体驱动的技术特性

在真空环境下,反应气体经电离形成由电子、离子及自由基构成的等离子体,其离化率虽仅0.01%~10%,但通过局部电荷积累效应可维持稳定的刻蚀能量场。

相较于湿法工艺,干法刻蚀摒弃了液态化学试剂,转而通过物理轰击与化学反应的协同作用实现材料去除,这种转变带来三大核心优势:其一是各向异性刻蚀能力,通过离子束方向性控制可实现垂直度优于85°的侧壁形貌;其二为关键尺寸(CD)控制精度,借助实时终点检测技术可将线宽偏差控制在±5nm以内;其三在于工艺稳定性,通过腔体压力与射频功率的精确调控,可实现晶圆内、批次间刻蚀速率波动<2%的极致均匀性。

工艺分类与作用机理

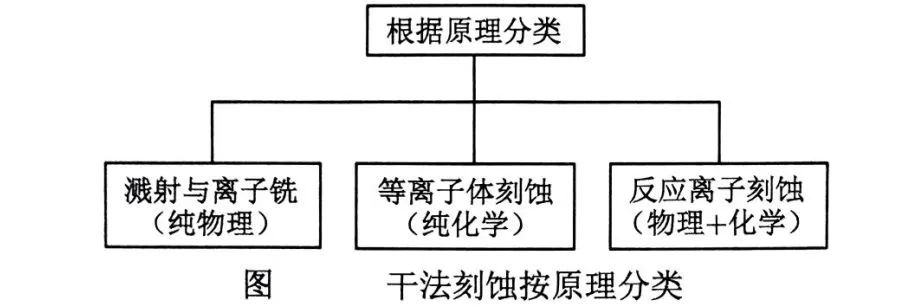

根据能量耦合方式,干法刻蚀可分为三大技术路线:

纯物理刻蚀(溅射/离子铣):依托高能惰性气体离子(如Ar ^+^ )的垂直轰击实现材料溅射去除,具有完全各向异性特征,但缺乏化学选择性,常用于金属互联层的修整

纯化学刻蚀(等离子体刻蚀):利用氟基/氯基自由基与硅基材料的化学反应生成挥发性产物(如SiF 4 ),呈现各向同性特征,对氧化硅/氮化硅的选择比可达10:1以上

反应离子刻蚀(RIE):通过物理轰击与化学刻蚀的动态平衡,在维持各向异性的同时提升刻蚀选择比,已成为逻辑器件栅极刻蚀、存储器三维堆叠的主流解决方案

复合刻蚀机制解析

现代RIE工艺通过多参数协同实现精密控制:

化学刻蚀主导区:中性自由基在表面吸附后引发化学反应,生成易挥发产物,该过程决定基础刻蚀速率与材料选择性

物理轰击增强区:加速离子束通过动量传递打破化学键,清除表面钝化层,其能量密度直接影响各向异性程度

聚合物沉积调控:含碳前驱体在离子轰击下于侧壁形成保护层,通过调整沉积/刻蚀速率比(D/E比)可实现侧壁倾角从0°到90°的连续调控

微负载效应补偿:采用脉冲式射频功率与分压控制技术,有效缓解高深宽比结构中的刻蚀速率衰减问题

技术挑战与发展方向

尽管干法刻蚀在精度与可控性方面优势显著,但仍面临三大技术瓶颈:其一,等离子体诱导损伤需通过低温工艺与钝化层优化进行抑制;其二,多材料叠层刻蚀的选择比需突破100:1量级;其三,EUV光刻胶的刻蚀兼容性亟待提升。当前研究聚焦于高密度等离子体源开发、原子层刻蚀(ALE)技术突破以及机器学习驱动的工艺窗口优化,旨在满足3nm及以下节点对极致精度与良率控制的需求。

该技术体系的发展,正持续推动着半导体器件向更高集成度、更低功耗方向演进,其工艺创新已成为摩尔定律延续的关键技术支柱之一。

溅射与离子铣刻蚀(纯物理刻蚀)

溅射与离子铣刻蚀作为典型的纯物理刻蚀工艺,其核心机理在于利用惰性气体离子(如氩离子)在强电场加速下获得的动能,通过垂直轰击晶圆表面实现材料去除。该技术的显著优势在于其极端的各向异性特性,离子束的直线传播特性使得侧壁倾角可控制在5°以内,这对亚微米级线宽的精确控制至关重要。然而,物理轰击的普适性也带来固有缺陷:

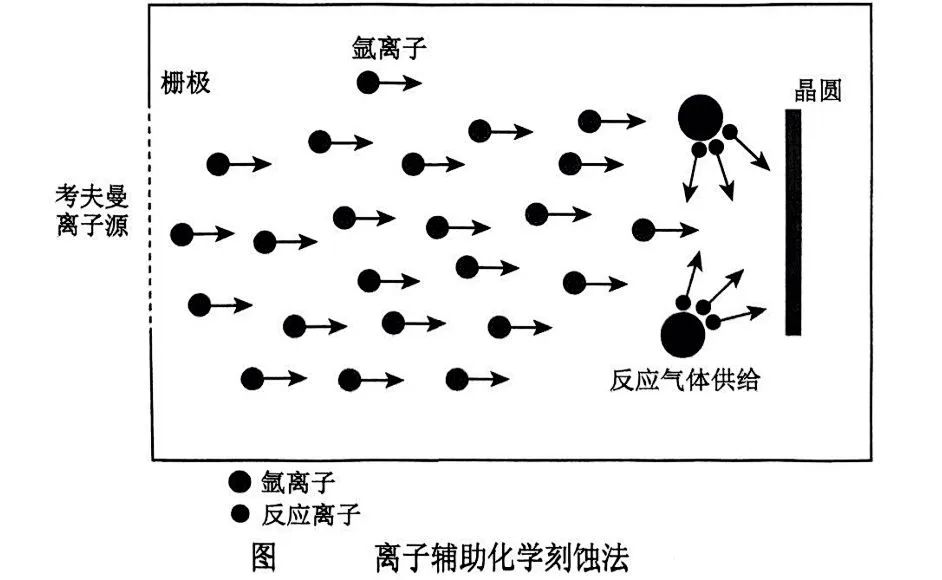

其一,刻蚀选择比通常低于3:1,光刻胶与衬底材料的同步侵蚀问题突出,尤其在图(a)所示的沟槽结构中,光刻胶侧壁侵蚀可导致关键尺寸(CD)偏差超过20%;其二,溅射产物再沉积效应显著,图(b)显示,光刻胶颗粒在离子反弹作用下的再淀积污染率可达15%,需通过高频氩气吹扫缓解;其三,离子沟槽效应如图(c)所示,垂直入射离子在光刻胶斜面发生镜面反射,在衬底形成二次刻蚀沟槽,深度可达原始刻蚀深度的30%。针对上述问题,行业开发出离子辅助化学刻蚀技术

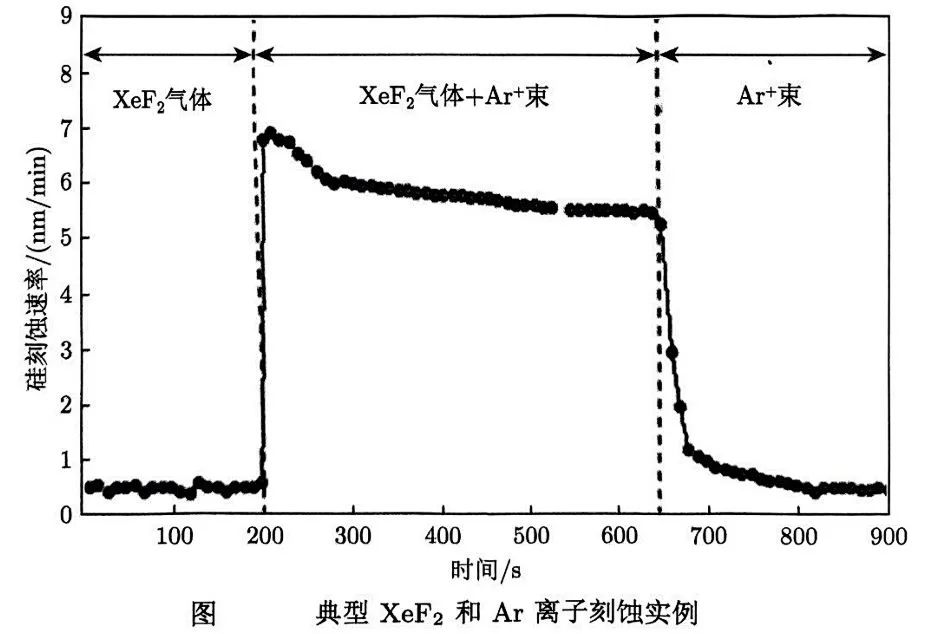

通过在硅片表面引入含氯/氟反应气体,使离子轰击能量从纯物理作用转向促进表面化学反应,典型工艺如CF 4 /Ar混合气体刻蚀硅氧化物,可将选择比提升至8:1,同时保持50nm/min的刻蚀速率。

等离子体刻蚀(纯化学刻蚀)

等离子体刻蚀技术则完全依托于高活性自由基团的化学反应。在射频电场作用下,含氟/氯气体(如SF 6 、Cl 2 )解离生成F·、Cl·等自由基,这些中性粒子通过扩散到达晶圆表面,与硅、二氧化硅等材料发生选择性反应,生成SiF 4 、CO等挥发性产物。

该技术的核心优势在于其卓越的刻蚀选择性,通过气体组分的精确调控,可实现硅/光刻胶选择比>50:1,二氧化硅/氮化硅选择比>30:1,这对保护下层器件结构至关重要。

然而,化学反应的各向同性特性导致线宽控制能力受限,在深宽比>5:1的结构中,侧向钻蚀可使特征尺寸膨胀15%-20%。为突破此瓶颈,行业采用脉冲式等离子体技术,通过周期性通断射频电源,在自由基反应阶段与副产物解吸阶段之间建立动态平衡,使刻蚀剖面各向异性比从0.6提升至0.85。

典型应用如逻辑器件接触孔刻蚀,采用C4F 8 /Ar脉冲等离子体,在保持120nm/min刻蚀速率的同时,将侧向钻蚀控制在2nm以内,满足14nm节点精度要求。

反应离子刻蚀(物理+化学刻蚀)

反应离子刻蚀(RIE)作为半导体制造的核心工艺,通过物理轰击与化学反应的协同作用,实现了刻蚀速率、选择性与各向异性的突破性平衡。其技术本质可拆解为三大核心部分:

协同刻蚀机理

RIE工艺中,等离子体中的带电离子(如Ar ^+^ )在射频偏压加速下获得数百eV动能,通过垂直轰击打破待刻蚀材料表面化学键,同时氟基/氯基自由基(F·、Cl·)与暴露出的活性位点发生选择性化学反应,生成挥发性产物(如SiF 4 、AlCl 3 )。这种“物理清障+化学刻蚀”的协同效应,使刻蚀速率较纯物理或纯化学工艺提升1个数量级。

典型应用如硅刻蚀速率可达1-2μm/min,且硅/光刻胶选择比>20:1。

聚合物调控技术

刻蚀过程中,含碳气体(如CHF 3 、C4F 8 )解离生成的含碳聚合物在侧壁沉积形成保护层,其沉积速率与刻蚀速率的动态平衡决定了侧壁形貌:

高沉积速率模式:聚合物覆盖速率>刻蚀速率,形成V形侧壁,适用于浅沟槽隔离(STI)等结构;

低沉积速率模式:通过优化气体流量比(如CF 4 /CHF3比例),使聚合物仅在侧壁沉积而表面保持清洁,获得垂直度>88°的U形侧壁,满足FinFET栅极刻蚀需求。

工艺系统与参数优化

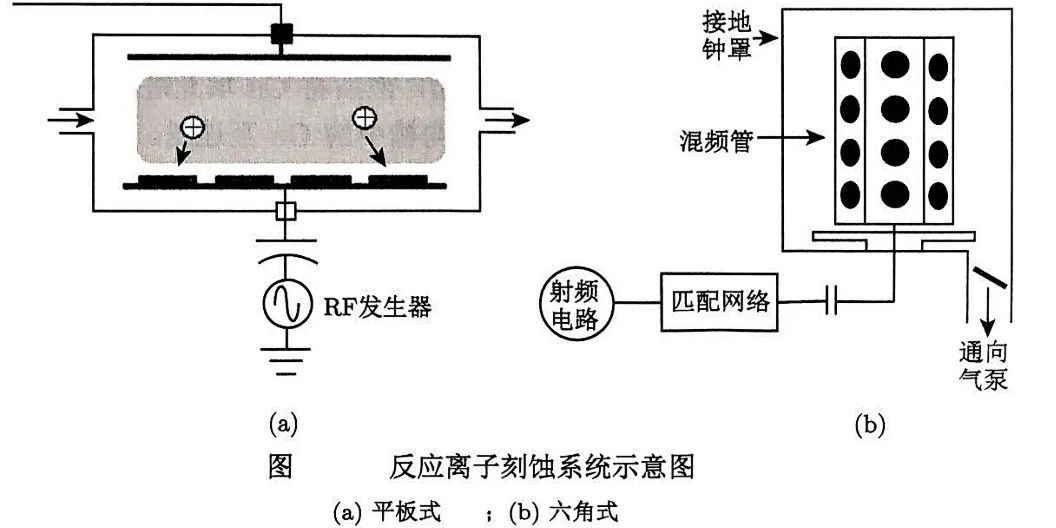

RIE设备分为平板式与电感耦合式(ICP)两大架构:

平板式系统:采用平行板电极结构,通过调节射频功率(100-1000W)与腔体压力(1-100mTorr)控制离子能量与通量,适用于介质层刻蚀;

六角式系统:利用电感耦合产生高密度等离子体(>10¹²/cm³),结合可调偏压电源,实现离子能量独立控制,典型应用如3D NAND通道孔刻蚀,深宽比可达100:1。

典型工艺案例

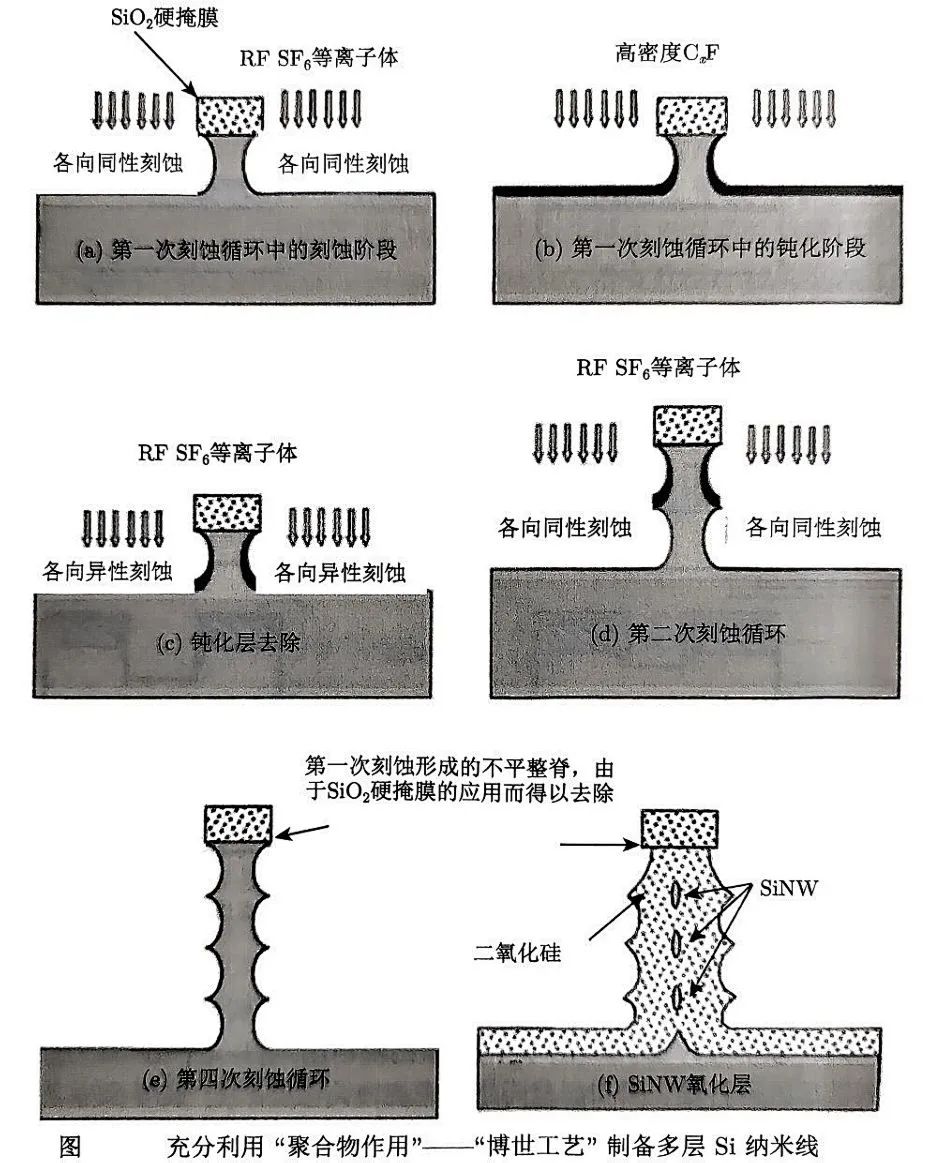

博世工艺:通过SF6刻蚀与C4F8钝化的交替循环,在硅表面形成周期性锯齿状结构。

最终通过热氧化工艺将侧壁形貌转化为多层纳米线,该工艺已实现深宽比60:1的通孔刻蚀;

硬掩膜集成工艺:针对多晶硅栅极刻蚀,采用SiO2硬掩膜替代光刻胶,通过两步RIE工艺,将关键尺寸(CD)偏差控制在±3nm以内,显著提升14nm节点器件良率。

技术边界与材料适应性

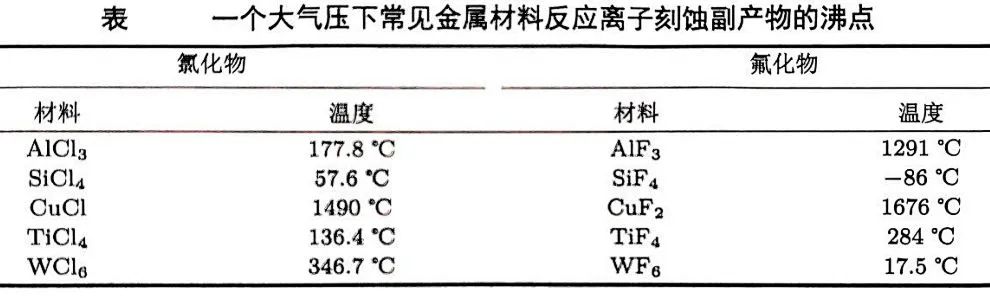

RIE工艺对材料的选择性取决于副产物挥发性:

硅基材料:SiF4(沸点-86℃)的高挥发性使其成为RIE理想刻蚀对象;

金属材料:Cu的刻蚀副产物CuCl(1490℃)因沸点过高易造成再沉积,故采用大马士革工艺替代直接刻蚀;Al则可通过Cl基气体(如BCl 3)实现可控刻蚀,副产物AlCl3沸点181℃,在150℃衬底温度下可有效挥发。

-

干法刻蚀的评价参数详解2025-07-07 2412

-

晶圆表面温度对干法刻蚀的影响2024-12-03 2413

-

干法刻蚀工艺的不同参数2024-12-02 3704

-

半导体芯片制造技术之干法刻蚀工艺详解2024-08-26 4945

-

干法刻蚀常用设备的原理及结构2024-01-20 17450

-

干法刻蚀与湿法刻蚀各有什么利弊?2023-09-26 10807

-

干法刻蚀和清洗(Dry Etch and Cleaning)2022-11-10 10485

-

干法刻蚀解决RIE中无法得到高深宽比结构或陡直壁问题2022-10-10 7305

-

干法刻蚀工艺介绍2022-06-13 1752

-

GaN材料干法刻蚀工艺在器件工艺中有着广泛的应用2020-12-29 4801

-

【转帖】干法刻蚀的优点和过程2018-12-21 5736

-

两种基本的刻蚀工艺:干法刻蚀和湿法腐蚀2018-12-14 72864

-

干法刻蚀原理2010-07-18 6930

-

释放MEMS机械结构的干法刻蚀技术2009-11-18 1431

全部0条评论

快来发表一下你的评论吧 !