MAX9248/MAX9250 27位、2.5MHz至42MHz、直流平衡、LVDS解串器技术手册

描述

概述

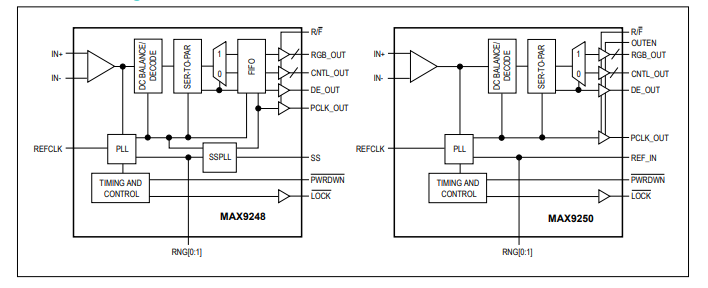

MAX9248/MAX9250数字视频串/并转换器能够在传输数据和控制信号阶段对27位数据进行解串处理。传送数据时,LVDS串行输入转换成18位并行视频数据;传送控制信号时,输入转换成9位并行控制数据。独立的视频和控制信号传输能够充分利用视频定时降低串行数据速率。MAX9248/MAX9250与MAX9247串行器配合工作,构成完整的数字视频传输系统。工作频率低于35MHz时,MAX9248/MAX9250也可以与MAX9217串行器配合工作。

数据表:*附件:MAX9248 MAX9250 27位、2.5MHz至42MHz、直流平衡、LVDS解串器技术手册.pdf

MAX9248具有扩频功能,能够在一定的频率范围内扩展输出数据和时钟频率,以降低EMI。数据和时钟输出扩展频谱可以设置为±4%;或±2%。MAX9250具有输出使能控制,用于数据总线控制。

专有的数据解码技术有助于降低EMI并提供DC平衡。DC平衡允许采用AC耦合,提供发送端和接收端之间的隔离。MAX9248/MAX9250可选择上升沿或下降沿输出锁定。

提供符合ISO 10605 ±10kV接触放电和±30kV气隙放电规范的ESD保护。

MAX9248/MAX9250核电压为+3.3V ±10%,独立的输出电源便于与1.8V至3.3V逻辑电平接口。该器件提供48引脚LQFP封装,工作在-40°C至+85°C或-40°C至+105°C温度范围。

应用

- 车载娱乐系统

- LCD显示器

- 导航系统显示器

- 摄像机

特性

- 可编程±4%或±2%扩频输出,有助于降低EMI (MAX9248)

- 专有的数据解码技术实现DC平衡并降低EMI

- 视频消隐期间解串控制数据

- 5位控制数据输入具有单位误差容限

- 根据工作频率调节输出跳变时间,降低EMI

- 交叉切换输出数据,降低EMI

- 输出使能选通输出总线(MAX9250)

- 锁存时,时钟脉冲延展

- ±2%的参考时钟容限

- 无需外部控制即可与MAX9247串行器同步

- 提供ISO 10605和IEC 61000-4-2 Level 4 ESD保护

- 独立的输出级电源便于与1.8V至3.3V逻辑接口

- +3.3V核电源

- 节省空间的LQFP封装

- -40°C至+85°C和-40°C至+105°C工作温度范围

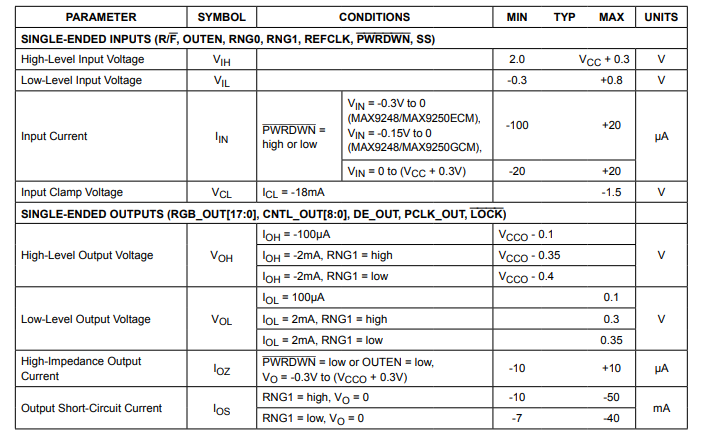

DC电气特性

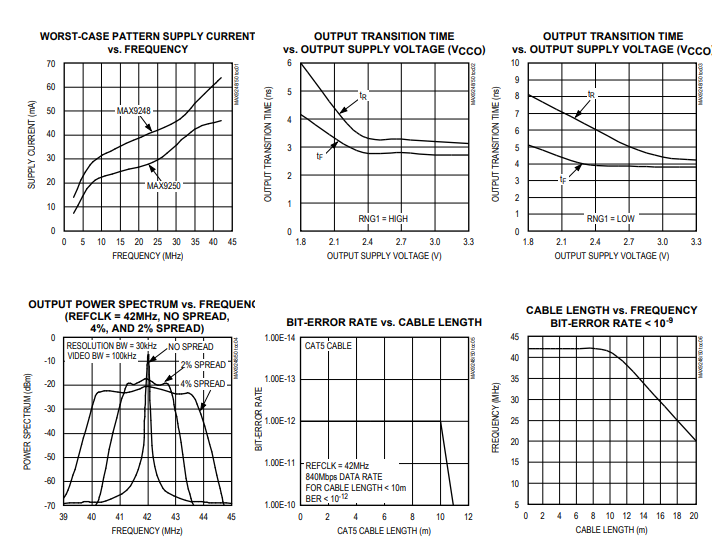

典型操作特性

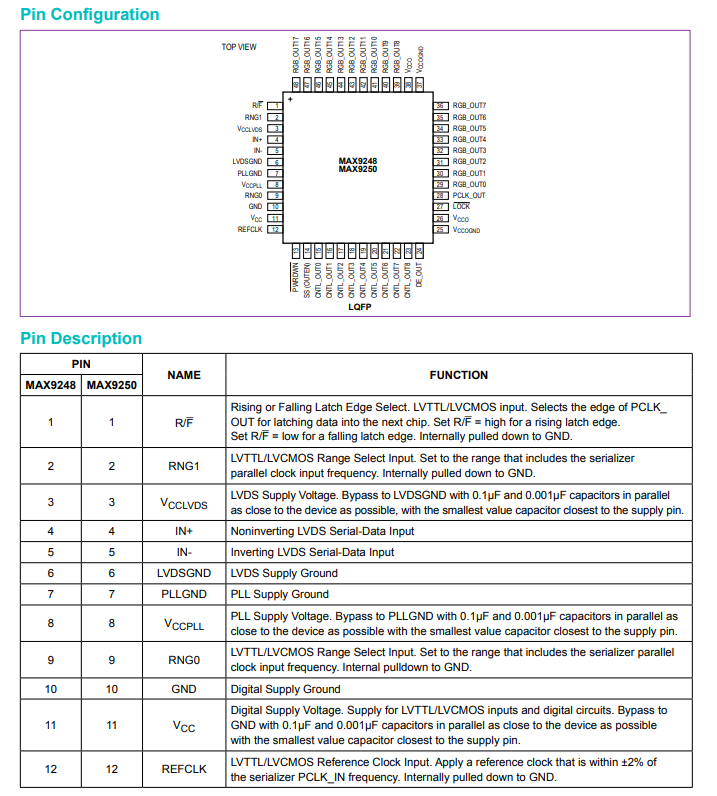

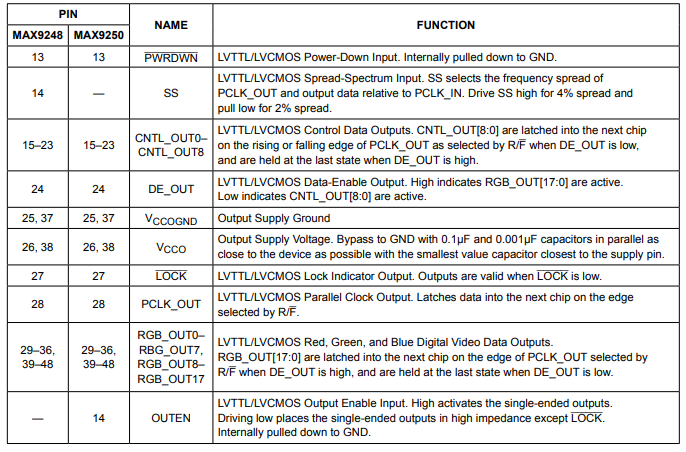

引脚配置描述

框图

应用信息

交流耦合电容的选择

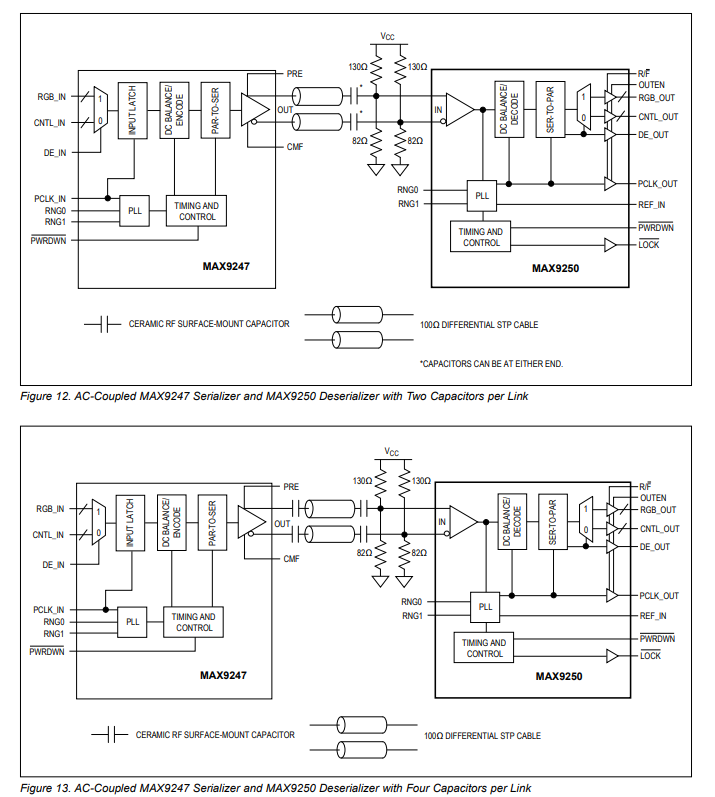

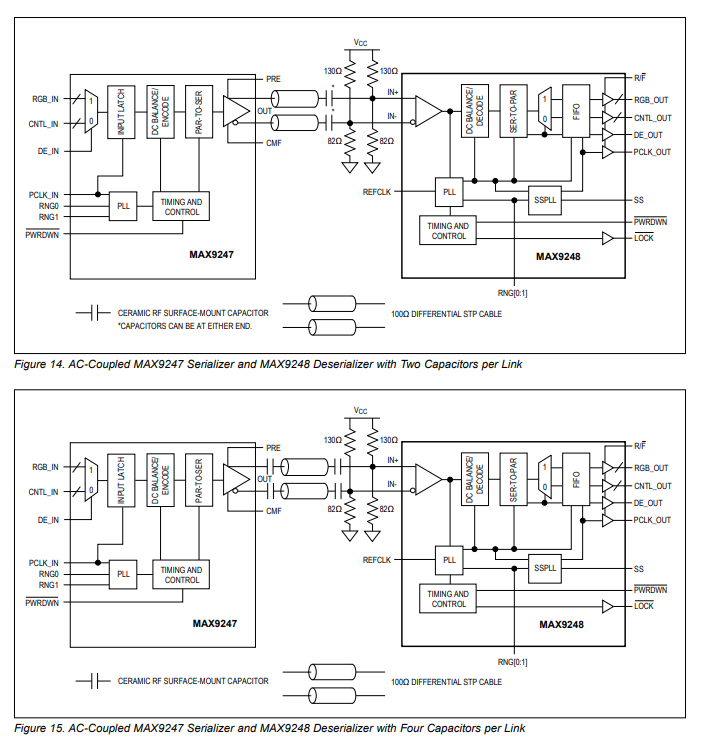

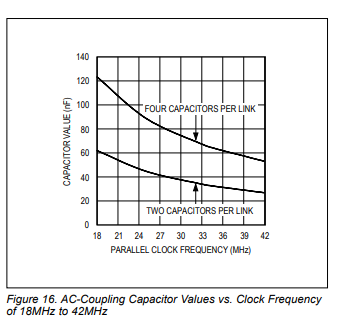

有关根据并行时钟频率计算交流耦合电容值的内容,见图16。该图展示了每条链路使用两个和四个电容的系统的电容值。对于时钟频率低于18MHz的应用,使用0.1μF的电容。

端接和输入偏置

IN+和IN- LVDS输入在内部通过42Ω电阻连接到+1.2V,为交流耦合(图42)提供偏置。假设为100Ω互联,LVDS输入可以用100Ω电阻进行端接,以匹配差分互联的阻抗。

在噪声环境中的交流耦合链路上,采用戴维南端接来提供1.2V偏置。对于100Ω差分阻抗的互联,将每个LVDS线从VCC通过330Ω电阻上拉,并从地到解序列化器输入下拉820Ω电阻(图12和图15)。此端接在公共模式下提供1.2V偏置。戴维南端接的阻抗应为互联差分阻抗的一半,并提供1.2V的偏置电压。

-

10 - MHz至66 - MHz,10:1 LVDS串行器/解串器芯片组的设计与应用2025-12-29 429

-

MAX9206/MAX9208 10位总线LVDS解串器技术手册2025-05-29 1337

-

MAX9247 27位、2.5MHz至42MHz、直流平衡、LVDS串行器技术手册2025-05-28 1358

-

MAX16990-MAX16992: 36V, 2.5MHz Automotive Boost/SEPIC Controllers Data Sheet MAX16990-MAX16992: 36V, 2.5MHz Automotive Boost/SEPIC Controlle2023-10-13 45

-

配合MAX9217/MAX9218/MAX9247/MAX9248/MAX9250评估板工作2023-06-16 4167

-

LVDS系统接口的解串器MAX9268资料推荐2021-04-01 1162

-

具故障保护的 6A、2.5MHz、42V 升压/负输出 DC/DC 转换器2021-03-21 1219

-

Maxim推出高速LVDS串行器/解串器MAX9259/MAX9260/MAX92652014-12-06 5970

-

MAX9234,MAX9236,MAX9238热插拔、21位、直流平衡、LVDS解串器2012-11-08 4801

-

配合MAX9217/MAX9218/MAX9247/MAX92009-04-25 915

-

MAX9248/MAX9250 pdf2008-06-30 1637

全部0条评论

快来发表一下你的评论吧 !