MAX9218 27位、3MHz至35MHz、直流平衡、LVDS解串器技术手册

描述

概述

MAX9218数字视频串/并转换器在数据和控制周期对总共27位数据解串。在数据周期,LVDS串行输入被转换为18位并行视频数据,在控制周期,输入被转换为9位并行控制数据。分开的视频和控制周期充分利用视频时序来降低串行数据速率。MAX9218与MAX9217串行器组成一个完整的数字视频传输系统。

专用数据解码降低EMI并提供DC平衡。DC平衡允许使用AC耦合,为发送和接收之间提供隔离。MAX9218具有可选的上升沿或下降沿输出锁定。

ESD容限符合ISO 10605的±10kV接触放电和±30kV气隙放电规范。

MAX9218内核电压为+3.3V,独立输出电源可实现与1.8V至3.3V逻辑电平接口。该器件可提供48引脚薄型QFN和LQFP封装,可用于-40°C至+85°C工作温度范围。

数据表:*附件:MAX9218 27位、3MHz至35MHz、直流平衡、LVDS解串器技术手册.pdf

应用

- 车载娱乐系统

- LCD显示器

- 导航系统显示器

- 摄像机

特性

- 专用数据解码实现DC平衡并降低EMI

- 视频消隐期间解串控制数据

- 5位控制数据输入为一位的误差容限

- 输出转换时间根据工作频率调整以降低EMI

- 输出分组转换以降低EMI

- 输出使能允许使用输出总线

- 锁定时时钟脉冲延展

- 宽至±2%的参考时钟容限

- 无需外部控制即可与MAX9217串行器同步

- ISO 10605 ESD保护

- 独立输出电源实现与1.8V至3.3V逻辑接口

- +3.3V内核电源

- 节省空间的薄型QFN和LQFP封装

- -40°C至+85°C工作温度范围

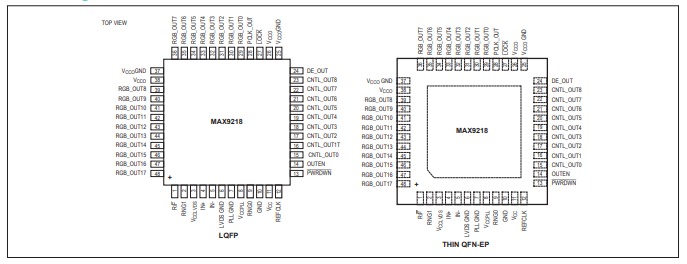

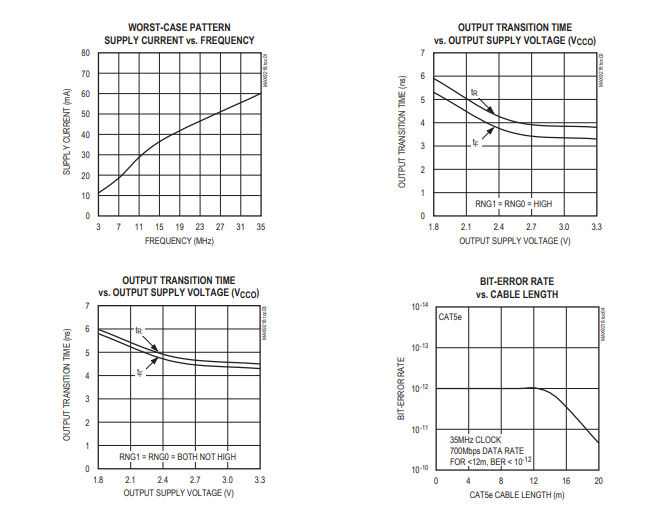

引脚配置描述

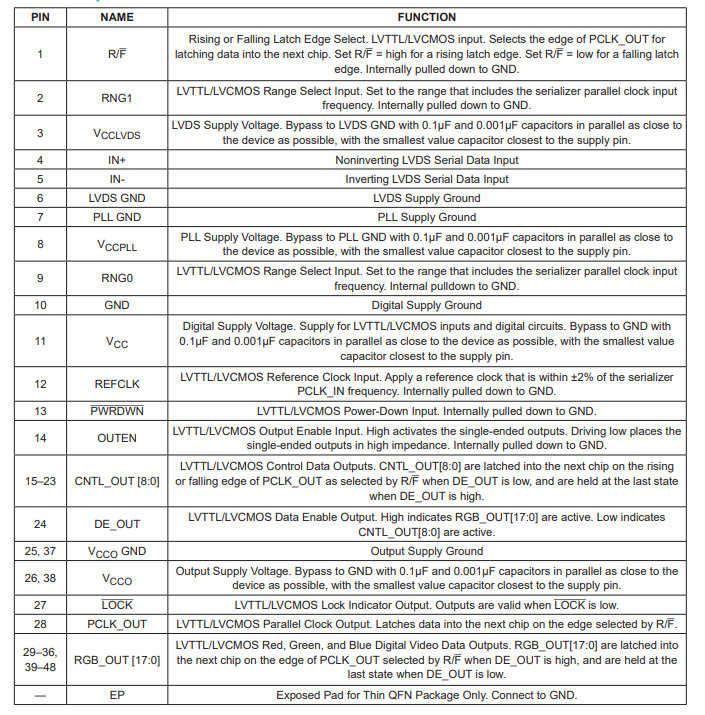

DC电气特性

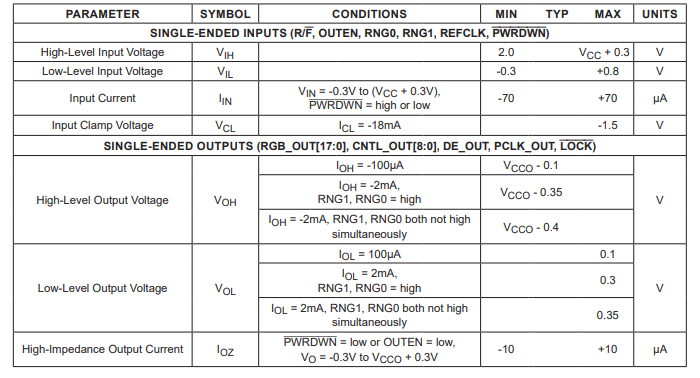

典型操作特性

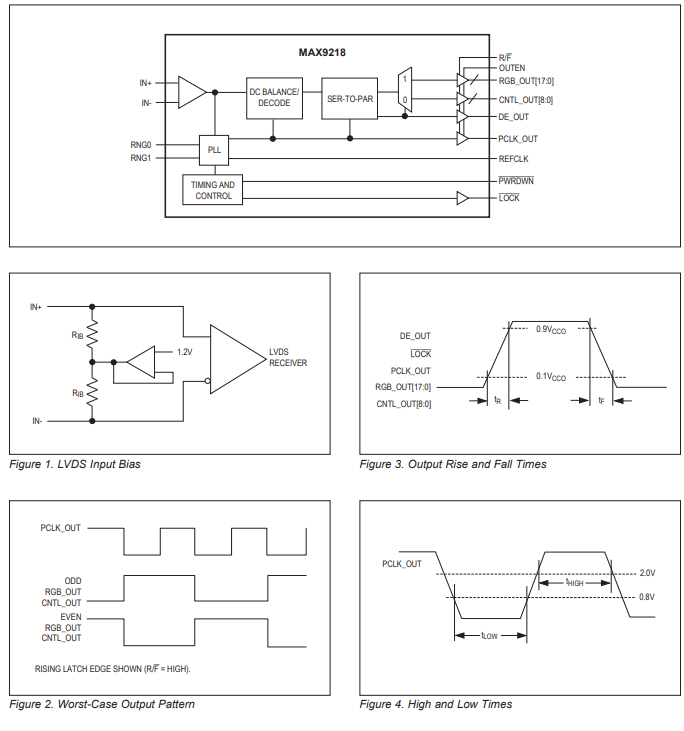

框图

详细说明

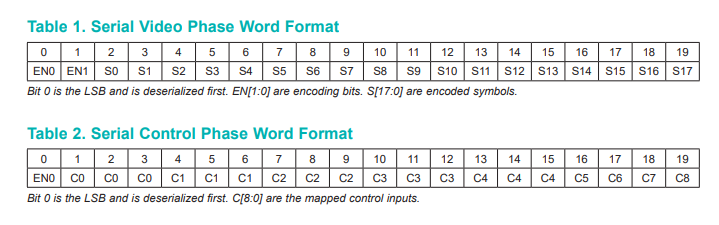

MAX9218直流平衡型解序列化器的并行时钟频率为7MHz至35MHz,对视频数据进行解序列化以输出RGB_OUT[17:0],当数据使能输出DE_OUT为高电平时进行输出,或在控制数据时输出CNTL_OUT[8:0],当DE_OUT为低电平时进行输出。视频数据字是对解码后的开销比特、EN0和EN1进行解码得到的。控制阶段编码字通过最大似然法进行解码,同时进行误码检测。由MAX9217序列化器执行的EN0编码可减少电磁干扰(EMI),并在直流平衡的情况下维持电缆长度。串行输入字格式见表1和表2。

控制数据输入C0至C4,在每个串行比特时间内由序列化器重复三次,使用多数表决法进行解码。通过三个比特中的两个或三个处于相同状态来确定恢复比特的状态,从而提供单比特误码容限。C0至C4的状态由比特自身的电平决定(不使用表决法),C5由其自身电平决定(不使用表决法)。

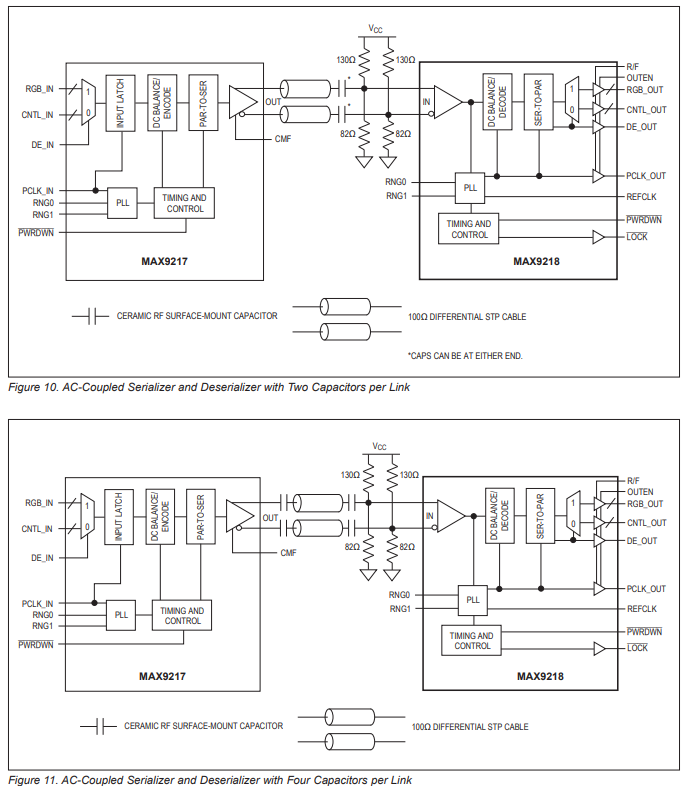

交流耦合优势

交流耦合将LVDS接收器的输入电压提升至电容的额定电压。两个电容就足以实现隔离,在序列化器输出端和/or 解序列化器输入端各放置一个,以防止电缆短路时出现高电压。交流耦合可阻断低频地电位偏移和共模噪声。MAX9217序列化器也可与MAX9218解序列化器直流耦合。图10展示了带有两个电容的交流耦合序列化器,图11展示了每条链路带有四个电容的交流耦合解序列化器。

应用信息

交流耦合电容的选择

有关根据并行时钟频率计算交流耦合电容值的内容,见图12。该图展示了每条链路使用两个和四个电容的系统的电容值。对于时钟频率低于18MHz的应用,使用0.1μF的电容。

端接和输入偏置

IN+和IN- LVDS输入在内部通过35kΩ(最小)电阻连接到+1.2V,为交流耦合(图1)提供偏置。假设为100Ω互联,LVDS输入可以用100Ω电阻进行端接,以匹配差分互联的阻抗。

在噪声环境中的交流耦合链路上,采用戴维南端接来提供1.2V偏置。对于100Ω差分阻抗的互联,将每个LVDS线从VCC通过130Ω电阻上拉,并从地到解序列化器输入下拉820Ω电阻(图10和图11)。此端接在差分模式和共模模式下均提供1.2V偏置。戴维南端接的阻抗应为互联差分阻抗的一半,并提供1.2V的偏置电压。

-

10 - MHz至66 - MHz,10:1 LVDS串行器/解串器芯片组的设计与应用2025-12-29 406

-

探索DS90C241和DS90C124:5 - 35MHz DC平衡24位FPD - Link II串行器与解串器2025-12-27 933

-

MAX9248/MAX9250 27位、2.5MHz至42MHz、直流平衡、LVDS解串器技术手册2025-05-28 1194

-

DS90C124,DS90C241 5MHz至35MHz DC平衡24位FPD-Link Il串行器和解串器数据表2024-07-05 510

-

配合MAX9217/MAX9218/MAX9247/MAX9248/MAX9250评估板工作2023-06-16 4121

-

串行器和解串器对的性能测试:MAX9247和MAX92182023-02-20 12010

-

关于MAX9247/MAX9218串行器/解串器芯片组的性能测试分析2021-04-12 2395

-

瑞盟 MS9218 数字视频串/并转换器在数据和控制周期对总共 27 位数据解串2019-07-30 1588

-

配合MAX9217/MAX9218/MAX9247/MAX92009-04-25 911

-

MAX9217/MAX9218 视频链路中的音频数据传输2008-10-22 1394

-

MAX9218 pdf2008-06-30 1402

全部0条评论

快来发表一下你的评论吧 !