MAX9206/MAX9208 10位总线LVDS解串器技术手册

描述

概述

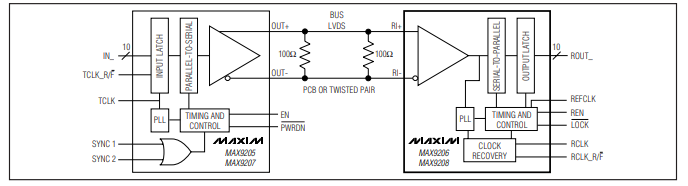

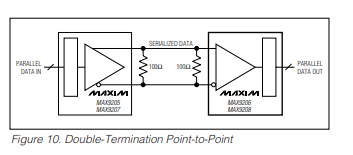

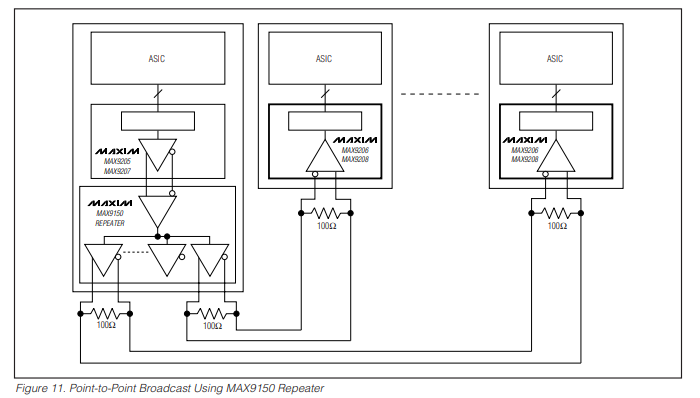

MAX9206/MAX9208解串器将高速串行BLVDS数据流转换位10位宽度的并行LVCMOS/LVTTL数据和时钟。解串器与串行器配对使用,如MAX9205/MAX9207串行器,完成将10位宽度的并行数据转换为串行BLVDS信号。串行器/解串器组合减少了互连线、简化了PCB布线和缩小了电路板尺寸。

MAX9206/MAX9208通过电路板线或双绞线,接收串行数据的速度分别高达450Mbps和600Mbps。这些器件结合了频率锁相、位锁相和帧锁相,以产生并行速率时钟和并行对齐的10位数据。串行器消除了并行总线的时钟至数据和数据至数据扭曲。

电源关断模式将典型的电源电流降低至600µA以下。一旦上电(加上电源或驱动/PWRDN为高电平,MAX9206/MAX9208在收到同步信号或来自MAX9205/MAX9207的串行数据后,即可完成时钟锁相。输出使能端可以禁止输出,在保持锁相的前提下,将并行数据输出和恢复时钟输出置为高阻态。

MAX9206/MAX9208工作于+3.3V单电源,指定温度范围为-40°C至+85°C,MAX9206/MAX9208提供28引脚SSOP封装。

数据表:*附件:MAX9206 MAX9208 10位总线LVDS解串器技术手册.pdf

应用

- 上/下路复用器

- 背板与互连应用

- 蜂窝电话基站

- 数字交叉连接

- DSLAM

- 网络路由器和交换机

特性

- 单片解串器(对比SerDes),尤其适合于单向数据链路

- 自动时钟恢复

- 允许热插入和同步,无须终止系统运行

- 额定速率的BLVDS串行输入,适合于点对点和总线应用

- 快速伪随机锁相

- 宽参考时钟输入范围

- 16MHz至45MHz (MAX9206)

- 40MHz至60MHz (MAX9208)

- 720ps

P-P的高抖动承受能力(MAX9206) - 30mA的低电源电流(MAX9206工作于16MHz)

- 10位并行LVCMOS/LVTTL输出

- 高达600Mbps的数据吞吐率(MAX9208)

- 可编程的输出选通边沿

- 引脚兼容于DS92LV1212A和DS92LV1224

典型操作电路

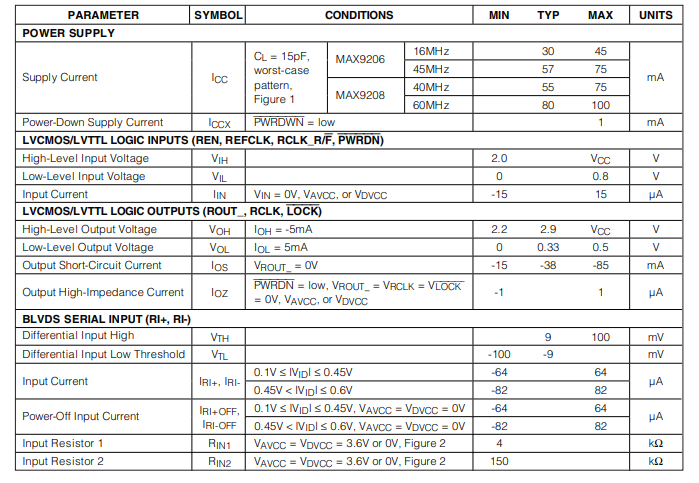

DC电气特性

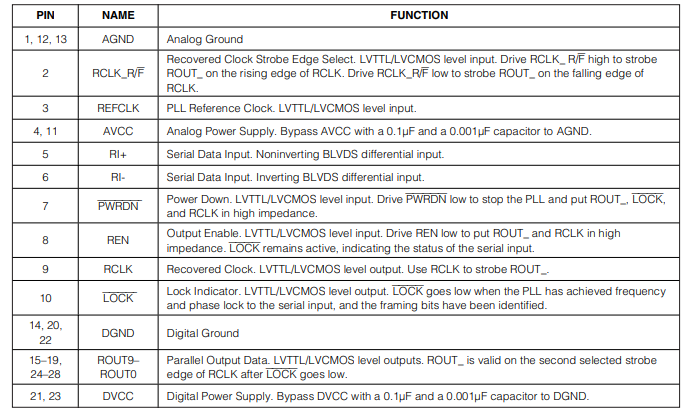

引脚配置描述

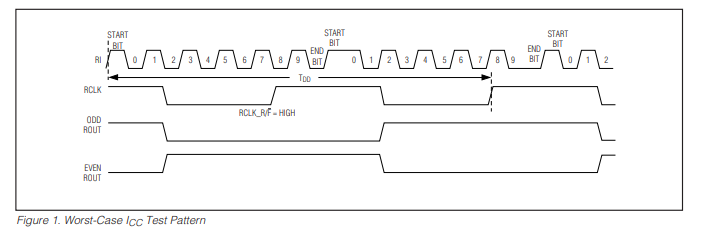

测试电路/时序图

应用信息

电源去耦

对每个电源引脚进行去耦,使用高频表面贴装陶瓷电容,0.1μF 和 0.001μF 电容并联,尽可能靠近器件安装,较小容值的电容离电源引脚最近。

差分走线与端接

匹配 MAX9206/MAX9208 的差分走线特性。使用受控阻抗介质。避免使用非平衡电缆,如简单同轴电缆。像双绞线这样的平衡电缆能提供更好的信号质量,并且由于抵消作用,产生的电磁干扰(EMI)较少。平衡电缆有助于拾取噪声,而共模噪声会被差分接收器抑制。

消除反射并确保差分模式工作,需将差分走线紧密并行布线。通过匹配走线的电气长度来减少偏斜。过度偏斜会导致磁抵消效果下降。

保持差分走线之间的距离恒定,以避免差分阻抗不连续。避免 90° 转弯,尽量减少过孔数量,以防止阻抗不连续。

-

MAX9205/MAX9207 10位、总线LVDS串行器技术手册2025-05-29 1034

-

MAX9218 27位、3MHz至35MHz、直流平衡、LVDS解串器技术手册2025-05-28 1440

-

MAX9208EAI+ - (Maxim Integrated) - 接口 - 串行器,解串器2023-08-02 71

-

LVDS串行器的信号完整性与传输速率和电缆长度的关系2023-06-10 4315

-

LVDS串行器-解串器在双绞线电缆上的性能2023-03-30 5023

-

在汽车应用中使用MAX9205/MAX9206 LVDS SerDes传输I2S音频流2023-02-08 3693

-

如何使用10位LVDS串行器/解串器IC对I2S音频数据流进行STP布线2023-01-14 4993

-

LVDS系统接口的解串器MAX9268资料推荐2021-04-01 1156

-

Maxim推出高速LVDS串行器/解串器MAX9259/MAX9260/MAX92652014-12-06 5966

-

MAX9205,MAX9207,pdf数据资料2012-12-17 819

-

MAX9234,MAX9236,MAX9238热插拔、21位、直流平衡、LVDS解串器2012-11-08 4722

-

MAX9206芯片驱动外部辅助电路2012-09-10 2580

-

Maxim推出高速LVDS串行器/解串器MAX9263/MAX9265/MAX92642011-04-14 4600

-

MAX9206, MAX9208 10位总线BLVDS解串器2010-12-21 1387

全部0条评论

快来发表一下你的评论吧 !