MAX9205/MAX9207 10位、总线LVDS串行器技术手册

描述

概述

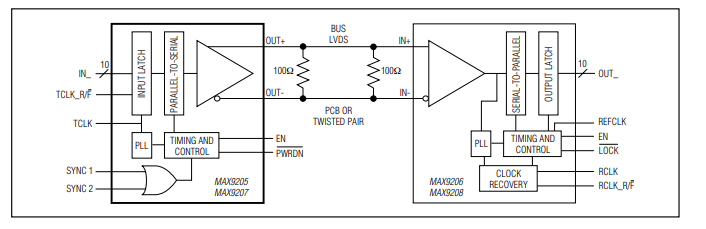

MAX9205/MAX9207串行器将10位宽度并行LVCMOS/LVTTL数据转换为串行高速总线LVDS数据流。串行器与解串器配对使用,如MAX9206/MAX9208解串器,完成将串行输出再转换为10位宽度的并行数据。

MAX9205/MAX9207在PCB线或双绞线上,传输串行数据的速度分别高达400Mbps和660Mbps。因为时钟是从串行数据流中提取,所以消除了在并行总线上出现的时钟至数据和数据至数据扭曲。

该串行器不需要外接元件,也仅需少量的控制信号。由TCLK_R/F选择输入数据选通边沿,当器件停止工作时,/PWRDN可用于省电控制。一旦上电,将激活同步模式,它还受控于两个同步输入端:SYNC1和SYNC2。

MAX9205可以锁定16MHz至40MHz系统时钟,而MAX9207可以锁定40MHz至66MHz的系统时钟。在器件完全锁定本地系统时钟之前,以及器件处于电源关断模式下,串行器输出保持高阻态。

两种器件均工作于+3.3V单电源,指定工作温度范围-40°C至+85°C,提供28引脚SSOP封装。

数据表:*附件:MAX9205 MAX9207 10位、总线LVDS串行器技术手册.pdf

应用

- 上/下路复用器

- 背板与互连应用

- 蜂窝电话基站

- 数字交叉连接

- DSLAM

- 网络路由器和交换机

特性

- 单片串行器(对比SerDes),尤其适合于单向数据链路

- 用于解串器的同步成帧位允许板卡热插入,无须中止系统运行

- 额定速率的LVDS串行输出,适合于点对点和总线应用

- 宽参考时钟输入范围

- 16MHz至40MHz (MAX9205)

- 40MHz至66MHz (MAX9207)

- 140ps (峰峰值)的低系统抖动(MAX9207)

- 34mA的低电源电流(MAX9205)

- 10位并行LVCMOS/LVTTL接口

- 高达660Mbps的有效数据速率(MAX9207)

- 可编程的输入锁存边沿

- 与DS92LV1021和DS92LV1023引脚兼容的升级器件

典型应用电路

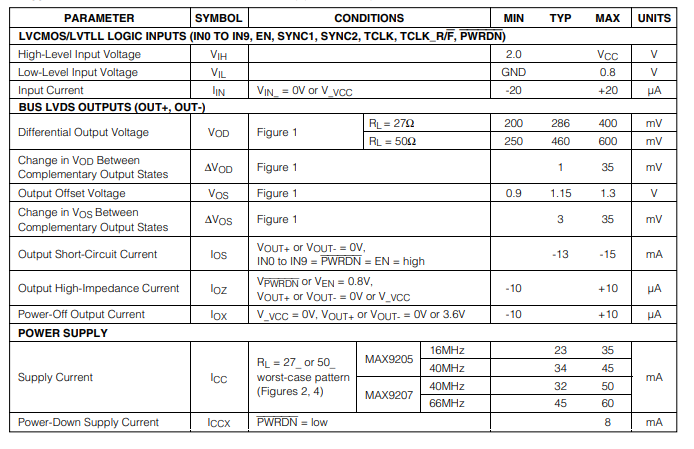

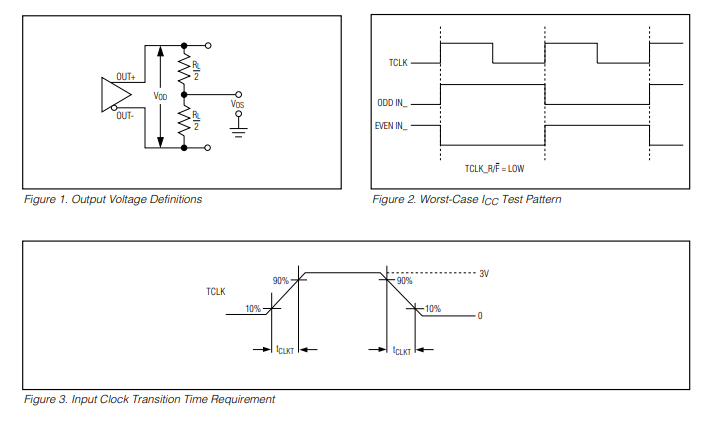

DC电气特性

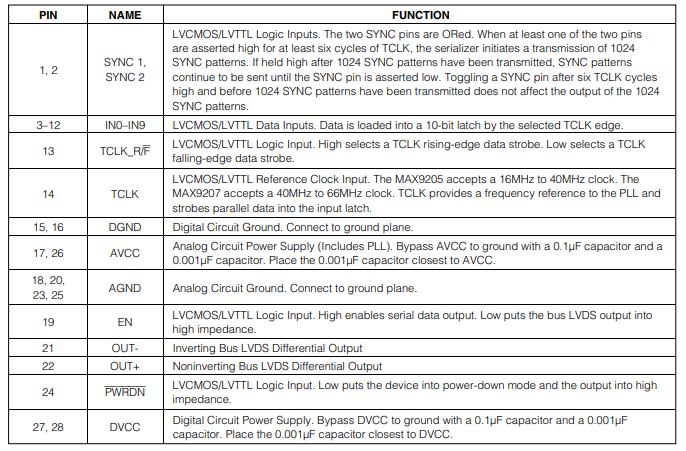

引脚配置描述

应用信息

电源去耦

使用高频表面贴装陶瓷电容(0.1μF 和 0.001μF 并联)对AVCC进行去耦,尽可能靠近器件安装,较小容值的电容靠近AVCC。使用高频表面贴装陶瓷电容(0.1μF 和 0.001μF 并联)对DVCC进行去耦,尽可能靠近器件安装,较小容值的电容靠近DVCC。

差分走线与端接

匹配MAX9205/MAX9207的输出走线特性。使用受控阻抗介质,并在传输线两端对介质的特性阻抗进行端接。在点对点链路的接收端,通常使用单个电阻进行端接,可提供可接受的性能。不过,MAX9205/MAX9207的输出电平是为双端接的点对点和多点应用而专门设定的。采用单个100Ω 端接时,输出摆幅会更大。

避免使用非平衡电缆,如带状电缆或简单同轴电缆。像双绞线这样的平衡电缆能提供更优的信号质量,且由于抵消效应,产生的电磁干扰(EMI)较少。平衡电缆易拾取共模噪声,而这种噪声会被差分接收器抑制。

通过紧密并行布置差分走线来消除反射,并确保噪声以共模形式耦合。通过匹配走线的电气长度来减少偏斜。过度的偏斜会导致磁抵消效果下降。

差分输出信号的布线应使每路输出与其外部返回路径靠近,以保持差分间的距离恒定。避免差分走线出现不连续情况。避免90°转弯,并尽量减少过孔数量,以进一步防止阻抗不连续。

-

MAX9206/MAX9208 10位总线LVDS解串器技术手册2025-05-29 1275

-

MAX9205EAI/V+T - (Maxim Integrated) - 接口 - 串行器,解串器2023-08-04 63

-

MAX9205EAI+ - (Maxim Integrated) - 接口 - 串行器,解串器2023-08-02 74

-

LVDS串行器的信号完整性与传输速率和电缆长度的关系2023-06-10 4310

-

LVDS串行器-解串器在双绞线电缆上的性能2023-03-30 5018

-

在汽车应用中使用MAX9205/MAX9206 LVDS SerDes传输I2S音频流2023-02-08 3691

-

如何使用10位LVDS串行器/解串器IC对I2S音频数据流进行STP布线2023-01-14 4987

-

Maxim推出高速LVDS串行器/解串器MAX9259/MAX9260/MAX92652014-12-06 5965

-

MAX9205,MAX9207,pdf数据资料2012-12-17 819

-

MAX9205, MAX9207 10位、总线式LVDS串行2010-12-21 1467

-

信号完整性与传输速率和电缆长度的LVDS串行器-Signal2009-05-01 2954

全部0条评论

快来发表一下你的评论吧 !