EMC 设计避坑指南:四不口诀

描述

你的产品明明设计得很好,为什么一做EMC测试就失败?雷卯EMC小哥教大家4个超实用的EMC设计技巧四不口诀,帮你避开常见的坑!

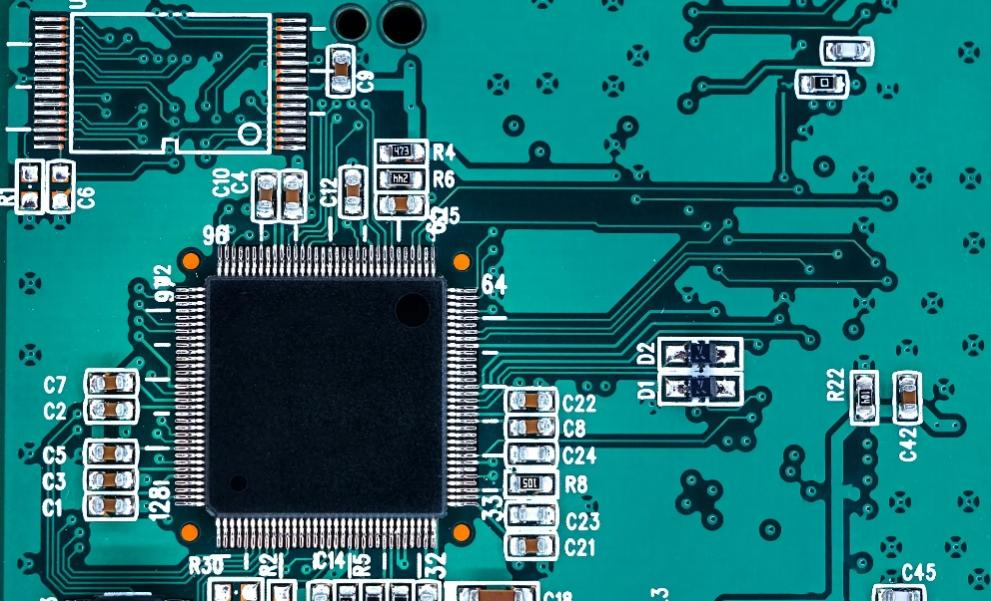

准则1 让电流“走捷径”,不绕远路

核心逻辑:高频电流走 “电感最小路径”,环路越大→辐射越强!

雷卯实验室关键知识点:

· 信号电流必成环路,回流路径紧贴流出路径

· 低频(kHz 级)走 “电阻最小路径”,回流可能分散;高频(MHz 级)走 “电感最小路径”,回流紧贴主线

· 设计技巧:高速信号与回流平面紧邻,缩短信号层与地平面间距

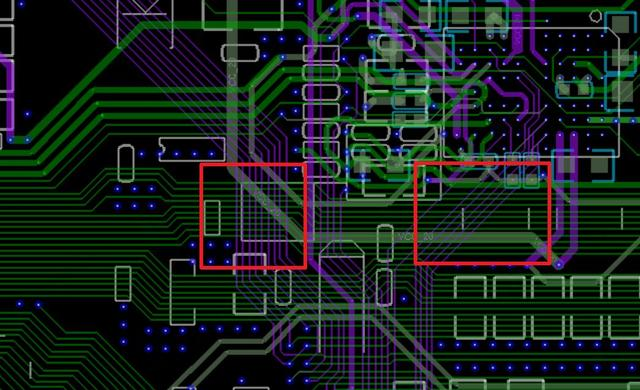

准则2 不要分割信号返回平面

雷卯 EMC 工程师的安全经验法则是:为所有信号电流提供一个完整的返回平面。若某低频信号易受干扰或可能干扰电路板上的电路,应使用单独层的走线将其电流回流至源端,而非分割平面。随意开槽 / 分割地平面,导致回流路径突变→EMI 激增!

例外情况:仅当低频敏感信号需隔离时(如音频电源),可采用独立回流走线,但需满足:

1. 独立层单独回流,不与高频平面交叉

2. 可咨询雷EMC专家,避免照搬案例

警示:99% 场景下,完整平面是最优解!

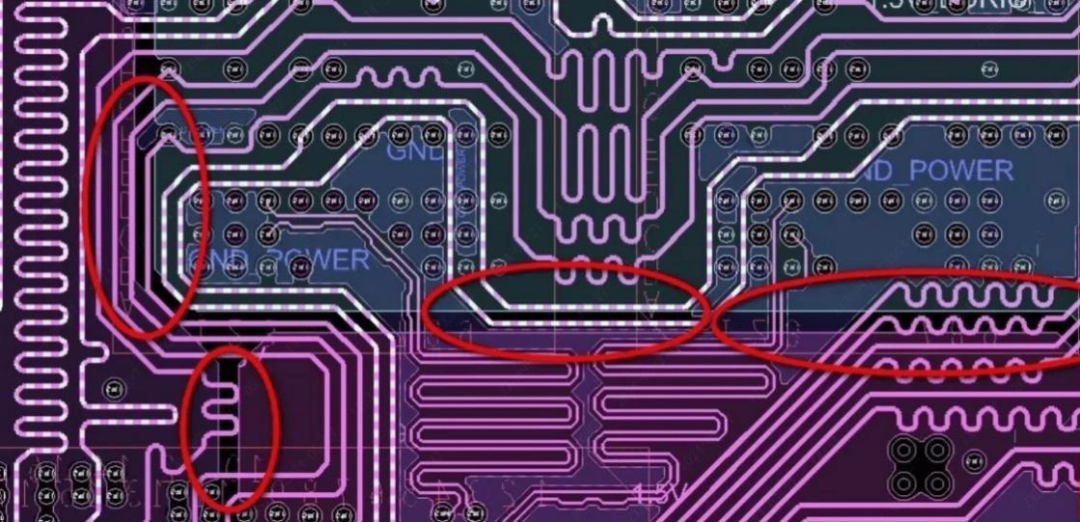

准则3 不要在连接器之间布置高速电路

在雷卯实验室评估过的电路板设计中,这是最常见的问题之一。许多本可轻松满足EMC要求(无需额外成本或精力)的简单设计,最终却因违反这一规则而不得不增加大量屏蔽和滤波措施。

为何连接器的位置如此重要?在几百兆赫兹以下的频率,波长可达米级或更长,印刷电路板本身的“天线”因电尺寸小而效率低,但连接到电路板的电缆或其他设备却可能成为高效天线。

信号电流在走线上流动并通过完整平面回流时,平面上任意两点的电压差通常与平面内的电流成正比。当所有连接器沿电路板一侧排列时,它们之间的电压差可忽略不计;但如果连接器之间布置了高速电路,连接器之间可能产生几毫伏或更高的电位差,这些电压会驱动电流流入连接的电缆,导致产品超出辐射发射要求。

准则4 不盲目追求最快边沿,控制好信号转换时间

核心逻辑:高频电流走 “电感最小路径”,环路越大→辐射越强!

雷卯推荐控制手段对比表:

| 方法 | 优点 | 缺点 | 适用场景 |

| 受控逻辑芯片 | 效果稳定,易集成 | 需定制器件 | 高速总线(如 PCIe) |

| 串联电阻 | 低成本,易调整 | 可能引入振铃 | 普通数字信号 |

| 铁氧体磁珠 | 高频抑制强 | 阻抗非线性,难调试 | 混合信号边界 |

| 并联电容 | 不可取!增加功耗 + 延迟 | 严重恶化信号质量 | 禁止使用! |

雷卯EMC小哥推荐黄金比例:转换时间≈20% 位周期(如 100MHz 时钟,边沿控制在 2ns 以内)

总结 四不口诀速记表

| 准则 | 核心要求 | 关键点 |

| 一不 | 电流不绕远路,需走高频最小电感路径 | 雷卯EMC小哥建议:确保信号与回流平面紧邻,缩短信号层与地平面间距,让电流 “走捷径”。 |

| 二不 | 不分割信号返回平面 | 为信号电流提供完整返回平面,规避因开槽/ 分割地平面导致的回流路径突变与 EMI 激增。 |

| 三不 | 连接器间不布高速电路 | 将连接器集中排列于电路板一侧,避免高速电路介于接口之间。 |

| 四不 | 不盲目追求最快边沿,控制好信号转换时间 | 采用受控逻辑芯片、串联电阻等方式,遵循“转换时间≈20% 位周期” 黄金比例。 |

Leiditech雷卯电子致力于成为电磁兼容解决方案和元器件供应领导品牌,供应ESD、TVS、TSS、GDT、MOV、MOSFET、Zener、电感等产品。雷卯拥有一支经验丰富的研发团队,能够根据客户需求提供个性化定制服务,为客户提供最优质的解决方案。

-

分享一些嵌入式系统编程中内存操作相关的避坑指南2021-12-17 1159

-

PCB设计避坑指南2023-03-20 2370

-

【避坑指南】电容耐压降额裕量不合理导致电容频繁被击穿2023-11-23 3741

-

EMC检测避坑指南2025-05-13 661

-

EMC 设计避坑指南:四不口诀2025-05-28 763

-

工业现场电磁干扰强?聚徽解码工控一体机抗干扰“避坑”指南2025-06-12 1747

-

MES系统避坑指南2025-10-29 521

-

避坑指南!RK3568开发板选型,这5点没看清千万别下手!(附迅为驱动开发指南资源)2025-10-30 1063

-

DIY避坑指南向|车载功放DIY别瞎买芯片!CD7377CZ/CD7388实操避坑全攻略2025-12-09 1022

-

冬季灌封胶不干?环氧聚氨酯低温固化五大避坑指南 |铬锐特实业2026-01-26 398

-

捷尚微分享辉芒微8位MCU选型指南,高效避坑省成本!2026-02-05 702

-

频率源/信号源模块设备怎么选?避坑指南2026-02-27 628

-

进线电抗器选型避坑指南|企业必看干货2026-02-28 324

-

2026射频同轴连接器选型终极指南:SMA/N/BNC/FAKRA四大天王,这样选不踩坑!2026-03-23 560

全部0条评论

快来发表一下你的评论吧 !