ADBMS6821/ADBMS6822单通道/双通道isoSPI收发器技术手册

描述

概述

ADBMS6821(单通道)和 ADBMS6822(双通道)通过每个数据链路的单双绞线连接在两个隔离器件之间提供双向隔离串行端口接口(isoSPI ^™^ )通信。每个收发器将逻辑状态编码为信号,通过隔离栅传输至另一个收发器。接收器件对传输信号进行解码,并将从机总线驱动至相应的逻辑状态。隔离栅可通过电容或脉冲变压器桥接以实现数百伏隔离。

ADBMS6821/ADBMS6822收发器使用匹配的拉电流和灌电流驱动差分信号,无需变压器中心抽头并降低了电磁干扰(EMI)。接收器中的精密窗口比较器可检测差分信号。

收发器可与先进的ADI电池堆监控器配对使用,在系统控制器断电时也能实现电池单元电压和传感器监控(低功耗电池单元监控或LPCM)。收发器提供超时功能,在编程的时间周期内未接收到传递心跳消息时,该功能可唤醒或提醒系统。

在整个数据手册中,所有引脚名称均指ADBMS6822上的两个收发器。例如,VDD指VDD和VDD2。

数据表:*附件:ADBMS6821 ADBMS6822单通道 双通道isoSPI收发器技术手册.pdf

应用

- 电动和混合动力汽车

- 备用电池系统

- 工业网络

- 远程传感器

特性

- 高达 2 Mbps 的隔离式双向串行数据通信

- 放入兼容:单 (ADBMS6821) 和双 (ADBMS6822)

- 完全独立的双收发器 (ADBMS6822)

- 使用电容器或变压器的简单电气隔离

- 单对双绞线上的双向接口

- 支持最长 100 米的电缆长度

- 很低 EMI 易感性和辐射

- ADI 公司电池监视器具有 LPCM 支持

- 中断输出,唤醒 LPCM 系统

- 4 Mbps 单向模式

- 在大多数 SPI 系统中不需要更改软件

- 超低空闲电流

- 自动接口唤醒检测

- 工作温度范围:–40°C 至 +125°C

- 3.0 V 至 5.5 V isoSPI 驱动电源

- 1.7 V 至 5.5 V 微控制器接口

- 3.0 V 至 30 V 输入,用于唤醒和监控功能供电(兼容 12 V 电池)

- 32 引脚、可侧焊 LFCSP

- AEC-Q100 适用于汽车应用

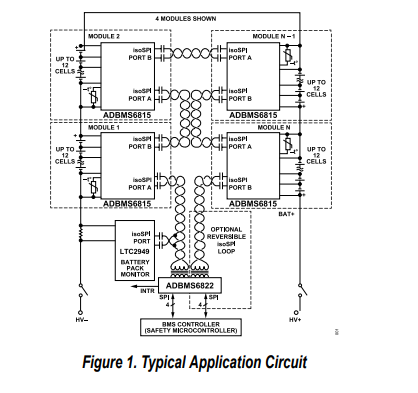

应用电路

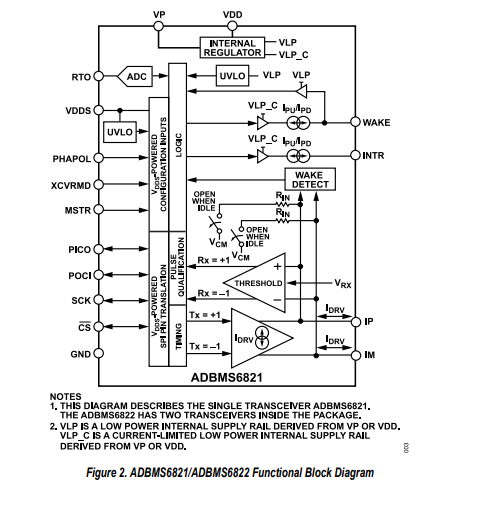

框图

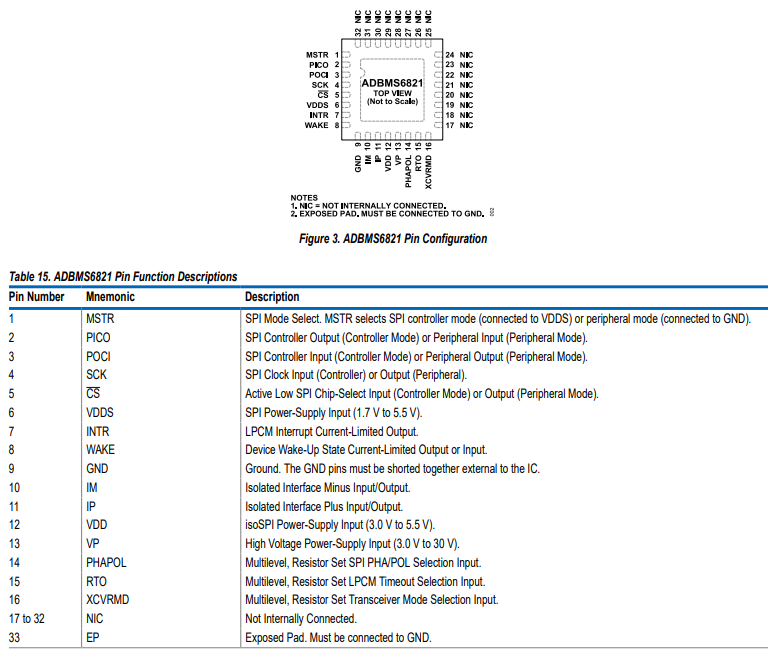

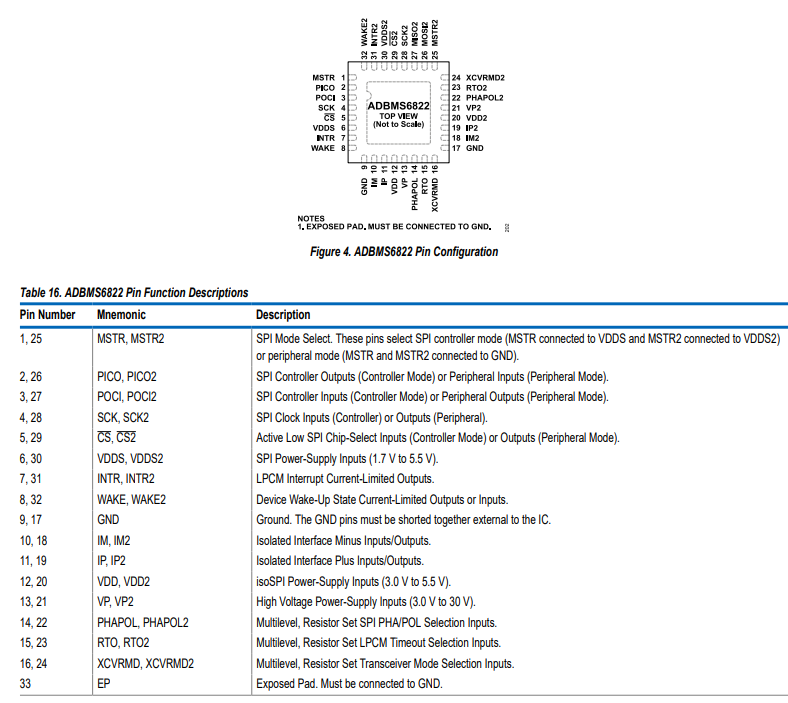

引脚配置描述

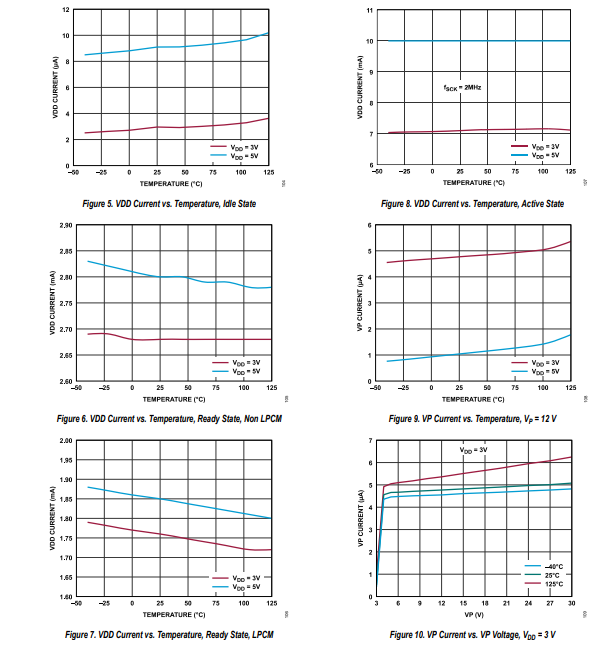

典型性能特征

ISOPSI 脉冲规格

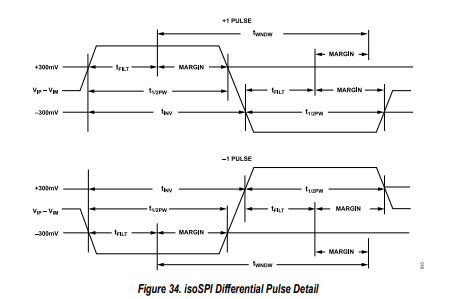

图34展示了 +1和 -1 isoSPI脉冲的时序规格。这些对称脉冲的任一版本都适用相同的时序规格。在“isoSPI 脉冲时序规格”部分会进一步细分这些规格,分为远端(长)和数据(短)参数。

一个有效的脉冲必须满足tJDPW的最小规格以及tINV的最大规格。换句话说,半脉冲宽度必须足够长,以通过相应的脉冲定时器,但又不能过长,以免在有效窗口内开始反转。在POCI中观察到的响应(或CS)会在脉冲反转后的tDEL延迟之后出现。

ISOPSI 交互与时序

图35和图36中的时序图展示了处于控制器模式(连接到SPI控制器)的isoSPI与处于外设模式(连接到SPI外设)的isoSPI之间的交互情况。图35展示了PHA = 0的操作,图36展示了PHA = 1的操作(同时展示了SCLK信号在POL = 0或1时的时序图)。虽然未全部展示,但控制器和外设SPI模式(PHA和POL设置)的各种组合都可与这些设备配合使用。

控制器SPI设备通过拉低CS来发起通信。ADBMS6821/ADBMS6822收发器将此转换为IP和IM引脚上的长 -1脉冲。该脉冲跨越隔离屏障(存在一定的关联电缆延迟),到达IP和IM引脚(连接到外设收发器)。当有效时,长 -1脉冲会转换回下降沿的CS转换,此时应用于外设SPI设备。如果外设PHA = 1,SCLK会保持空闲状态。

在控制器SPI设备提供第一个锁存时钟沿(通常是上升沿,例外情况见表20)之前,外设收发器必须发送初始外设数据位Sn。Sn的值由POCI的采样状态决定。

如果POCI = 0,外设会向控制器发送一个短 -1脉冲。控制器收发器接收并解码该脉冲,并将控制器POCI设置为0(与外设匹配)。然而,如果外设POCI = 1,外设不会发送脉冲。控制器将此无响应解释为1,并将控制器POCI设置为1。这种行为使得可以将多个外设收发器连接到单个电缆,且信号不会冲突(更多信息,请参阅“多点”部分)。

在下降沿的CS序列之后,控制器上的每个锁存时钟沿都会将PICO引脚驱动为isoSPI数据脉冲(Mn,Mn - 1,...,M0),同时外设收发器会同时锁存数据位。外设收发器接收每个数据位后,会根据其POCI引脚的状态将其设置为相应状态,然后在外设的POCI数据返回之前生成一个SCK脉冲(可以是短 -1脉冲,也可以是空脉冲)。

在通信结束时,外设发送的数据位(无论是脉冲还是空脉冲)都会被控制器忽略。外设收发器必须返回一个数据位,因为控制器无法预测通信何时结束。控制器SPI设备随后会拉高CS,以长 +1脉冲的形式传输到外设。该过程以外设收发器将CS转换为高电平并将SCK恢复到空闲状态(如果PHA = 1)而结束。

-

ADBMS6817:高性能8通道多节电池监测器的技术剖析2026-02-12 265

-

ADBMS6834精度+扩展性无对手 力压群雄2025-07-16 5701

-

Analog Devices Inc. EVAL-ADBMS6830BMSW 评估板特性/应用/系统架构2025-06-07 1554

-

Analog Devices Inc. EVAL-ADBMS6822 评估板数据手册2025-06-05 1121

-

Analog Devices Inc. ADBMS6821/ADBMS6822 isoSPI™收发器数据手册2025-05-29 1288

-

ADBMS6821/ADBMS6822收发器 利用匹配的拉电流和灌电流驱动差分信号,无需变压器中心抽头并降低了电磁干扰2024-12-09 2389

-

ADBMS1818多通道电池堆监控器数据手册2023-12-15 919

-

ADBMS2950/ADBMS2951/ADBMS2951/ADBMS2952:电池包装监测数据表 ADI2023-10-08 434

-

内存的单通道与双通道2012-07-05 18361

全部0条评论

快来发表一下你的评论吧 !