ADuM1253超低功耗I2C隔离器,具有单向SCL、扩展VDD、空闲总线热插拔和低体积技术手册

描述

概述

ADuM1253 提供两个开漏通道(一个单向,一个双向),适用于需要在同一线路上双向传输数据但具有单向时钟的应用(例如 I^2^C)。为了防止闩锁行为,第 1 侧输出包含特殊缓冲器,可将逻辑低电平电压调节为 0.64V,并且输入逻辑低电平阈值比输出逻辑低电平电压至少低 50mV。第 2 侧具有不调节逻辑低电平输出电压的传统缓冲器。

ADuM1253 在隔离器的第 1 侧和第 2 侧均具备 1.71V 至 5.5V 独立电源。该套件的工作频率高达 2MHz。每侧均提供 21μA 的超低待机电流,非常适合电池供电系统。

ADuM1253 首先对总线引脚进行预充电,然后监视总线状态以发现空闲总线或检测 I^2^C 停止条件,再连接第 1 侧和第 2 侧,从而为第 2 侧的热插拔连接提供无干扰总线连接。ADuM1253 采用 8 引脚窄体 SOIC 封装。该套件的额定工作环境温度范围为 -40°C 至 +125°C。

数据表:*附件:ADuM1253超低功耗I2C隔离器,具有单向SCL、扩展VDD、空闲总线热插拔和低体积技术手册.pdf

应用

- 隔离式 I^2^C/SMBus 接口

- 电池管理系统

- 以太网供电 (PoE)

- 电机控制系统

特性

- 低 V

OL(MAX) 可实现更高的 I^2^C 套件兼容性- 第 1 侧:0.69V

- 第 2 侧:0.4V

- 超低功耗可延长电池寿命

- 400 kHz 时每通道 142μA(典型值)

- 较宽的独立 V

DD1/VDD2电源范围支持更多逻辑电压电平并可实现电平转换- 两侧均为 1.71V 至 5.5V

- 热插拔第 2 侧 I/O 可防止数据损坏

- 初始第 2 侧连接发生在总线空闲或停止状态

- 双向 I^ 2^ C 数据传输高达 2MHz SCL

- 强大的灌电流能力可降低 R

PULL-UP值,从而实现更快的总线速度- 第 1 侧:5mA

- 第 2 侧:50mA

- 为数字信号提供稳健的电气隔离

- 可持续耐受 (V

IOWM)- 8 引脚窄体 SOIC:445V

RMS

- 8 引脚窄体 SOIC:445V

- 可承受 ±10kV 浪涌,符合 IEC 61000-4-5 标准

- 具有爬电距离和电气间隙的封装

- 8 引脚窄体 SOIC:4mm

- 可持续耐受 (V

- 安全和法规认证(申请中)

- IEC60747-17(申请中)

- 增强型 VIORM 窄体 SOIC:630V

PEAK

- 增强型 VIORM 窄体 SOIC:630V

- UL 1577(申请中)

- 8 引脚窄体 SOIC:1 分钟 3000V

RMS

- 8 引脚窄体 SOIC:1 分钟 3000V

- IEC/EN/CSA 62368-1(申请中)

- IEC/EN/CSA 61010-1(申请中)

- CAN/CSA-C22.2 第 14-18 号(申请中)

- IEC60747-17(申请中)

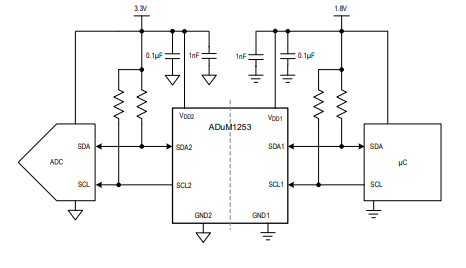

简化应用程序图

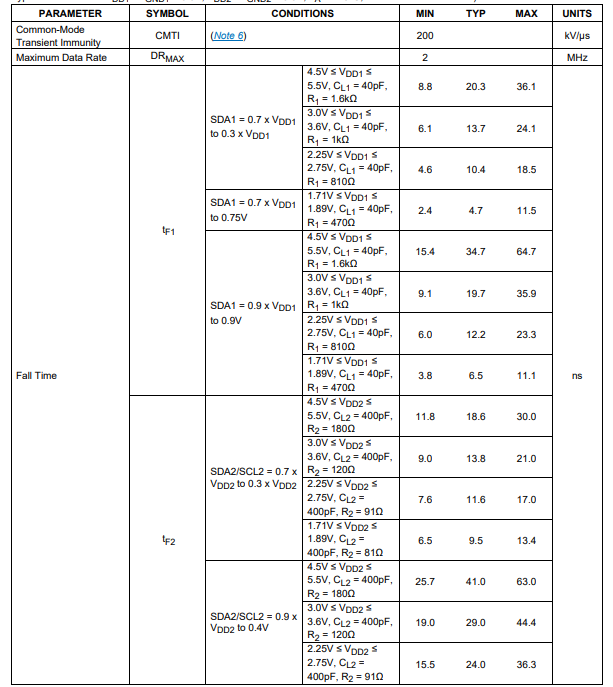

动态特性

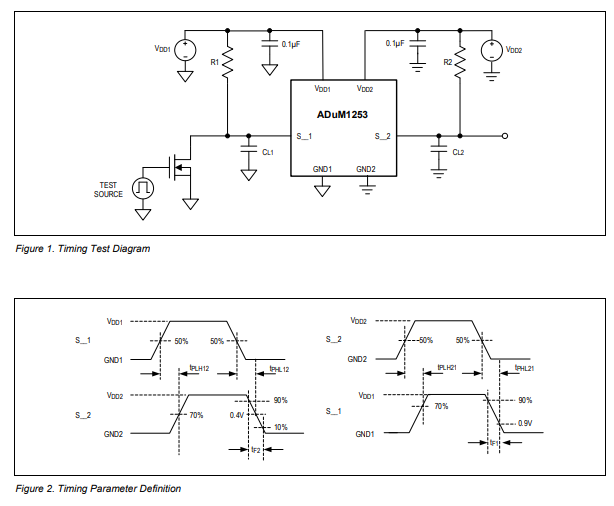

时序图

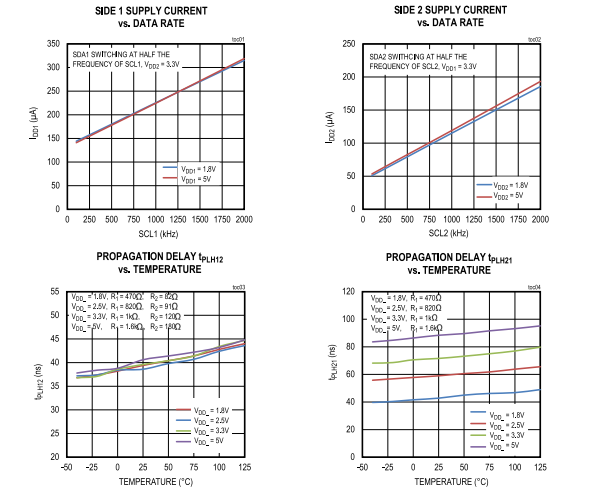

典型操作特性

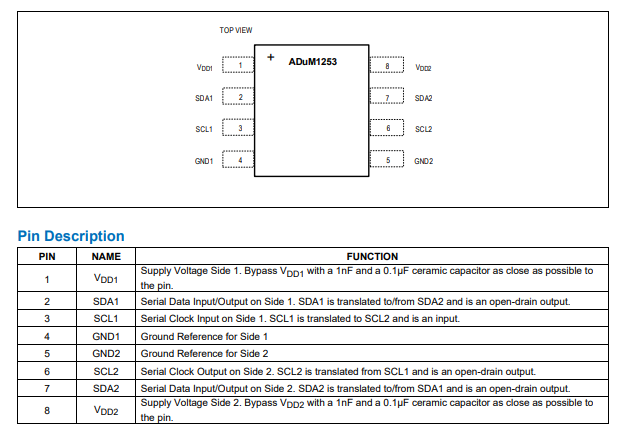

引脚配置描述

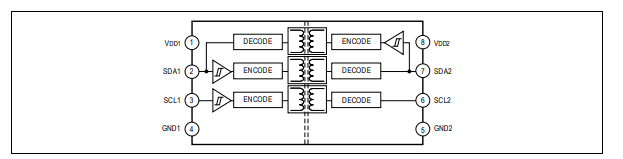

框图

详细说明

ADuM1253是一款双通道I²C隔离器,采用亚德诺半导体(Analog Devices, Inc.)的专有工艺技术。该器件可在高达 +125°C的环境温度下,于不同电源域的电路之间传输数字信号。

此器件提供两条开漏通道,一条用于数据的双向通道,另一条用于时钟的单向通道,适用于仅需在隔离栅一侧进行信号方向控制的I²C应用。典型应用包括I²C拓扑结构,其中所有I²C控制器都位于隔离栅的一侧,且/或隔离栅另一侧的设备不使用时钟延长功能。

该器件在隔离器两侧均配备独立的1.71V至5.5V电源。其工作的SCL频率最高可达2MHz。宽温度范围和高隔离电压使该器件非常适合在恶劣的工业环境中使用。

数字隔离

ADuM1253为在两个接地域之间传输的数字信号提供增强型电气隔离。

在8引脚MSOP封装(21 - 0036)中,ADuM1253可承受高达2.5kV RMS的电压差,持续时间最长为60秒,以及高达424V PEAK的连续隔离电压。

在8引脚窄SOIC封装(21 - 0041)中,ADuM1253可承受高达3kV RMS的电压差,持续时间最长为60秒,以及高达630V PEAK的连续隔离电压。

在8引脚宽SOIC封装(21 - 100415)中,ADuM1253可承受高达5kV RMS的电压差,持续时间最长为60秒,以及高达1200V PEAK的连续隔离电压。

双向通道

ADuM1253器件有一条双向开漏输出通道。

双向通道不需要方向控制输入。一侧的低电平逻辑会使另一侧相应引脚被拉低,同时,由于侧1输出逻辑低电平(V OL1)的协调作用,可避免器件内部出现数据锁存问题,其保持逻辑低电平阈值(V IL1)约为0.64V 。侧1输出利用特殊偏置,可防止侧1的低电平输出逻辑被误当作输入低电平并传输到侧2,进而避免锁存效应。

SDA2和SCL2是常规输出,不调节ADuM1253的输出电压。

由于其特殊性质,侧1的SDA/SCL引脚与不同电源域的引脚不能连接在一起。此限制还包括使用类似缓冲器或上升沿加速电路的其他器件的引脚。侧2引脚没有此限制。因此,侧2的引脚可以相互连接,或与ADuM1253的侧1引脚及其他双向缓冲器或电平转换器的引脚连接。

-

ISO164x系列:增强EMC与GPIO功能的热插拔双向I2C隔离器2026-01-21 376

-

ISO164x热插拔双向I2C隔离器:设计与应用全解析2025-12-17 979

-

Analog Devices Inc. ADuM1252双向I2C隔离器数据手册2025-06-10 1182

-

Analog Devices Inc. ADuM1253超低功耗I2C数字隔离器数据手册2025-06-07 1160

-

ADuM2250/ADuM2251热插拔双通道I2C隔离器技术手册2025-06-06 1887

-

ADuM1250/ADuM1251热插拔双向I2C隔离器技术手册2025-06-05 1816

-

ADUM2250热插拔双通道I2C® 隔离器2022-11-10 2281

-

热插拔I2C隔离器2021-05-25 1012

-

LTC4310:热插拔I2C隔离器产品手册2021-04-25 894

-

可热插拔的I2C隔离器LTC43101相关资料下载2021-04-15 888

-

可热插拔的I2C隔离器LTC43102相关资料下载2021-04-13 1363

-

可热插拔的 I<SUP>2</SUP>C 隔离器在具有隔离接地的总线之间实现了简单的连接2021-03-21 754

-

ADuM1250/ADuM1251:热插拔双通道I2C隔离器2021-03-19 1114

-

凌力尔特推出可热插拔的I2C隔离器--LTC43102010-04-24 1960

全部0条评论

快来发表一下你的评论吧 !