ADN4622/ADN4624 5.7 kV rms/1.5 kV rms、四通道 LVDS 2.5 千兆位隔离器技术手册

描述

概述

ADN4622/[ADN4624]是一款四通道、信号隔离式低电压差分信号 (LVDS) 缓冲区,能够以很低的通道在高达 2.5 Gbps 的数据速率下运行。该器件集成了 ADI 公司的 iCoupler^®^ 技术,已针对高速运行进行增强,可提供 LVDS 信号链的插入式电气隔离。到 LVDS 接收器和来自 LVDS 驱动器的交流耦合和/或电平转换允许隔离其他高速信号,例如电流模式逻辑 (CML)。

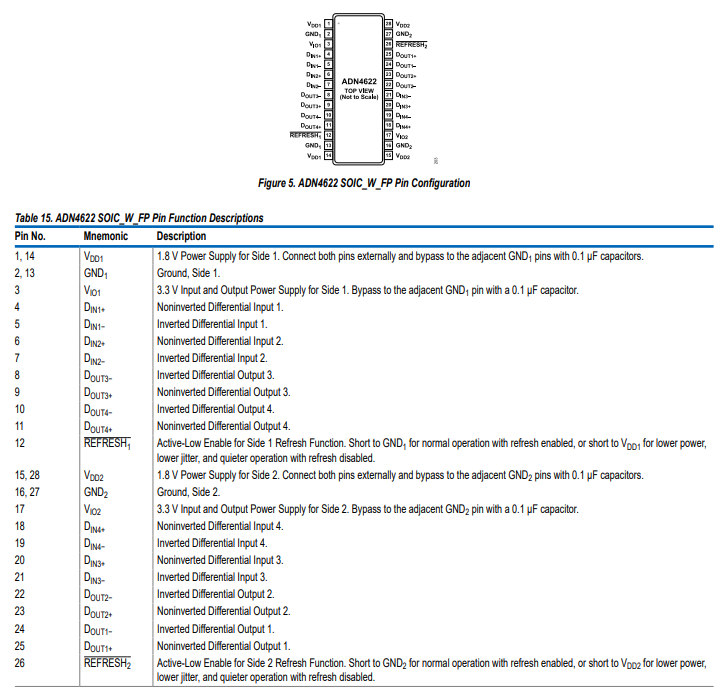

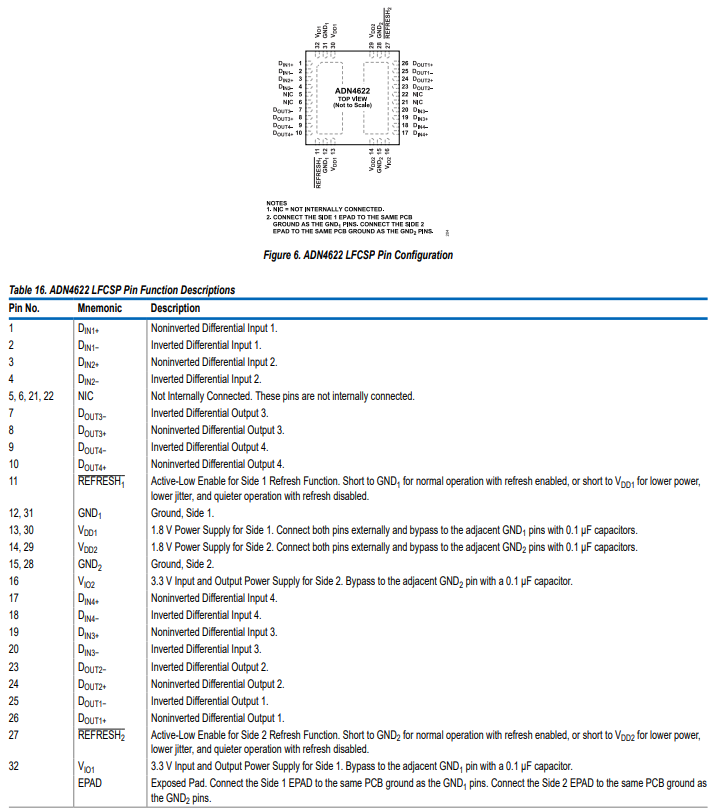

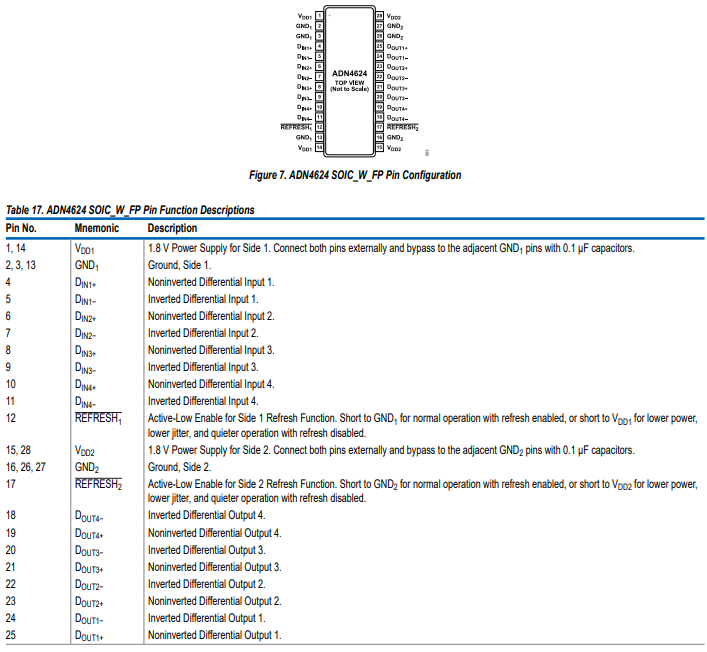

ADN4622/ADN4624 包括一种刷新机制,用于监控输入和输出状态,并确保它们在没有数据转换的情况下保持不变。为了以低抖动实现低功耗和高速运行,LVDS 和隔离器电路依赖于 1.8 V 电源。ADN4622/ADN4624 完全适合在宽工业温度范围内工作,并且可采用 28 引脚、宽体和小间距 SOIC_W_FP 封装,爬电距离和电气间隙为 8.3 mm(适用于 5.7 kV rms 或 8 kV 峰值浪涌和脉冲电压,并在交流电源电压下增强绝缘),或者采用 6 mm × 6 mm LFCSP 封装,爬电距离和电气间隙为 1.27 mm(适用于基本/功能性隔离)。

数据表:*附件:ADN4622 ADN4624 5.7 kV rms 1.5 kV rms、四通道 LVDS 2.5 千兆位隔离器技术手册.pdf

应用

- 隔离式视频和成像数据

- 模拟前端隔离

- 数据平面隔离

- 隔离式高速时钟和数据链路

- 多千兆位 SERDES

- 板对板光纤更换(例如:短距离光纤)

特性

- 5.7 kV rms 和 1.5 kV rms LVDS 隔离器

- 符合 TIA/EIA-644-A LVDS 信号电平

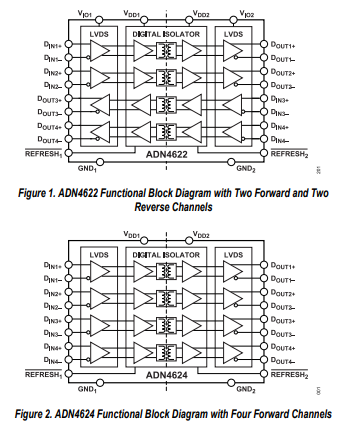

- 四通道配置(ADN4622:2 + 2,ADN4624:4 + 0)

- 能以高达 2.5 Gbps 的任意数据速率进行切换,具有低抖动

- 跨四个通道的 10 Gbps 总带宽

- 传播延迟 2.15 ns(典型值)

- 典型抖动:0.82 ps rms 随机,40 ps 总峰值

- 低功耗 1.8 V 电源

- ±8 kV IEC 61000-4-2 ESD 跨隔离栅保护

- 高共模瞬变抗扰度:100 kV/μs(典型值)

- 安全和监管审批 (28 引脚 SOIC_W_FP 封装)

- UL(申请中):5700 V rms 持续 1 分钟,符合 UL 1577 标准

- CSA 元件验收通知 5A(申请中)

- VDE 符合性证书(申请中)

- DIN V VDE V 0884-11 (VDE V 0884-11):2017-01

- V

IORM= 849 V峰值(工作电压)

- 启用或禁用刷新(低速输出正确性检查)

- 工作温度范围:−40°C 至 +125°C

- 28 引脚、宽体、细间距 SOIC_W_FP 封装,爬电距离和电气间隙为 8.3 mm,或 6 mm × 6 mm LFCSP 封装,爬电距离和电气间隙为 1.27 mm

框图

引脚配置描述

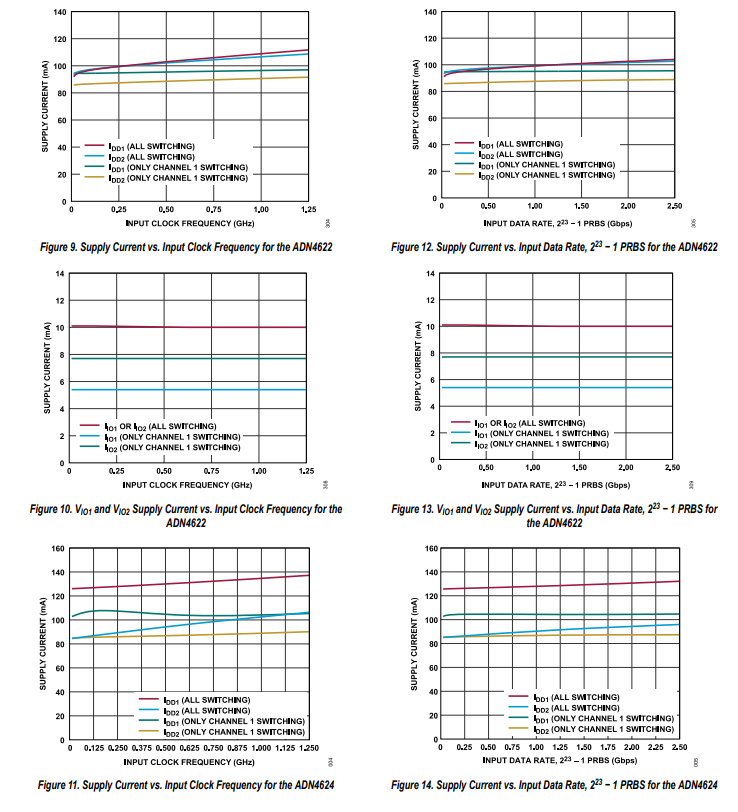

典型性能特征

应用信息

PCB布局

ADN4622/ADN4624可处理高达1.25GHz时钟频率的高速低压差分信号(LVDS),以及高达2.5Gbps的不归零制(NRZ)数据。在隔离此类高频信号时,应尽可能在靠近LVDS发送器和接收器的位置布置LVDS走线和端接。放置一个100Ω的端接电阻,使其与发送器和接收器的TxN和RxN引脚之间的距离相等。

为确保LVDS信号完整性、减少系统抖动并降低印刷电路板(PCB)的电磁干扰(EMI),LVDS信号线上需要100Ω差分的受控阻抗走线。应选择两条走线的宽度、它们之间的间距以及与接地层或电源层的距离,以优化每对走线的特性阻抗。通过谨慎选择过孔位置,可将串扰降至最低。

ADN4624已通过EN 55032 B级辐射发射限值,无需额外的考虑因素。在隔离高频数据或高速时钟时,应采用隔离器。为了减少辐射,特定的PCB布局措施有助于减少二极管天线效应,从而实现隔离间隙,并为ADN4622提供足够的裕量以满足EN 55032 B级辐射发射限值。使用增强型PCB布局(在隔离器区域下叠加内部PCB第2层和第3层,使用受控阻抗走线、堆叠式陶瓷电容),ADN4622在900Mbps PRBS数据运行时,可满足EN 55032 B级辐射发射限值。

高速PCB设计的最佳实践是避免高速LVDS信号走线产生辐射。特别建议在断开连接的情况下切换高速LVDS信号(以及时钟)。使用共模扼流圈、铁氧体或其他滤波器(如屏蔽式LVDS连接器和电源供应器),只要它们能连接到接地或电源层,就可以使用。

ADN4622/ADN4624的VDDx引脚需要用100nF电容进行适当的解耦。电源供应也需要适当的滤波,以避免因高频开关噪声而产生不必要的辐射发射。

应用示例

- 高速LVDS接口 :用于模拟前端(AFE)、处理器到处理器的串行通信,或视频和成像数据的隔离。使用ADN4622/ADN4624可隔离端口、背板或电缆。

- 标准LVDS输入和输出 :允许使用现场可编程门阵列(FPGA)、接收器或耦合网络轻松集成到高速信号链中,以实现与其他物理层的接口。

- 隔离式AFE应用 :以ADN4622/ADN4624为例,提供模拟组件接口。ADN4624可同时隔离四个通道的数据,适用于高达1.25Gbps的高速带宽测量,其模拟 - 数字转换器(ADC)具有并行LVDS输出。ADN4622可隔离两个ADC通道,每个通道有四个方向,并且在使用回声时钟时可隔离ADC。这两种芯片都可用于需要串行化和解串行化(SERDES)的应用,或使用FPGA聚合大量CMOS输出以实现2.5Gbps数据通道的应用。ADN4622/ADN4624的附加相位抖动足够低,即使在隔离采样时钟时也不会影响ADC性能。此外,实现电气隔离可提高ADC性能,减少来自FPGA和特定集成电路(ASIC)电路的数字和电源供应噪声。

- PCB到PCB连接 :通过LVDS信令,可实现高带宽链路与低延迟同步数据传输。串行化的吉比特以太网连接可用于强大的扩展器或工业控制器通信模块。ADN4622具有两个方向的LVDS通道,每个通道可隔离1.25Gbps的传输和接收信号,适用于一对吉比特以太网交换机。两个通道的传播延迟在几纳秒内,为工业自动化和过程控制提供了所需的低延迟。

- 其他耦合网络 :可将ADN4624用作整体信号链的一部分,以隔离MIPI CSI - 2、DisplayPort和基于USB的协议(如FLink - L)。在应用特定集成电路中,可使用串行解串器(SERDES)通过多个ADN4624设备扩展带宽,支持1080p或4K视频分辨率,为短距离光纤提供替代方案。

-

ADN4650/ADN4651/ADN4652 5 kV/3.75 kV rms、600 Mbps双通道LVDS隔离器技术手册2025-06-03 3317

-

ADN4654/ADN4655/ADN4656 5kV RMS/3.75 kV RMS、双通道LVDS千兆位隔离器技术手册2025-05-30 4123

-

ADN4620/ADN4621 7.5 kV RMS/3.75 kV rms双通道LVDS 2.5 Gbps隔离器技术手册2025-05-29 2875

-

ADN4622能给PCIE信号做隔离吗?2024-07-03 14501

-

3 kV RMS双通道数字隔离器ADuM1280数据手册2023-11-29 506

-

ADuM4400/ADuM4401/ADuM4402:5 kV rms四通道数字隔离器数据表2021-05-22 1048

-

ADuM110N:3.0 kV rms,单通道数字隔离器数据表2021-05-15 1135

-

ADN4654/ADN4655/ADN4656:5 kV RMS和3.75 kV RMS,双通道LVDS Gigabit Sigabit数据Sheet2021-05-08 1214

-

ADuM210N:5.0 kV rms,单通道数字隔离器数据表2021-04-29 1009

-

UG-900:评估ADN4651/ADN4652 5 kV rms、600 Mbps LVDS隔离器(SOIC_W)2021-04-28 1088

-

UG-933:评估ADN4650 5 kV rms、600 Mbps LVDS隔离器(SOIC_W)2021-04-23 991

-

ADuM7440/ADuM7441/ADuM7442: 1 kV RMS四通道数字隔离器2021-03-21 1074

-

ADuM140D/ADuM140E/ADuM141D/ADuM141E/ADuM142D/ADuM142E:3.75 kV rms 四通道数字隔离器2021-03-20 1267

全部0条评论

快来发表一下你的评论吧 !