ADN4620/ADN4621 7.5 kV RMS/3.75 kV rms双通道LVDS 2.5 Gbps隔离器技术手册

描述

概述

ADN4620/[ADN4621]均为双通道、信号隔离式、低压差模信号(LVDS)缓冲器,数据速率高达2.5 Gbps,并且具有非常低的抖动。这些器件集成了ADI公司的iCoupler®技术,已针对高速运行进行了增强,可提供LVDS信号链的插入式电气隔离。与LVDS接收器和LVDS驱动器之间的交流耦合和/或电平转换允许隔离其他高速信号,例如电流模式逻辑(CML)。

ADN4620/ADN4621包括一种刷新机制,用于监控输入和输出状态,并确保它们在没有数据转换的情况下(例如上电时)保持不变。为了以低抖动实现低功耗和高速运行,隔离器电路采用1.8 V电源,3.3 V电源用于LVDS接收器,以支持全共模范围,输入电压范围为(输入共模+差分输入电压)0 V至2.4 V,如数据手册中的表2所示。

额定温度范围为宽工业温度范围,采用具有5.3 mm爬电距离的紧凑型SSOP封装(在交流电源电压下实现强化绝缘)或具有15.1 mm爬电距离的宽SOIC_IC封装(增强的高工作绝缘电压高达1500 V峰值)。

数据表:*附件:ADN4620 ADN4621 7.5 kV RMS 3.75 kV rms双通道LVDS 2.5 Gbps隔离器技术手册.pdf

应用

- 模拟前端隔离

- 数据平面隔离

- 隔离高速时钟和数据链路

- 多千兆位序列化/反序列化 (SERDES)

- PCB对PCB光纤更换(例如:短距离光纤)

特性

- 7.5 kV rms/3.75 kV rms LVDS隔离器

- 符合TIA/EIA-644-A LVDS信号电平标准

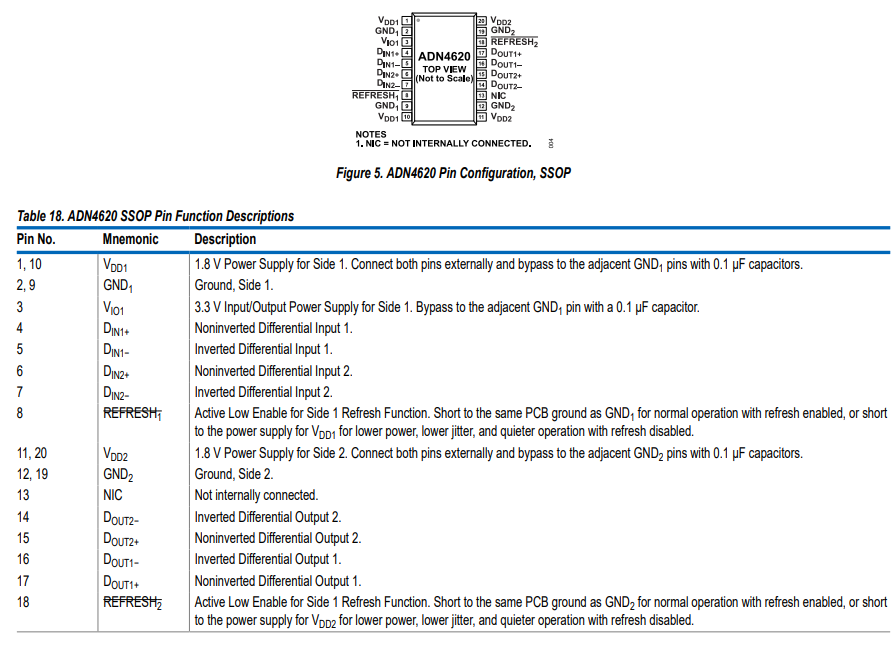

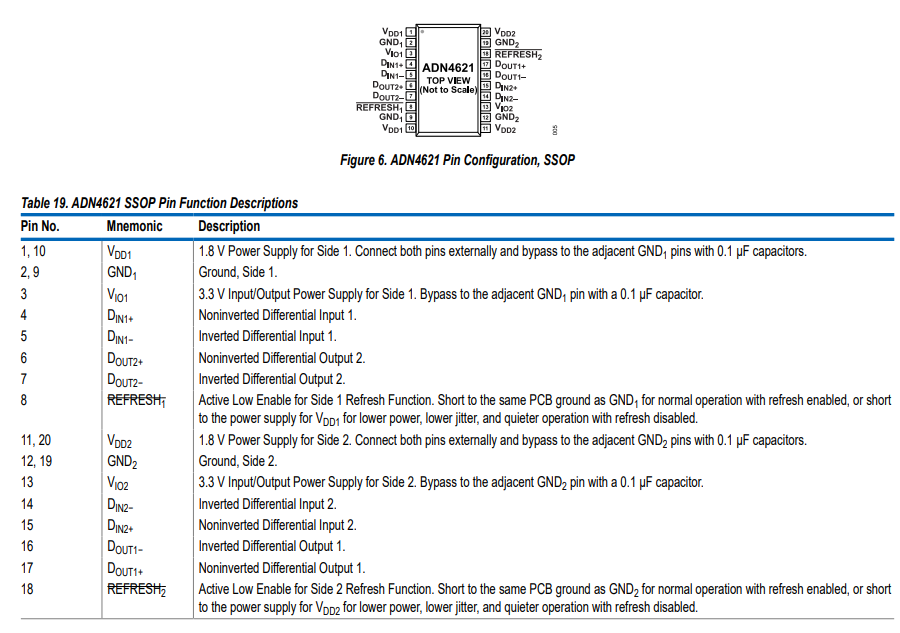

- 双通道配置(ADN4620:2 + 0,ADN4621:1 + 1)

- 任何数据速率支持高达2.5 Gbps开关频率,具有低抖动特性

- 两个通道的总带宽为5 Gbps

- 2.15 ns传输延迟(典型值)

- 典型抖动:0.82 ps rms(随机),40 ps(总峰峰值)

- 低功耗1.8 V电源和用于I/O的3.3 V电源

- 高达±8 kV的IEC 61000-4-2 ESD隔离栅保护

- 高共模瞬变抗扰度:70 kV/μs(典型值)

- 安全和法规认证(16引脚SOIC_IC封装)

- UL(申请中):1分钟7500 V rms,符合UL 1577

- CSA元件验收通知5A(申请中)

- VDE合规证书,强化绝缘(申请中)

- DIN V VDE V 0884-11 (VDE V 0884-11):2017-01

- V

IORM= 1500 VPEAK(最大工作绝缘电压)

- 使能或禁用刷新(20引脚SSOP封装)

- 工作温度范围:−40°C至+125°C

- 具有5.3 mm爬电距离的紧凑型SSOP封装或具有15.1 mm爬电距离的宽SOIC_IC封装

引脚配置描述

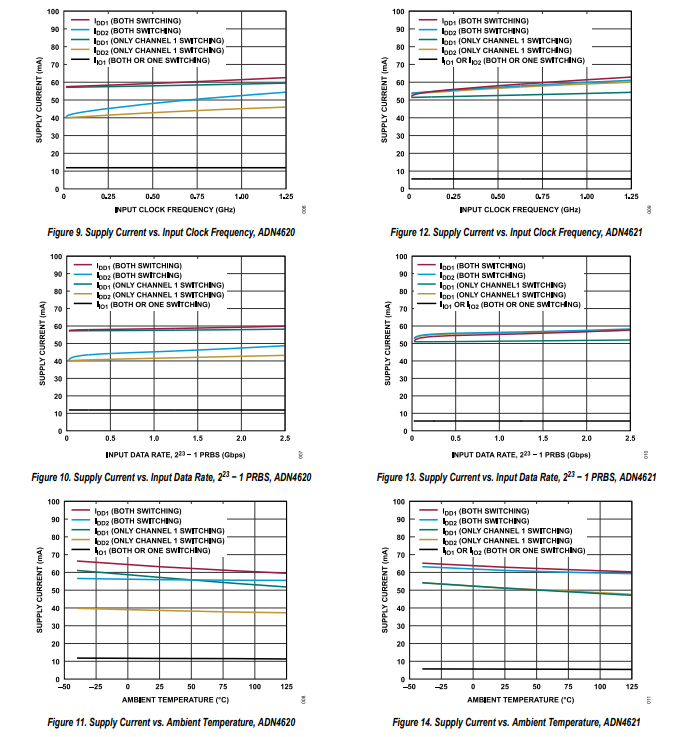

典型性能特征

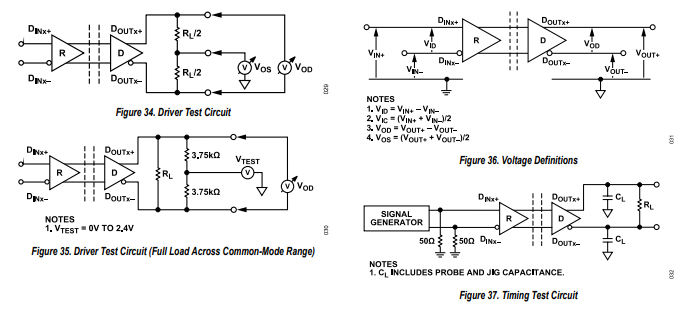

测试电路和开关特性

工作原理

隔离与刷新

ADN4620/ADN4621是高速差分信号隔离器,能够以高达2.5Gbps的速率切换,信号电平符合TIA/EIA - 644 - A标准。这些器件将施加到LVDS接收器输入端的差分信号,通过隔离栅耦合到另一侧,并以LVDS形式重新传输比特流或时钟。这种集成方式允许LVDS信号链的中断隔离,以及对其他信号(如CML)的隔离。

LVDS接收器检测LVDS输入上端接电阻两端存在的差分电压。集成数字隔离器将输入状态传输到隔离栅另一侧,LVDS驱动器输出与输入相同的状态。

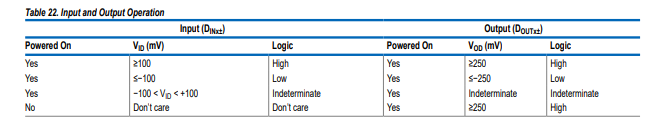

当在任意DIn+引脚和对应的DIn-引脚之间存在+100mV的正差分电压时,对应的DOut+引脚会流出电流。该电流通过连接的传输线和端接电阻流动,而DOut-引脚吸收回流电流。当在任意DIn+引脚和对应的DOut-引脚之间存在-100mV的负差分电压时,对应的DOut+引脚吸收电流,而DOut-引脚流出电流。表22总结了这些输入和输出组合。

该输出驱动电流为±2.5mA和±4.5mA(典型值为±3.1mA),在100Ω端接电阻(RT)上产生±250mV和±450mV的电压。接收电压以1.2V为中心。由于差分电压(VD)会反转极性,跨越RT的电压摆幅是差分电压幅值(|VD|)的两倍。

为响应集成LVDS接收器检测到的输入状态变化,编码器电路会发送窄(~1ns)脉冲,以触发解码器,使输出LVDS驱动器缓冲器输出恢复到正常工作状态,反映隔离的LVDS输入状态。

对于ADN4620/ADN4621的正常运行,SSOP封装型号上的低电平有效使能引脚(ENABLE1和ENABLE2)分别短接到相应的电源(VDD1和VDD2),以启用刷新功能。启用此功能后,解码器会在检测到输入状态变化超过约1μs时,发送周期性刷新脉冲(指示输入逻辑转换),包括故障安全输出状态(如适用)。此功能在SOIC封装型号上永久启用,用于SOIC。

上电时,输出状态初始为正确状态,若无输入转换,在1μs内由刷新脉冲校正。

如果解码器在超过约1μs的时间内未接收到内部脉冲,器件会认为输入侧未通电或无功能,此时输出将设置为正差分电压(逻辑高电平)。

对于时钟、恒定比特流或协议,如果错误校正,刷新功能可能不需要。如果SSOP封装型号上的ERROR1和ERROR2引脚以及REFRESH1和REFRESH2引脚短接到相应的电源(VDD1和VDD2),则刷新功能将被禁用,允许在无内部时钟信号(可能会减少传导或辐射发射)的情况下运行。在此模式下,可能需要在输入侧或连接的输出侧进行数据转换,甚至在超过保证的共模瞬态抗扰度规范的电源上电后,也可能需要进行共模输出状态事件。

真值表

LVDS标准TIA/EIA - 644 - A定义了两种正常接收器工作条件:输入差分电压为+100mV对应一种逻辑状态,-100mV对应另一种逻辑状态。在这些阈值之间,标准允许接收器检测任一逻辑状态,如表22所示。

-

Analog Devices Inc. ADN4620和ADN4621 LVDS 2.5Gb隔离器数据手册2025-06-20 2463

-

ADN4650/ADN4651/ADN4652 5 kV/3.75 kV rms、600 Mbps双通道LVDS隔离器技术手册2025-06-03 3206

-

ADN4654/ADN4655/ADN4656 5kV RMS/3.75 kV RMS、双通道LVDS千兆位隔离器技术手册2025-05-30 4000

-

ADN4622/ADN4624 5.7 kV rms/1.5 kV rms、四通道 LVDS 2.5 千兆位隔离器技术手册2025-05-29 4733

-

ADN4621是否支持单端LVDS信号传输?是否还能支持单端的LVDS(单线LVDS)信号隔离?2024-05-27 13500

-

3 kV RMS双通道数字隔离器ADuM1280数据手册2023-11-29 487

-

ADuM110N:3.0 kV rms,单通道数字隔离器数据表2021-05-15 1087

-

ADN4654/ADN4655/ADN4656:5 kV RMS和3.75 kV RMS,双通道LVDS Gigabit Sigabit数据Sheet2021-05-08 1175

-

ADuM210N:5.0 kV rms,单通道数字隔离器数据表2021-04-29 978

-

UG-900:评估ADN4651/ADN4652 5 kV rms、600 Mbps LVDS隔离器(SOIC_W)2021-04-28 1062

-

UG-933:评估ADN4650 5 kV rms、600 Mbps LVDS隔离器(SOIC_W)2021-04-23 969

-

ADuM120N/ADuM121N: 3.0 kV rms双通道数字隔离器2021-03-21 953

-

ADN4652 5 kV/3.75 kV rms、600 Mbps双通道LVDS隔离器2019-02-22 895

全部0条评论

快来发表一下你的评论吧 !