基于FPGA芯片和RISC在图像驱动中的应用

可编程逻辑

描述

随着亚微米技术的发展,FPGA芯片密度不断增加,并以强大的并行计算能力和方便灵活的动态可重构性,被广泛地应用于各个领域。但是在复杂算法的实现上,FPGA却远没有32位RISC处理器灵活方便,所以在设计具有复杂算法和控制逻辑的系统时,往往需要RISC和FPGA结合使用。这样,电路设计的难度也就相应大大增加。随着第四代EDA开发工具的使用,特别是在IP核产业的迅猛发展下产生的SOPC技术的发展,使嵌入RISC的通用及标准的FPGA器件呼之欲出。单片集成的RISC处理器和FPGA大大减小了硬件电路的复杂性和体积,同时也降低了功耗、提高了系统可靠性。Altera公司的EPXAl0芯片就是应用SOPC技术,集高密度逻辑(FPGA)、存储器(SRAM)及嵌入式处理器(ARM)于单片可编程逻辑器件上,实现了速度与编程能力的完美结合。本文所介绍的图像驱动和处理系统正是应用了EPXAl0的这些特点,充分发挥了FPGA逻辑控制实现简单、对大量数据做简单处理速度快的优势以及ARM软件编程灵活的特点。

1 内嵌ARM核的FPGA芯片EPXA10及其主要特点

EPXAl0单片集成了ARM核、高密度的FPGA、存储器及接口和控制模块,不仅简化了ARM与FPGA之间的通讯,也使片外扩展存储器以及和外设通讯变得相对简单;同时通过在FPGA中嵌入各种IP核和用户控制逻辑可以实现各种接口和控制任务。这样的高度集成化不仅大大加快了ARM与片内各种资源的通讯速度,而且减小了硬件电路的复杂性、体积和功耗,真正实现了SOPC。

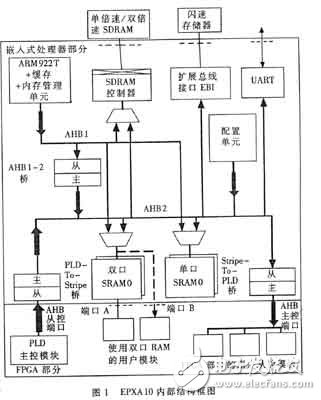

EPXAl0内部结构框图如图1所示式,主要分为嵌入处理器和FPGA两部分。

1.1嵌入式微处理器ARM922T

EPXAl0嵌入式处理器部分集成了业界领先的32位ARM处理器(ARM922T),工作频率可达200MHz;支持32位ARMv4T指令集和16位Thumb扩展指令集;具有全性能的内存管理单元以及8K的指令缓存和8K数据缓存,以支持实时操作系统(RTOS)、C语言和汇编语言。

1.2高密度的FPGA

EPXAl0片内FPGA部分具有1000000门可编程逻辑、3MB的内置RAM和512个可供用户使用的I/0管脚,可以通过嵌入各种IP核实现各种标准工业接口(如PCI、USB等)。

1.3先进的存储支持

EPXAl0嵌入式处理器部分集成了256KB单口SRAM和128KB双口SRAM;同时集成了两个先进的存储支持:(1)SDRAM控制器,用于控制单倍速/双倍速SDRAM。SDRAM的各种工作状态是依据信号线上提供的不同控制时序来确定的,实现起来非常复杂。有了SDRAM控制器的支持,只需要在Altera公司提供的EDA开发软件Quartus II中设置好SDRAM工作所需的各种参数,就可以按照直接给出指令、地址和数据的方式对SDRAM进行操作,控制器会自动将各种指令转化成SDRAM所需的工作时序,大大降低了对SDRAM的控制难度。(2)扩展总线接口(EBl),可外接4个存储设备,如闪速存储器、SRAM等,总容量高达128MB。其中EBI接口0外接闪速存储器,用于存储用户的软件、硬件设计代码。

1. 4方便的接口模块

EPXAl0嵌入式处理器部分嵌入了串口通讯模块(UART),可以不用编程直接实现ARM与超级终端之间的串行通讯,实时监视软件的运行情况。如果要实现计算机与ARM之间的数据传递存储,只需用户编写基于VC++语言的串口通讯程序,这需要用到Microsoft公司提供的MSComm串行通讯控件。

1.5灵活的启动方式

EPXAl0共有两种启动方式:(1)从ARM启动。这种启动方式需要将设计下载到片外闪速存储器中,而且设计中必须包含对ARM的应用。启动时ARM为主动,配置各种寄存器及FPGA,执行软件代码。(2)从FPGA启动。这种启动方式需要将设计下载到片外E2PROM中,而且设计中可以只包含FPGA部分的应用。启动时PP-GA为主动,ARM处于复位状态,配置完成后,如果有对ARM的应用,则ARM解除复位,执行软件代码;反之,ARM一直处于复位状态。

2 EPXAl0的工作方式

EPXAl0嵌入式处理器部分提供了两条32位AMBA微控制器总线AHB1、AHB2,分别用于片内各种资源的通讯,如图1所示。基于AHB1、AHB2总线,EPXAl0的工作方式大致可分为三种:(1)ARM作为AHB1总线的主控,直接访问AHB1总线的从属资源,包括SDRAM控制器、片上SRAM、中断控制器等。(2)ARM作为AHB1总线的主控,通过AHBl-2桥访问AHB2总线上

的从属资源,包括UART、E-BI、SRAM、Stripe-To-PLD桥等,同时通过Stripe-To-PLD

桥对FPGA进行访问和控制。(3)FPGA通过AHB2的总线主控PLD-To-Stripe桥访问AHB2总线上的从属资源,包括SRAM、SDRAM控制器、UART等。

EPXAl0片内集成了软件可编程锁相环路(PLL),为微控制器总线及SDRAM控制器提供了灵活精确的时钟基准。

3 EPXAl0在图像驱动和处理方面的应用

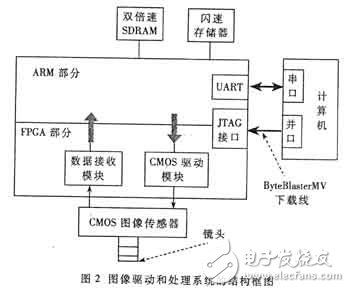

本文所述的图像驱动和处理系统主要利用FPGA逻辑控制实现简单、对大量数据做简单处理速度快以及ARM软件编程灵活的特点,系统框图如图2所示。在芯片FPGA部分,构造了CMOS驱动模块,驱动CMOS图像传感器使之能够采集图像数据。然后图像数据经数据接收模块存入片外SDRAM中,并经串口传人PC机,要将图像数据在PC机中显示成图像,还需编写基于CDib类的图像显示程序;同时将图像数据经芯片ARM部分的图像处理算法(本系统采用Sobel算子)处理,处理后的图像数据才能经串口传给PC机进行显示。为了验证基于ARM的图像处理算法实现的正确性,还将这一算法在PC机中进行了实现,最后针对同一幅图像,将两种实现的结果进行了比较。

3.1图像的驱动

3.1.1 CMOS图像传感器的驱动

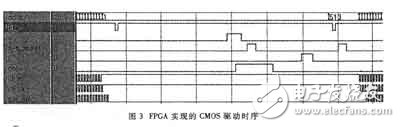

要使CMOS图像传感器成像,必须设计正确。的驱动时序,包括行同步、列同步、场同步及曝光时间设定等时序。利用FPGA逻辑编程简单的特点,用硬件描述语言Verilog HDL编程,可在FPGA中实现CMOS图像传感器的驱动时序,该驱动时序的仿真结果如图3所示。图中,ld_y为行选通信号;ld_x为列选通信号;cal为场选通信号;clk_adc为内部A/D转换器所需的时钟;addr为行列地址线;sys_reset为曝光时间设定信号;s和r为内部放大器选通信号。

3.1.2图像的采集

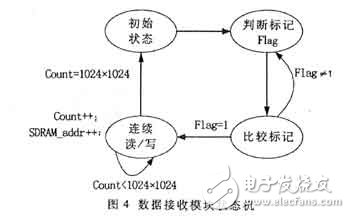

CMOS图像传感器输出的信号为数字信号(即数字图像数据),所以图像的采集要通过FPGA中的数据接收模块将图像数据保存到片外SDRAM中。数据接收模块状态机如图4所示。标志Flag为1,开始采集数据。因为CMOS图像传感器在每个A/D转换时钟周期输出一个数据(如图3所示),接收模块也相应地设计成一个时钟接收周期接收一个数据(Burst状态),这样也就发挥了FPGA对大量数据处理速度快的优势。

3.1.3图像的显示

ARM将SDRAM中的图像数据经串口传给计算机,在计算机中用VC++语言编写串口协议和图像显示程序,将CMOS图像传感器采集到的图像显示在屏幕上,以便于监测验证。

3.2图像的处理

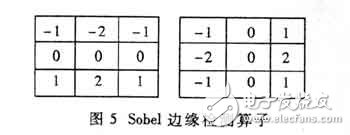

本系统采用的图像处理算法基于Sobel边缘检测算子。图像的边缘是由灰度不连续性所反映的,是图像的最基本信息。边缘检测算子检查每个像素的邻域并对灰度变化率进行量化,也包括方向的确定,大多数使用基于方向导数掩模求卷积的方法。就sobel算子而言,如图5所示,采用了两个3×3卷积核形成边缘算子模板,紧邻中心像素的像素有4个,和中心像素成斜对角的像素也有4个,距离中心像素近的模板值的系数为2,成斜对角的比较远,所以其系数为1,该系数反映了这样一点:邻域对当前像素的灰度梯度的影响程度越近影响越大,越远影响越小。图像中的每个点都用这两个核做卷积,一个核对垂直边缘响应最大,而另一个核对水平边缘响应最大,两个卷积的最大值作为该点的输出位,反映了当前位置灰度梯度(图像边缘)的主要方向和大小。运算结果反映了一幅边缘幅度图像。

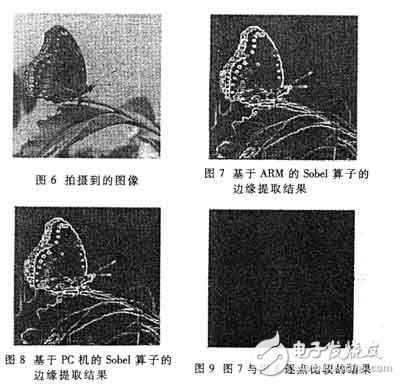

因为拍摄的图像为1024×1024,采用的Sobel算子为3x3模板,所以图像周边的一圈像素(第1行、第1024行、第1列、第1024列)保持原灰度值。在图像的第2行2列到1023行1023列的范围内,用图5所示的算子模板进行扫描计算,即当前像素和与当前像素相邻的8个像素,分别与模板中位置相应的9个系数相乘,累加这9个乘积结果,就得到针对某一方向的灰度梯度。比较两个方向的计算结果,取最大者作为当前位置的灰度梯度。图7为图6经过Sobel算子进行边缘提取后得到的图像。该算法在ARM中是基于C语言实现的,体现了ARM软件编程灵活的特点。

3.3试验结果

图6是成功驱动CMOS图像传感器后拍摄的景物图像,可见图像非常清晰。本文分别针对Soble算子进行了基于PC机和基于ARM的实现,图7为图6经过ARM中的Sobel算子的边缘提取结果,图8为图6经过PC机中Sobel算子的边缘提取结果,图9为图7和图8逐像素的比较结果。可见两种实现方法得到的结果完全一致,说明了基于ARM的Sobel算子的实现是正确的。

上述图像驱动和处理系统如果仅用FPGA来实现,算法部分的实现会比较复杂;如果仅用ARM来实现,驱动时序的设计也会非常困难。而采用内嵌ARM核的FPGA芯片EPXAl0,单片就实现了上述系统,大大减小了设计的难度和电路的复杂性,同时也减小了硬件电路的体积和功耗,在系统小型化方面有着独特的优势。由于EPXAl0集成了先进的ARM922T处理器器以及高密度的FPGA,所以在不增加体积和改进硬件电路的情况下,可以实现更加复杂的图像处理算法和硬件控制逻辑设计,具有很强的系统扩展潜力。这种嵌入式方案必将成为集成电路的发展趋势,将会在未来较短的时间里得到快速的发展。

-

FPGA 实时信号处理应用 FPGA在图像处理中的优势2024-12-02 2864

-

FPGA在图像处理领域的优势有哪些?2024-10-09 9493

-

risc-v在人工智能图像处理应用前景分析2024-09-28 1095

-

FPGA中如何使用Verilog处理图像2021-09-23 7647

-

在芯片设计中FPGA的优势是什么?2021-05-10 2662

-

如何使用FPGA实现图像数据采集卡及其驱动设计2021-02-03 1661

-

DSP芯片及其在图像技术中的应用2017-10-21 1404

-

基于FPGA的实时图像预处理技术在汽车夜视系统中的应用2016-08-29 624

-

实时图像处理FPGA芯片怎么选择2012-08-06 9246

-

基于FPGA的LCoS驱动和图像处理系统设计2011-06-28 2520

-

LOG算子在FPGA中的实现2011-05-16 1320

-

FPGA芯片EPXA10在图像处理中的应用2010-07-10 1301

-

FPGA在步进电机任意细分驱动中的应用2010-05-11 657

-

内嵌ARM核的FPGA芯片EPXA10及其在2006-04-16 1629

全部0条评论

快来发表一下你的评论吧 !