arm架构的芯片memory及智能机存储部件简述

电子说

描述

处理器系统中可能包含多种类型的存储部件,如Flash、SRAM、SDRAM、ROM以及用于提高系统性能的Cache等等。刚刚接触芯片开发的工程师常常被各式各样的存储和存储管理弄得晕头转向,因此本文简单对ARM架构和基于ARM架构处理器系统中可能包含多种类型的存储部件,如Flash、SRAM、SDRAM、ROM以及用于提高系统性能的Cache等等。刚刚接触芯片开发的工程师常常被各式各样的存储和存储管理弄得晕头转向,因此本文简单对ARM架构和基于ARM架构的处理器上的内存及内存管理做一个简单的汇总和整理。文章首先阐述了内存的分类,其次ARM920T为例描述了ARM芯片包含的存储部件和存储管理单元,最后简单阐述了智能机中的存储部件。

一,存储部件的分类

1,RAM(Random Access Memory)-随机存取存储器

RAM在任何时候都可以被读写,通常作为操作系统或其他正在运行程序的临时存储介质(内存,掉电后RAM不能保留数据。RAM有SRAM、DRAM两大类。

SRAM(Static RAM/SRAM)写入的数据不会消失,直到下次写入或掉电,是目前读写最快的存储设备,价格昂贵,只用于要求苛刻的地方,如Cache。

DRAM(Dynamic RAM/DRAM)保留数据时间短,速度比SRAM慢,但快于其他任何ROM,比SRAM便宜很多,常用于计算机内存。DRAM种类很多,常见的有FPRAM/FastPage、EDORAM、RDRAM、SGRAM、SDRAM、DDR RAM等。

SDRAM(Synchronous DRAM)同步动态随机存储器,是一种改善了结构的增强型DRAM。SDRAM的接口相对复杂,需要相应的控制器支持,但由于容量大、价格便宜、访问速度快,所以常用在对内存容量和处理速度要求高的应用场合,在这种场合中,相应的处理器(CPU)都自带有SDRAM控制器。

DDR RAM(Date-Rate RAM)也称作DDR SDRAM,是目前电脑中用得最多的内存,这种改进型的RAM和SDRAM是基本一样的,但是它数据传输速率加倍了,一个时钟内可以进行两次数据书读写。

2,ROM(Read Only Memory)--只读存储器

ROM可在任何时候读取,断电后能保留数据,数据一但旦写入只能用特殊方法更改或无法更改。因此ROM相当于PC机上的硬盘,用来存储和保存数据。嵌入式系统中ROM常用来存放可执行文件映像。RAM和ROM相比,两者的最大区别是RAM在断电以后保存在上面的数据会自动消失,而ROM就不会。随着ROM存储介质发展,应用中经常提到的有ROM、PROM、EPROM、2PROM。

ROM:Read Only Memory,只读存储器。ROM中内容只能读不能改,在工厂里通过特殊的方法将数据烧录进去。

PROM:Programmable ROM,可编程ROM。可通过专用的编程器将数据写入,但是只可写一次,一旦写入再无法修改。

EPROM:Erasable Programmable ROM,可擦除可编程ROM。芯片写入要用专用的编程器,可重复擦除和写入,擦除通过紫外线照射实现。

EEPROM:Electrically Erasable Programmable ROM,

电可擦除可编程ROM。价格高,写入慢。但其写入、擦除不需借助其它设备,电子信号即可实现。用厂商提供的专用刷新程序并利用一定的编程电压就可以轻而易举地改写内容。手机软件一般放在EEPROM中,我们打电话,有些最后拨打的号码,暂时是存在SRAM中的,不是马上写入通过记录(通话记录保存在EEPROM中),因为当时有很重要工作(通话)要做,如果写入,漫长的等待是让用户忍无可忍的。

3,FLASH存储器(闪存)

FLASH结合了ROM和RAM的长处,不仅具备电子可擦出可编程(EEPROM)的性能,断电也不会丢失数据。同时数据可以快速读取,U盘和MP3以及现在的智能手机里用的就是这种存储器。过去,嵌入式系统一直采用ROM(EPROM)作存储设备,近年来Flash则将其全面代替,被用来存储Bootloader、操作系统或者程序代码。目前Flash主要有两种:NOR Flash和Nand Flash 。

NOR Flash带有SRAM接口,有足够的地址引脚来寻址,可以很容易地存取其内部的每一个字节。 NOR Flash的特点是芯片内执行(XIP, eXecute In Place),用户可以直接运行装载在NOR FLASH里面的代码,不必再把代码读到系统RAM中。NOR Flash的传输效率很高,在1~4MB的小容量时具有很高的成本效益,但是很低的写入和擦除速度大大影响了它的性能,同时成本较高。

NAND Flash没有采取内存的随机读取技术,它的读取是以块的形式来进行,通常一个块大小为512个字节,Nand Flash比较廉价,用户不能直接运行NAND Flash上的代码。应用NAND的困难还在于flash的管理和需要特殊的系统接口,它使用复杂的I/O口来串行地存取数据,各个产品或厂商的方法可能各不相同。

Nand Flash一般采用两种不同的类型。一种叫做SLC(Single Level Cell),单层单元闪存;第二种叫做MLC(Multi Level Cell),多层单元闪存。两者的主要区别是SLC每一个单元储存一位数据,而MLC通过使用大量的电压等级,每一个单元储存两位数据,数据密度比较大。SLC成本较高,但性能优、能耗低、重复擦写次数多。

嵌入式开发中,因为NOR Flash多用来存储启动代码、操作系统等重要信息,而大容量的用NAND FLASH。

4,SD/MMC

MMC(MultiMedia Card)卡,是一种快闪存储器卡标准。在1997年由西门子及SanDisk共同开发,技术基于东芝的NAND快闪记忆技术。SD卡(Secure Digital Memory Card)是一种为满足安全性、容量、性能和使用环境等各方面的需求而设计的一种新型存储器件,在MMC卡基础上发展而来。SD/MMC的存储介质就是NAND FLASH。

二,ARM架构上的内存和内存管理部件

嵌入式开发中常常使用多种类型的组合实现来降低成本、提高效率。如Rom+RAM+Nand Flash的组合,基本的引导代码放在ROM中,系统加电即自动从Rom初始地址开始执行,而后分阶段(一阶段或两阶段)将bootloader代码、RTOS和应用程序代码复制至RAM中执行。程序代码之类一定是放在一种可以掉电不失数据的存储设备中,笼统的将之称为ROM。传统的嵌入式开发中由于代码量和数据量很少,一般内部EEROM即够用。后来由于代码量、数据量太大,EERom存不下来,就出现了Flash。由于Flash不能直接与CPU交换数据或交换很慢,所以在程序运行后,需要将Flash内部的某一要运行的程序,“搬移”到能够和处理器直接交换数据的RAM中去执行。当程序被搬运(也许只搬运了部分)到ram中后,就开始从ram的首地址开始运行程序。为了提高利用率,一般会将向量表之类的需要快速响应的部分放到ram中;当然若ram够大,也可以将所有的代码放到RAM中。芯片中,存储部件间程序和数据的“搬移”、CPU core与主存间通信就是通过处理器的各种内存管理单元来实现。

芯片上所有的片内、片外存储都统一管理,存在一个系统存储器分配映射,其不仅是存储器块可用地址和I/O设备可使用地址的反映,也是系统中硬件存储器和I/O设备描述的反映。它反映了不同存储单元ROM、RAM、Flash和I/O设备等的存在性,每种存储部件有各自的开始和结束地址;也反映了定位器对程序、数据、I/O操作的存储器分配。不同的存储单元之间存在着空间间隔以方便扩展,扩展时只需改动软件程序即可。

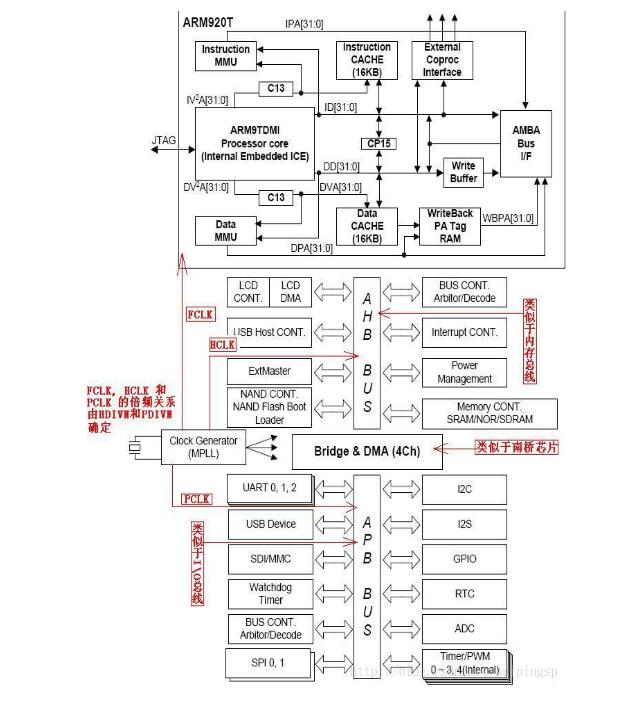

如下图是ARM920T的逻辑框图

1,寄存器

对于寄存器,它不是ram,可以理解成ram,寄存器的速度是最快的,是处理器运算的临时空间,内存的数据和信息都是经过它来参加CPU内逻辑运算单元或算术运算单元的。

2,Cache

高速缓存存储器是一个硬件部件,SRAM,对用户来说是透明的。Cache与主存以Cache Line为单位交换数据。Cache的地址映像和变换方法有三种:直接相联、全相联和组相联映像。Cache与一些写回、写通技术结合来提高系统效率的同时保持Cache和主存数据的一致性。

在ARM920T有16K的数据Cache和16K的指令Cache,这两个Cache是基本相同的,数据Cache多了一些写回内存的机制,后面我们以数据Cache为例来介绍Cache的基本原理。我们已经知道,Cache中的存储单位是Cache Line,ARM920T的一个Cache Line是32字节,因此16K的Cache由512条Cache Line组成。

多核心的架构下,每个处理器都会有自己的L1Cache,并共享一个L2 Cache。ARM采用CacheCoherence机制保证Cache的同步。

3,MMU(Memory Management Unit)- 内存管理单元

MMU负责虚拟地址到物理地址的映射,并提供硬件机制的内存访问权限检查。MMU使得每个用户进程拥有自己独立的地址空间,并通过内存访问权限的检查保护每个进程所用的内存不被其他进程破坏。

ARM CPU地址转换涉及三种地址:虚拟地址(VA,Virtual Address)、变换后的虚拟地址(MVA,Modified Virtual Address)、物理地址(PA,Physical Address)。MMU没有使能时,CPU核心、cache、MMU、外设等所有部件使用的都是物理地址。启动MMU后,CPU核心对外发出虚拟地址VA,VA被转换为MVA供cache、MMU使用,在MMU里MVA被转换成PA,最后使用PA读取实际设备。

从MVA到PA的转换需要访问多次内存,转译查找缓存(Translation Lookaside Buffers,TLB)用来改进CPU访问内存的性能。由此,通过使用这样一个高速、容量相对较小的存储器来存储近期用到的页表条目(段、大页、小页、极小页描述符),避免每次地址转换都到主存中查找,这样就大幅提高性能。这个存储器用来帮助快速地进行地址转换,成为当CPU发出一个虚拟地址时,MMU首先访问TLB。如果TLB中含有能转换这个虚拟地址的描述符,则直接利用此描述符进行地址转换和权限检查,否则MMU访问页表找到描述符后再进行地址转换和权限检查,并将这个描述符填入TLB中,下次再使用这个虚拟地址时就直接使用TLB用的描述符。

使用TLB需要保证TLB中的内容与页表一致,在启动MMU之前,页表中的内容发生变化后,尤其要注意。一般的做法是在启动MMU之前使整个TLB无效,改变页表时,使所涉及的虚拟地址对应的TLB中条目无效。

4,协处理器CP15

在基于ARM的嵌入式系统中,存储器常用协处理器CP15完成存储单元的大部分管理工作。例如通过专用指令写CP15控制寄存器相应位来使能和控制内存管理单元MMU和Cache。

5,Nand Flash controller和Flash

操作NAND Flash时,先传输命令,然后传输地址,最后读写数据,这个期间要检查Flash的状态。

NAND Flash的读写操作次序如下:

①设置NFCONF配置NAND Flash

②向NFCMD寄存器写入命令

③向NFADDR寄存器写入地址

④读写数据:通过寄存器NFSTAT检测NAND Flash的状态,在启动某个操作后,应该检测R/nB信号以确定该操作是否完成、是否成功。

Flash相当于PC的硬盘,用于永久存放数据,可以将部分引导程序、可执行映像存放在Flash中,在系统加电后通过Bootloader加载至RAM。

6,DMA(Direct Memory Access)- 直接存储器存取

DMA用来提供在外设和存储器之间或存储器和存储器之间的高速数据传输。无须CPU干预,数据可以通过DMA快速地移动,这就节省了CPU的资源。

7,ROM(内部Rom和外部Rom),用于存放系统启动和初始化代码、RTOS等。

8,RAM(分内部IRAM和外部RAM),相当于PC的主存,用于任务执行过程中的临时数据、代码存储和堆栈。执行频率高的代码、数据存于IRAM。系统启动后ROM中的影像端copy至RAM并执行。

9,I/O端口和设备地址空间:该地址由处理器根据硬件配置分配,包括控制/数据/状态寄存器。

三,智能机应用处理器AP和无线路由器CP的存储部件配置

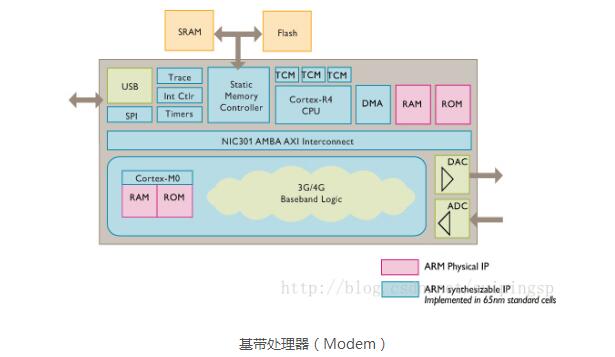

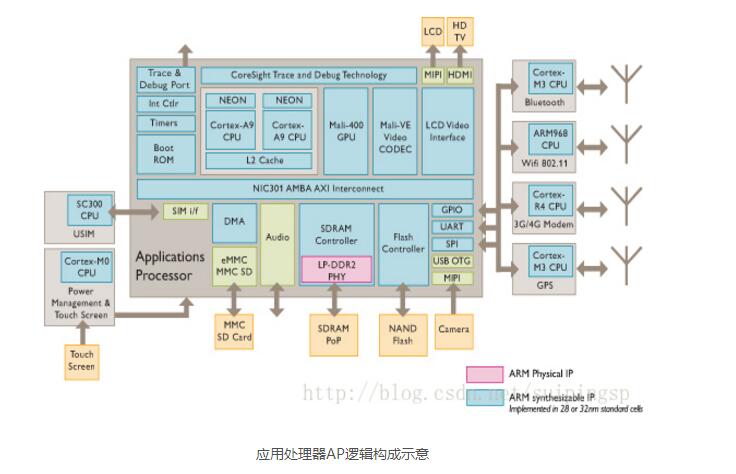

下面两幅图是ARM提供的当前典型的ARM架构的无线modem和 应用处理器AP的逻辑示意图

图中的ROM、RAM组合用来实现系统代码的存放和启动、运行。另外一些应用场景中(如功能机)modem需要额外的存储部件,即通过Static Memory Controller外接Flash等实现。

TCM是一个固定大小的RAM,紧密地耦合至处理器内核,提供与cache相当的性能,相比于cache的优点是,程序代码可以精确地控制什么函数或代码放在那儿(RAM里)。当然TCM永远不会被踢出主存储器,因此,他会有一个被用户预设的性能,而不是象cache那样是统计特性的性能提高。

AP示意图中列出了当下流行的存储部件和存储控制器组合,实际上这些控制部件不一定同时存在于一颗AP上。当我们谈到智能机的“内存”时,实质上指的往往是应用处理器的存储配置。下文会简述智能机中的存储部件组合。

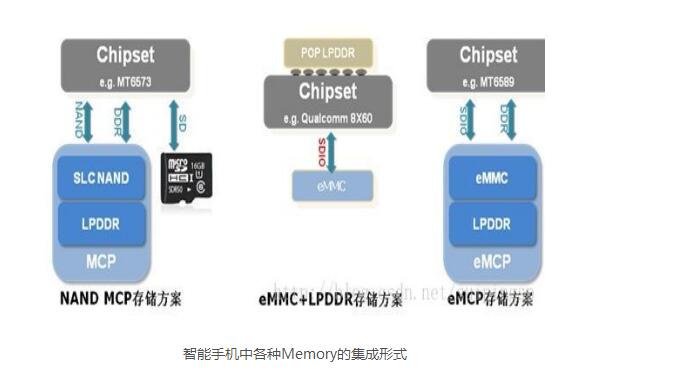

手机的Memory由两大块组成,俗称RAM与ROM。RAM也叫运行内存,其大小决定手机后台能运行多少程序;ROM的大小则决定手机中能安装多少程序、放多少歌曲、电影、小说等。RAM则是上面提到的DRAM,对智能手机的性能影响最大、价格也贵,特别是目前新一代的LPDDR2的价格,同等容量时比电脑中采用的PC DDR3的价格贵一倍左右。今年底,下一代LPDDR3也将被一些高端平台采用,价格将更昂贵。ROM实质上是Nand Flash闪存,用来永久存储智能手机中的各种数据。而RAM与ROM如何结合、如何封装则是目前手机厂商在选择平台时最为纠结的地方,因为涉及到PCB的布线和空间位置,不仅如此,还涉及到后面物流采购的可行性与价格的波动,因为不同形式的Memory价格波动也不一样。目前主流的形式有MCP、eMCP、POP(Package on Package)以eMMC+LPDDR2的分商方式,手机采用哪一种形式往往是由手机选择的主芯片平台来决定,而容量则由手机厂商根据市场需求和自己的产品定义来决定。有些手机厂商在将其它配置都定义得较高,为了省成本选择了512MB的RAM,这对用户是一种不负责的态度。目前512MB的RAM与2GB的RAM价格差了十几美元。

低端机一般是一颗主芯片(与AP集成的SoC)配一个Flash+DRAM。Flash与DRAM封一起,称为ND MCP。这里Flash是NandFlash,一般采用的SLC目前主要的配置有两种:一种是ND 4Gb+2Gb;另一种是ND4Gb+4Gb。前者也即厂商通俗所称的512MB ROM+2RAM,目前价格约为4.2-4.5美元;后者也即厂商所报的512MB ROM+4RAM,目前报价约为7-7.5美元。现在主流低端智能机已采用第二种了。低端机的512MB ROM不能支持Android 4.0。

中端智能机是由一颗主芯片(AP与集成)配一个eMMC和一颗DRAM。所谓eMMC是集成了闪存控制器,eMMC=NAND Flash+闪存控制芯片+标准接口封装,这样的最大好处是BB/CPU主控IC不需要再面对不同厂商的闪存的兼容性问题,以及闪存技术不断升级带来的接口兼容性问题,当然,Flash与控制器集成还有很多好处,这里就不一一描述了,昌旭在去年曾写过一文专门谈eMMC的好处。并且,由于目前智能手机PCB上占位面积有限,三星等厂商将eMMC与DRAM封在一起,称为eMCP。

今天主要谈价格。目前的中端智能机(1500元-1999元)的主要配置也有两种:一种是4GB eMMC+4Gb DRAM(注意,这时是大写GB,且闪存采用了MLC)

最后,再看看苹果三星这种高端配置的手机。这种手机一般采用与AP分离的方式,eMMC供与AP,上不再需要NOR Flash,而AP上还需要堆叠一颗DRAM(目前主要是LPDDR2)。所以,eMMC与DRAM也是分开的。eMMC的配置主流有16/32/64GB。

-

无线收发系统架构简述2023-05-09 1771

-

Arm架构安全技术介绍中,安全core不能访问除共享memory之外的非安全memory?2022-09-23 3414

-

Arm架构内存的加密与验证是在之前提到的memory filter上进行的吗2022-09-02 2949

-

ARM的体系架构基本概念2022-01-25 1357

-

ARM架构简述-精简版#嵌入式开发韦东山 2022-01-04

-

ARM架构基础知识点汇总2021-12-13 1876

-

介绍一下ARM架构2021-11-25 1501

-

ARM架构2021-08-04 2341

-

ARM芯片架构2021-07-28 2449

-

arm架构的芯片有哪些2021-07-21 2364

-

详谈ARM架构、ARM内核发展史2021-07-01 1506

-

基于 RFID 和 ARM 架构的医疗器械智能控制系统2020-01-07 1929

-

集中式服务器架构和基于ARM微服务器架构的存储差别在哪?2018-12-27 1097

-

ARM7_Sharp_LH79520_Memory2016-03-24 1000

全部0条评论

快来发表一下你的评论吧 !