芯片面积估计的概念和方法

电子说

描述

芯片面积估计的概念

芯片面积的主要涵盖部分分为三部分

IO:芯片的信号及电源pad等

Standard cell : 实现芯片的功能逻辑

Macro block :第三方IP( PLLDAC POR Memory .etc )

芯片面积估计就是通过目标工艺的库信息,设计的spec、以往设计的信息及,部分IP的综合报告来统计这主要部分的总面积的过程。

图1,IO,Standard cell,Macro block

芯片面积估计的具体过程

获得面积信息

获得IO面积:通过目标工艺的IO库文件得到各种IO的长宽及size大小,再根据我们的设计是spec,pin_list文档中的pad选型和数量统计出。

获得Standard cell面积:可以通过单独IP的综合过进行统计,转产项目科根据原设计的全芯片综合报个得到,对与没有完整RTL的IP可以根据IP的复杂程度由设计方提供预估的等效逻辑门数,通过等效逻辑门※的数量计算面积。

※等效逻辑门:对数字设计的复杂程度一般用等效逻辑门的数量来评价,等效逻辑门一般为目标工艺下的一个标准大小(最小驱动能力)的与非门表示A(10k Gates)B(um2)=C(mm2),SMIC 110nm B=4.12。

获得Macro block面积:第三方IP提供方提供的IP文档中会有形状及面积,Memorycompiler生成的memory文档中也有memory的形状及面积

几种面积估计的方法

有了以上三种面积基本信息,就可以进行面积估算了。

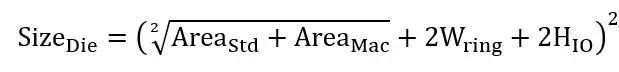

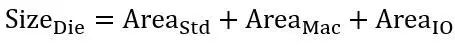

首先要对获得的Standard cell及Marco block的面积信息进行一下转换,Standard cell的转换(如果Standard cell的总面积是需要做SCAN但是未插入SCAN,需要乘以一个SCAN后的面积增量,经验值为105%)主要是由于density◎,需将Standard cell的总面积除以density值,Macro block主要是由于blockage●,需将Macro block的长宽加上两倍blockage的宽度再做乘积。

● density:由于芯片的Timing等原因,导致用于摆放Standard cell的区域不能全部被Standard cell(图2中蓝色部分)填满,Standard cell的总面积占用于摆放Standard cell的区域的百分比就是density。

图2 Standard cell,闲置区域(包含电源布线)

● blockage:第三方IP(多为模拟IP,图3中央蓝色的正方形)为了防止外围环境的电气干扰,在文档中会要求保留一定的空区域或者用电源ring环绕,这部分区域就是blockage。

图3

Pad Limit

这种情况是将芯片全部IO在四边紧密的排满,中间的面积大于转换过的Standard cell与Macro block的总和,因为四边排满IO没有办法在缩小,所以芯片的主体面积就是有IO排列决定的这块区域的面积,不需要估计由后端工程师排列好IO直接给出

2. Core Limit

这种情况是将芯片全部IO在四边紧密的排满,中间的面积小于CORE面积(转换过的Standard cell与Macro block的总和),这时CORE的面积决定了芯片面积的大小。

Core Limit的时候如果设计有在IO ring上不能摆放其他单元的要求,估算时将CORE当做正方形(因为正方形在芯片生产的时候在wafer上浪费的面积最小,也有利有芯片内部电源布线,减少IRdrop),将面积值开方的到正方形的边长加上一个宽度为固定值或者边长百分比的ring(power ring等)的宽度的两倍,再加上IO高度的两倍,再进行平方得到芯片的主体面积。

Core Limit的时候如果设计无要在IO ring上不能摆放其他单元的要求,估算是将CORE面积与IO面积相加即可。

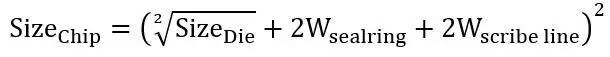

芯片生产出来的时候是许多芯片在一片wafer上的需要用划片机将芯片分割开来,这个时候就需要为分割芯片预留的空间scribe line,在分割芯片及芯片运输封装的过程中,芯片边缘的应力会产生变化,设计上需要在芯片周边做一圈钝化的区域(sealring)以保护芯片不碎裂以及屏蔽和防潮功能。

这样整个芯片的面积就是芯片主体边长(主体面积开方)加上两倍的scribe line的宽度和两倍的sealring宽度再平方。

- 相关推荐

- 热点推荐

- 芯片

-

三星3nm工艺创新采用‘GAAFET结构’ 芯片面积减少45%2019-05-17 9151

-

异步电机速度估计方法之直接计算法2023-05-05 905

-

声源定位中的时延估计方法研究2010-04-22 3829

-

请问开关管13003芯片面积的问题2014-05-08 2541

-

英飞凌以塑封料温度测量为基础的一种结温计算方法2018-12-03 3365

-

以塑封料温度测量为基础的一种结温计算方法2018-12-05 5577

-

新品# 极小的芯片面积,超强音质ANC codec ADAU1850主动降噪芯片2021-08-23 5548

-

中芯发布0.11μm超高密度IP库方案 可节省31%芯片面积2012-03-12 1487

-

无线传感网络缺失值估计方法2017-12-27 995

-

叶面积仪操作方法和效果分析2021-06-24 807

-

活体叶面积仪的应用使得测量叶片面积更加方便2021-08-02 1693

-

使用SRAM如何节省芯片面积2022-01-26 557

-

软件方法对多星座GNSS芯片设计的好处2022-06-29 1484

-

对通信信号的载波频偏进行估计的方法2022-11-30 8049

-

AMD Navi 44/48图形芯片细节揭示:RDNA 4架构,芯片面积较大2024-04-10 1889

全部0条评论

快来发表一下你的评论吧 !