设计一个1位的二选一多路选择器及其VHDL描述

电子说

描述

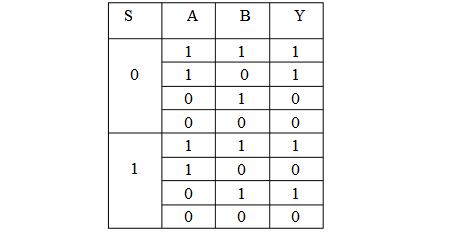

二选一多路选择器真值表

二选一多路选择器逻辑表达式为:

根据逻辑表达式所列真值表如下图所示

1位二选一多路选择器及其VHDL描述

实验步骤:

1、新建一个文件夹,打开Quartus2软件,选择FLE-》NEW菜单,在弹出的NEW对话框中选择DEVICE DESGIN FILE 页的原理图文件编辑器输入项VHDL FILE,按确定键打开VHDL 编辑器窗口;

2、在VHDL 编辑器窗口输入2选1多路选择器的VHDL 描述;

ENTITYmux21aIS

PORT(ab:IN BIT:

s:INBIT:

y :OUT BIT):END ENITY mux2 1a:

ARCHITECTURE one OF mux21a IS

BEG IN

y《=aWHEN s=‘0“ELSE b:ENDARCHITECTURE one;或者:

ENTITYmux21a IS

PORT(ab:IN BIT:

s:INBIT:

y:OUT BIT);END ENTITYmux2 1a;

ARCHITECTURE one OF mux2 1a IS

BEG IN

y《=a WHEN s=”O“ELSE b;ENDARCHITECTURE one;

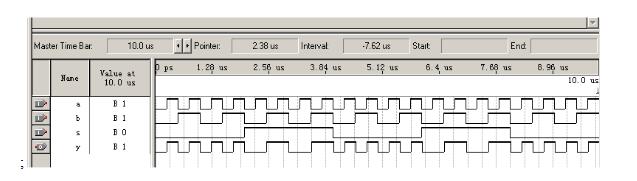

3、打开波形编辑器,分别运行2 选1多路选择器,观察他们的输出波形:

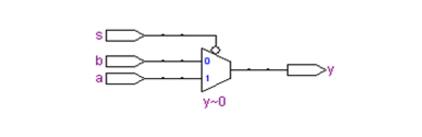

4、调出VHDL 描述产生的2 选1多路选择器的原理图。点击TOOLS-》NELIST

VIEWERS-》RTLVIEWERS,即调出VHDL描述产生的2 选1多路选择器的RIL 电路图,如下所示

实验小结:

经过本次试验初步了解了Quartus2 软件的使用,及VHDL 表达和设计电路的方法。

1位的二选一多路选择器的逻辑表达式实现

设计来源

`timescale 1ns / 1ps

//////////////////////////////////////////////////////////////////////////////////

// Company:

// Engineer:

//

// Create Date: 2018/03/17 08:26:28

// Design Name:

// Module Name: disTwo2OneSelector

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//////////////////////////////////////////////////////////////////////////////////

module disTwo2OneSelector(

input sl,

input a,

input b,

output out

);

reg out;

always @(sl or a or b)

begin

// “? :”表达式的返回值必须赋给一个变量。

out=sl?b:a;

end

endmodule

模拟源

`timescale 1ns / 1ps

//////////////////////////////////////////////////////////////////////////////////

// Company:

// Engineer:

//

// Create Date: 2018/03/17 08:45:19

// Design Name:

// Module Name: simTwo2OneSelector

// Project Name:

// Target Devices:

// Tool Versions:

// Description:

//

// Dependencies:

//

// Revision:

// Revision 0.01 - File Created

// Additional Comments:

//

//////////////////////////////////////////////////////////////////////////////////

module simTwo2OneSelector(

);

reg simA,simB,simSl;

wire simOut;

initial

begin

simSl=0;

simA=0;

simB=0;

// 在激励程序运行的瞬间,“simSl=0;simA=0;simB=0;”语句已经执行完了。

// 在0-10个时间单位,激励程序的状态保持不变。

#10

simSl=0;

simA=1;

simB=0;

#10

simSl=1;

simA=0;

simB=0;

#10

simSl=1;

simA=0;

simB=1;

end

// 设计文件模块名 对象名 (。设计文件模块中的类中的参数(激励文件模块中的类中的参数))

disTwo2OneSelector objTwo2OneSelector(.a(simA),.b(simB),.sl(simSl),.out(simOut));

endmodule

-

教你学Vivado—以2选1多路选择器为例2023-10-02 5342

-

基于FPGA的多路选择器设计(附代码)2023-03-01 2203

-

使用case语句设计实现自定义数据位宽的4选1数据选择器2022-07-04 6754

-

4选1多路选择器是什么?2022-02-09 1095

-

EDA四选一多路选择器的设计资料下载2021-04-20 1631

-

EDA四选一多路选择器的设计2021-04-12 6931

-

【梦翼师兄今日分享】 二选一数据选择器的设计2019-12-13 5050

-

8选1多路选择器电路图(五款8选1多路选择器电路)2018-04-28 143536

-

多路选择器有哪些_多路选择器分类介绍2018-04-27 38328

-

VHDL例程4选1选择器2016-11-10 942

-

至芯科技之altera 系列FPGA教程 第九篇 二选一多路选择器的设计2016-08-11 3533

-

八选一多路选择器Verilog代码及仿真结果MUX_82016-03-28 6382

全部0条评论

快来发表一下你的评论吧 !