什么是时钟频率_时钟频率详解和编程

编程实验

描述

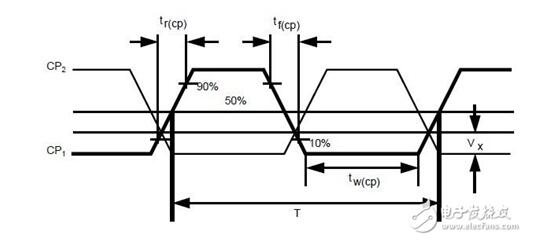

在电子技术中,脉冲信号是一个按一定电压幅度,一定时间间隔连续发出的脉冲信号。脉冲信号之间的时间间隔称为周期;而将在单位时间(如1秒)内所产生的脉冲个数称为频率。频率是描述周期性循环信号(包括脉冲信号)在单位时间内所出现的脉冲数量多少的计量名称;频率的标准计量单位是Hz(赫)。本文主要介绍什么是时钟频率及编程,具体的跟随小编一起来了解一下。

什么是时钟频率

时钟频率即CPU的外部时钟频率,由电脑主板提供,以前一般是66MHz,也有主板支持75各83MHz,目前Intel公司最新的芯片组BX以使用100MHz的时钟频率。另外VIA公司的MVP3、MVP4等一些非Intel的芯片组也开始支持100MHz的外频。精英公司的BX主板甚至可以支持133MHz的外频,这对于超频者来是首选的。

时钟频率就像发动机转速,以一定频率在转,但能跑多块还要具体分析

频率越高,对信号质量要求越高,能耗越大,与同样产品相比,高频率=高性能不是一辆卡车变两辆卡车……虽然还是那个速度,但装的多

木桶能装多少水取决于最短那块板,在电脑上有一定道理没有绝对的好,坏,成本决定性能,同样的成本可以有不同的侧重点,加强某方面的性能,但其他方面相应减弱

时钟频率详解和编程

晶振:其作用是产生原始的时钟频率,这个频率经过频率发生器的倍频或分频后就成了电脑中各种不同的总线频率;其本身不振荡但和外电路产生谐振。

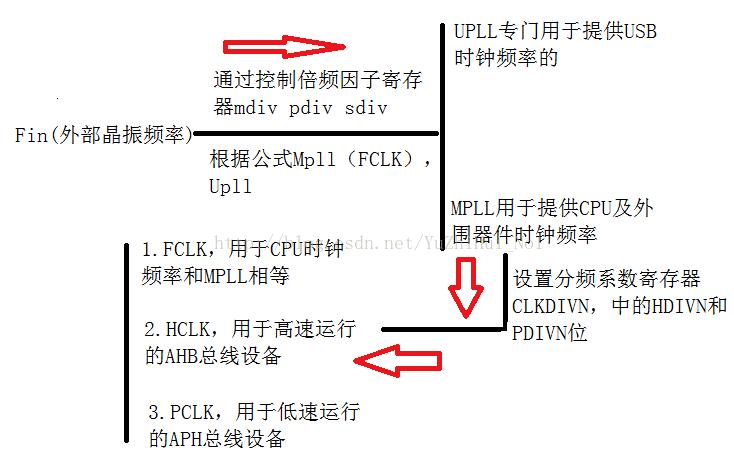

一般来讲系统都会有2个锁相环。这里就拿三星的S3C2440来作为例子吧。S3C2440有2个锁相环(PLL--- phase locked loop),一个是MPLL,一个是UPLL;MPLL用于CPU及其他外围器件。UPLL用于USB提供48MHz.外部时钟源,经过MPLL处理后能够得到三种不同的系统时钟。他们分别是FCLK,HCLK,PCLK三种频率,这三种频率分别有不同的用途。

FCLK是为CPU提供时钟信号,主频时钟,用于ART920T内核。

HCLK是为AHB总线提供的时钟信号,主要用于高速外设,比如内存控制器,中断控制器,LCD控制器,DMA以及USB主模块等。

PCLK是为APB总线提供的时钟信号,主要用于低速外设,比如看门狗,UART控制器,IIS,I2C,SDI/MMC,GPIO,RTC and SPI。

当系统上电或者复位时后,MPLL就可以工作,但此时MPLL的值并不是系统时钟,因为此时MPLL寄存器还没初始化,还是个无效的值,所以系统选择外部时钟晶振作为系统时钟。因此系统上电及复位后,必须向MPLL寄存器写入一个值,尽管这个值可能就是寄存器中的旧值。

LOCKTIME寄存器:用于设置MPLL启动后稳定前所需等待的时间(Lock time),一般使用默认值。

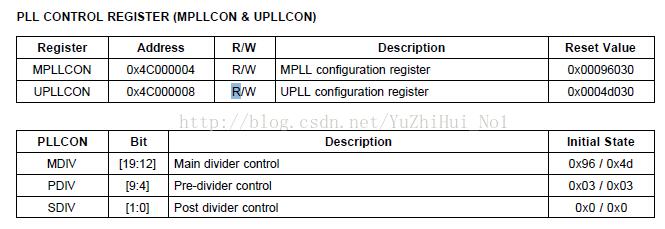

MPLLCON/UPLLCON寄存器设置:MDIV 主频控制位,PDIV 预分频控制位,SDIV 后分频控制位

Mpll(FCLK) = (2 * m * Fin)/(p*2s)

Upll = (m * Fin)/(p*2s)

其中:m = (MDIV+8), p = (PDIV+2), s = SDIV

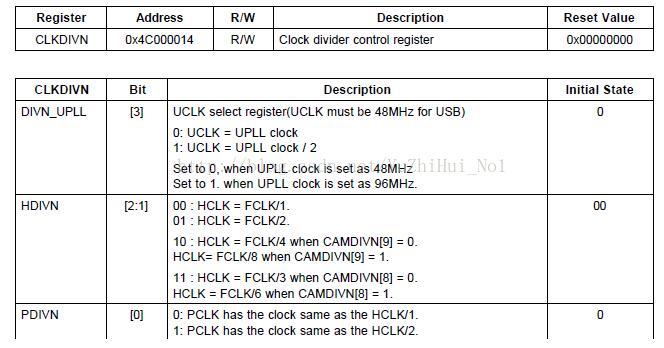

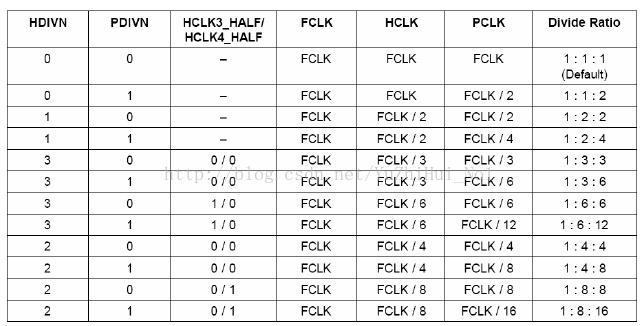

FCLK、PCLK、HCLK 这三个系统时钟具有一地定的比例关系,这种关系是通过寄存器CLKDIVN中的HDIVN位和PDIVN位来控制的,因此我们知道了FCLK,再通过这2位的控制就能确定HCLK,PCLK.而FCLK则是通过外部晶振频率Fin由上面公式可以得到。

说了这么多,还是来理理顺序:

下面的例子网上好多,先贴出来,然后再分析其本质是什么。

mpll_val = (92《《12)|(1《《4)|(1);//至于为什么mpll_val这个值是(92《《12)|(1《《4)|(1),没有找到说明,个人分析有可能是大家的经验,或者是从后面逆推计算出来的。在Fin为12MHz情况下,要让主频达到400MHz,可以从后面开始逆推出来。

定义mpll_val这个值实际是为了让倍频因子控制寄存器设定下面的值:

MDIV=92 PDIV=1 SDIV=1

ChangeMPllValue((mpll_val》》12)&0xff, (mpll_val》》4)&0x3f, mpll_val&3);

函数原型:

void ChangeMPllValue(int mdiv,int pdiv,int sdiv)

{

rMPLLCON = (mdiv《《12) | (pdiv《《4) | sdiv;

}

函数功能:输入参数设定MPLLCON寄存器的值,即倍频因子寄存器的值。

再根据公式:

Mpll(FCLK) = (2 * m * Fin)/(p*2s),m = MDIV + 8 =100;Fin 外部晶振频率为12MHz,p = PDIV+2 = 3,S = SDIV =1;

所以得到:FCLK = Mpll = 400MHz

得到了FCLK,要计算出PCLK和HCLK就比较容易了。设置下分频系数寄存器CLKDIVN中的HDIVN位和PDIVN位就可以了。下面是常用的分频系统。

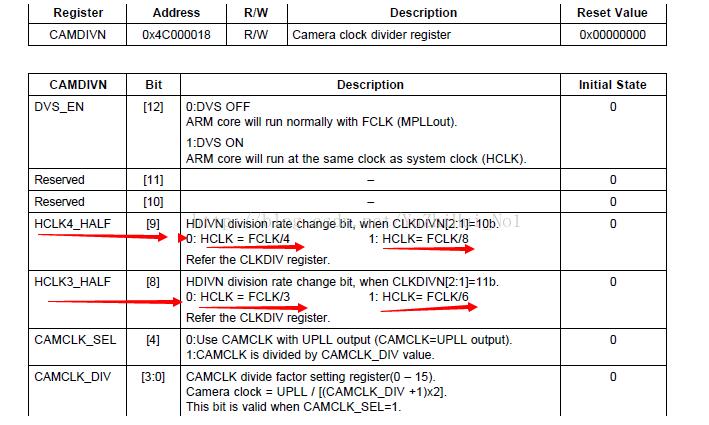

其实分频系数寄存器中HDIVN位要设置为10或者11时,还要设置下CAMDIVN寄存器:

最后,再补上一个总结的图上去。

- 相关推荐

- 热点推荐

- 时钟频率

-

dds输出频率与时钟的关系2024-10-06 3229

-

2023年 新品发布总结 频率控制和时钟器件Part2jf_05851568 2024-01-24

-

时钟和频率合成的应用领域2023-11-27 426

-

为什么需要debug时钟频率 Debug时钟频率原理详解2023-09-20 1482

-

如何改变spi的时钟频率?2023-06-03 5021

-

如何修改时钟频率2022-02-08 4010

-

时钟频率和晶振频率的区别2022-01-29 12053

-

51/时钟周期、时钟频率、状态周期、机器周期2021-11-20 1241

-

PLL设计和时钟频率产生2021-06-07 1011

-

cpu时钟频率的单位是什么2020-05-14 12463

-

cpu时钟频率计算公式_CPU频率计算方法详解2018-04-28 35232

-

基于SERDES时钟的频率跟随的设计2017-11-18 8063

-

时钟频率是什么意思2017-11-10 25720

-

分析引起较高时钟频率仿真失败的原因2017-01-04 3103

全部0条评论

快来发表一下你的评论吧 !