74ls75引脚图及功能表介绍

芯片引脚图

730人已加入

描述

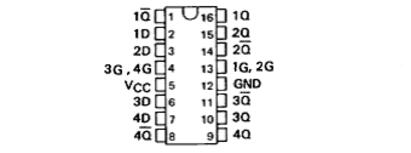

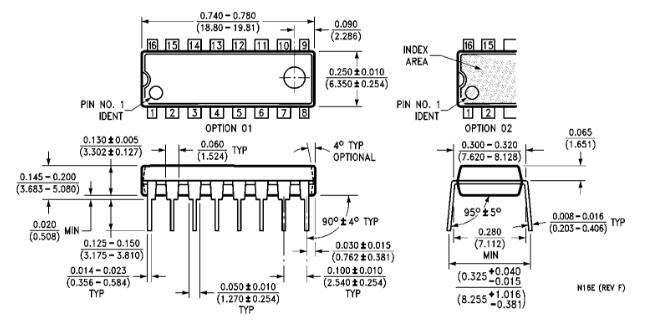

74ls75引脚图

16引脚4路透明D锁存器。当控制端G为高电平时,Q输出跟随D变化。当控制端为低电平时,Q保持原值。 通常用在数据在时钟沿未准备好时来暂存数据。

74ls75功能表

H=高电平L=低电平×=不定

Q0=使能G由高电平转换到

低电平之前Q的电平

说明:这种锁存器最适合作运算单元和输入/输出(或指示)单元之间二进制数据的暂时储存之用。当使能G是高电平时,数据D输入上的信息便传送至Q输出;只要使能保持高,Q输出便随数据输入而变。当使能变为低电平时,跳变时数据输入端的信息将保持在Q输出上,直至使能变成高电平为止。

74ls75推荐工作条件

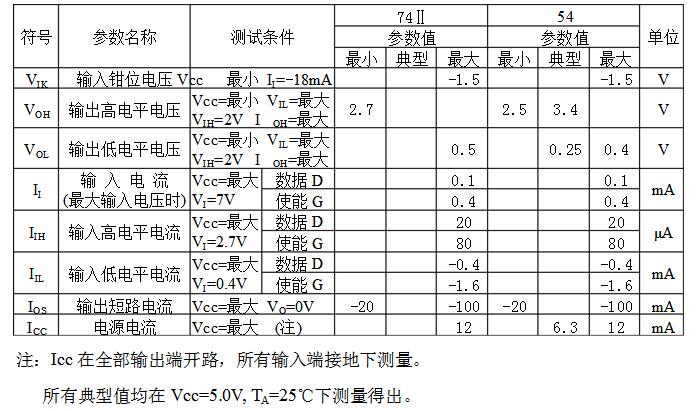

74ls75电气性能

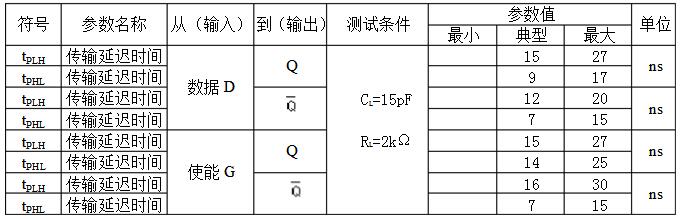

74ls75交流(开关参数)

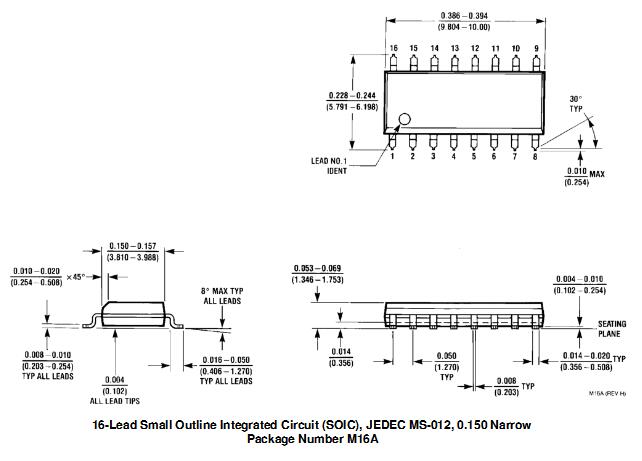

74ls75封装

声明:本文内容及配图由入驻作者撰写或者入驻合作网站授权转载。文章观点仅代表作者本人,不代表电子发烧友网立场。文章及其配图仅供工程师学习之用,如有内容侵权或者其他违规问题,请联系本站处理。

举报投诉

- 相关推荐

- 热点推荐

- 74LS75

-

74ls160引脚图及功能真值表介绍2022-05-25 178630

-

74ls163引脚图及功能表2021-07-08 97767

-

74ls109引脚图及功能详解2018-05-29 28895

-

74ls123引脚图及功能_功能表及内部结构2018-05-28 54134

-

74ls152中文资料_74ls152引脚图_功能表_逻辑图_特性参数2018-05-07 25456

-

74ls125中文资料(74ls125引脚图及功能_真值表)2018-05-04 111762

-

74ls09引脚图及功能表_真值表和特性参数2018-04-09 33635

-

74ls194引脚图及功能_74ls194功能表_74ls194应用电路2017-12-22 383341

-

十进制可逆计数器74LS192引脚图管脚及功能表2011-05-19 132365

-

74ls92引脚图及功能表2008-12-01 26136

-

74ls190引脚图管脚图及功能表2008-08-06 117289

-

74ls04引脚图 引脚功能2007-11-29 76546

全部0条评论

快来发表一下你的评论吧 !