直接数字频率合成知识点汇总(原理_组成_优缺点_实现)

模拟技术

描述

直接数字频率合概述

DDS同DSP(数字信号处理)一样,也是一项关键的数字化技术。DDS是直接数字式频率合成器(Direct Digital Synthesizer)的英文缩写。DDS是从相位概念出发直接合成所需要波形的一种新的频率合成技术。

直接数字频率合成是一种新的频率合成技术和信号产生的方法,具有超高速的频率转换时间、极高的频率分辨率分辨率和较低的相位噪声,在频率改变与调频时,DDS能够保持相位的连续,因此很容易实现频率、相位和幅度调制。此外,DDS技术大部分是基于数字电路技术的,具有可编程控制的突出优点。因此,这种信号产生技术得到了越来越广泛的应用,很多厂家已经生产出了DDS专用芯片,这种器件成为当今电子系统及设各中频率源的首选器件。

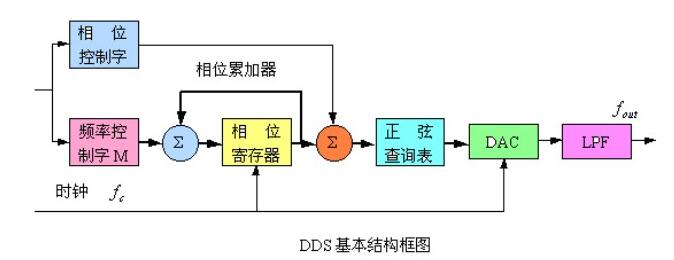

直接数字频率合成原理

工作过程为:

1、将存于数表中的数字波形,经数模转换器D/A,形成模拟量波形。

2、两种方法可以改变输出信号的频率:

(1)改变查表寻址的时钟CLOCK的频率,可以改变输出波形的频率。

(2)、改变寻址的步长来改变输出信号的频率.DDS即采用此法。步长即为对数字波形查表的相位增量。由累加器对相位增量进行累加,累加器的值作为查表地址。

3、D/A输出的阶梯形波形,经低通(带通)滤波,成为质量符合需要的模拟波形。

直接数字频率合成系统的构成

直接数字频率合成主要由标准参考频率源、相位累加器、波形存储器、数/模转换器、低通平滑滤波器等构成。其中,参考频率源一般是一个高稳定度的晶体振荡器,其输出信号用于DDS中各部件同步工作。DDS的实质是对相位进行可控等间隔的采样。

直接数字频率合成优缺点

优点:

(1)输出频率相对带宽较宽

输出频率带宽为50%fs(理论值)。但考虑到低通滤波器的特性和设计难度以及对输出信号杂散的 抑制,实际的输出频率带宽仍能达到40%fs。

(2)频率转换时间短

DDS是一个开环系统,无任何反馈环节,这种结构使得DDS的频率转换时间极短。事实上,在 DDS的频率控制字改变之后,需经过一个时钟周期之后按照新的相位增量累加,才能实现频率的转 换。因此,频率时间等于频率控制字的传输,也就是一个时钟周期的时间。时钟频率越高,转换时 间越短。DDS的频率转换时间可达纳秒数量级,比使用其它的频率合成方法都要短数个数量级。

(3)频率分辨率极高

若时钟fs的频率不变,DDS的频率分辨率就是则相位累加器的位数N决定。只要增加相位累加器的 位数N即可获得任意小的频率分辨率。目前,大多数DDS的分辨率在1Hz数量级,许多小于1mHz甚 至更小。

(4)相位变化连续

改变DDS输出频率,实际上改变的每一个时钟周期的相位增量,相位函数的曲线是连续的,只是在 改变频率的瞬间其频率发生了突变,因而保持了信号相位的连续性。

(5)输出波形的灵活性

只要在DDS内部加上相应控制如调频控制FM、调相控制PM和调幅控制AM,即可以方便灵活地实 现调频、调相和调幅功能,产生FSK、PSK、ASK和MSK等信号。另外,只要在DDS的波形存储器 存放不同波形数据,就可以实现各种波形输出,如三角波、锯齿波和矩形波甚至是任意的波形。当 DDS的波形存储器分别存放正弦和余弦函数表时,既可得到正交的两路输出。

(6)其他优点

由于DDS中几乎所有部件都属于数字电路,易于集成,功耗低、 体积小、重量轻、可靠性高,且易于程控,使用相当灵活,因此性价 比极高。

缺点:

DDS也有局限性,主要表现在:

(1)输出频带范围有限

由于DDS内部DAC和波形存储器(ROM)的工作速度限 制,使得DDS输出的最高频有限。目前市场上采用CMOS、 TTL、ECL工艺制作的DDS工习片,工作频率一般在几十 MHz至400MHz左右。采用GaAs工艺的DDS芯片工作频 率可达2GHz左右。

(2)输出杂散大

由于DDS采用全数字结构,不可避免地引入了杂散。其来 源主要有三个:相位累加器相位舍位误差造成的杂散;幅 度量化误差(由存储器有限字长引起)造成的杂散和DAC 非理想特性造成的杂散。

直接数字式频率合成器基本技术实现方案

(1)采用高性能的DDS单片电路解决方案

随着DDS技术和VLSI的发展,DDS单片化在九十年代就已经完成。由于DDS芯片性能日渐完善,促成了许多DDS芯片生产厂家出现,它们推出了许多性能优越的DDS芯片,为电路设计者提供了多种选择。其中AD公司的DDS系列产品性价比较高,目前取得了极为广泛的应用。

(2)自行设计基于可编程器件的解决方案

由于可编程逻辑器件的规模大、速度快、可编程,以及有强大的EDA软件支持等特性,十分适合实现DDS系统的数字部分。在高可靠性的应用领域,如果设计合理得当,将不会存在类似MCU的复位不可靠等问题。而且由于它的高度集成,完全可以将整个系统下载到同一个芯片当中,实现所谓的片上系统,从而大大缩小产品的体积,提高了系统的可靠性。

(3)基于FPGA的DDS系统合成方案

通过FPGA控制DDS产生线性调频信号及跳频信号。基于FPGA的DDS系统技术可以产生多种调制方式以及多种组合方式,并且可以实现多个DDS芯片的功能,更加集成。

事实上,除了这三种基础合成方案外,还可考虑这三种方案的优势组合,形成新的方案。

直接数字频率合成系统实现

1、DSP及DDS芯片介绍

本次设计采用DSP控制DDS实现频率合成器。使用TI公司生产的DSP处理器TMS320VC5402和ADI公司生产的DDS芯片AD9835,下面分别对这两个芯片做简单介绍。

数字信号处理器(DSP)是在模拟信号变换成数字信号以后进行高速实时处理的专用处理器,其处理速度比最快的通用CPU还快1O一50倍。在当今的数字化时代,DSP己成为通信、计算机、消费类电子产品等领域的基础器件,被称为信息社会革命的旗手。

VC5402是TI公司1999年10月推出性价比较高的定点数字信号处理器,VC5402具有先进的改进型哈佛结构,操作速率可达100MIPS;多总线结构。VC5402的存储器的配置比较灵活,主要由模式寄存器PMST里的OVLY、DROM和MP/MC位进行配置。其中,OVLY和DROM上电复位均为0,而MP/MC决定配置DSP为微处理器/微机模式。上电后采样MP/MC引脚信号,保存在MP/MC位,可以在DSP运行中由软件配置该位。

AD9835是AD公司生产的一款CMOS工艺完备的DDS芯片,5V供电。它的最高时钟频率可达50MHZ。AD9835主要由数控振荡器(NCO)和相位调制器、正弦查询表以及一个10位数模转换器(DAC)组成。其中数控振荡器和相位调制器部分包含两个32位的频率寄存器、一个32位的相位累加器和四个12位的相位寄存器。

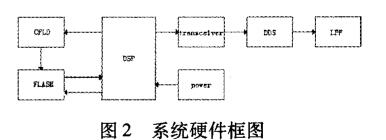

2、系统硬件实现

系统硬件框图如图2所示:

选用的FLASH存储器为AM29LV160D。由DSP芯片通过CPLD对FLASH进行逻辑控制。这样可以使系统的存储器配置更加灵活。由于外扩了FLASH,DSP要对FLASH进行正常读写的逻辑时序控制就由CPLD来实现,由于CPLD可在线编程,使得日后系统的逻辑的修改也非常方便,这比用传统的组合逻辑电路设计要灵活方便,只需要的是将DSP对FLASH读写时序分析清楚。在此采用的是Altera公司的EPM7064S来完成以上功能。

电源芯片采用rI’I公司生产的TPS767D318,该芯片是双电源输出,每个电源输出都有单独的复位和输出使能控制。它采用TSSOP封装,固定两路电压输出,第一路输出1.8V,第二路输出电压为3.3V。该芯片同时还提供)两路复位信号,该系统中只使用了第二路复位信号,芯片的22引脚输出低电平复位信号,复位后需为高电平,上拉为3.3V。

数字解调实验时采用的信号是已调模拟信号,模拟信号不能直接送人DSP中,要先由模数转换器(AD)转换为数字信号后,再送入DSP中进行数字解调和基带处理。模数转换器选用了AD公司的AD转换芯片AD7822。AD7822是20脚的8位模数转换芯片,最大采样率可以达到2MSPS。AI)7822以并行的方式和DSP相连。数模转换(DA)模块的功能就是完成数字信号的模拟化,在进行数字调制实验时通过DA模块把DSP输出的已调数字信号转换为模拟信号,可以为解调实验提供一个已调的模拟信号,也可以通过示波器观测调制信号波形。该模块选用了AD公司的芯片AD7303。

- 相关推荐

- 热点推荐

- DDS

-

直接数字频率合成信号发生器的设计2023-10-30 615

-

直接数字频率合成技术(DDS+PLL)2021-06-07 1148

-

直接数字频率合成有什么优缺点?2020-03-16 3577

-

直接数字频率合成技术的频率研究2019-07-10 5142

-

基于单片机的直接数字频率合成详解2018-04-28 4192

-

利用单片机和CPLD实现直接数字频率合成2016-05-04 501

-

直接数字频率合成技术DDS原理2015-10-30 1105

-

FPGA实现直接数字频率合成(DDS)的原理、电路结构和优化...2012-08-11 10200

-

直接数字频率合成器的实现设计方案2012-03-30 3378

-

基于FPGA的直接数字频率合成器的设计2010-08-09 556

-

基于SystemView的数字频率合成器的设计2010-07-09 2749

-

基于FPGA的直接数字频率合成器的设计和实现2009-05-16 1306

-

FPGA实现的直接数字频率合成器2009-05-11 1219

-

直接数字频率合成器设计方法2008-03-25 1347

全部0条评论

快来发表一下你的评论吧 !