ADuM4120/ADuM4120-1具有2A输出的隔离式精密栅极驱动器技术手册

描述

概述

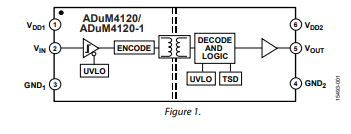

The ADuM4120/[ADuM4120-1 系列]是 2 A 隔离式单通道驱动器,采用 Analog Devices, Inc. 的 i耦合器®技术来提供精密隔离。The ADuM4120/ADuM4120-1 在 6 引脚宽体 SOIC 封装中提供 5 kV rms 隔离,爬电距离增加。这些隔离元件结合了高速 CMOS 和单片变压器技术,具有出色的性能特征,例如脉冲变压器和栅极驱动器的组合。

ADuM4120/ADuM4120-1 采用 2.5 V 至 6.5 V 的输入电源供电,兼容更低的 电压系统。与采用高压电平转换方法的栅极驱动器相比,ADuM4120/ ADuM4120-1 具有真正的电流隔离优势 输入和输出。

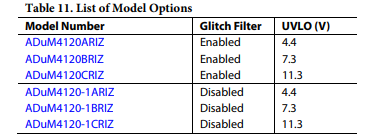

对于带和不带 input glitch filter 的模型,存在选项。毛刺滤波器有助于减少输入引脚上出现噪声的可能性 触发 output。

因此,ADuM4120/ADuM4120-1 可对绝缘栅极的开关特性进行可靠控制 双极晶体管 (IGBT)/金属氧化物半导体场效应晶体管 (MOSFET) 配置,适用于较宽的开关电压范围。

数据表:*附件:ADuM4120 ADuM4120-1具有2A输出的隔离式精密栅极驱动器技术手册.pdf

应用

- 开关电源

- IGBT/MOSFET 栅极驱动器

- 工业逆变器

- 氮化镓 (GaN)/碳化硅 (SiC) 功率器件

特性

- 2.3 A 峰值输出电流 (<2 Ω RDSON_x)

- 2.5 V 至 6.5 V

DD1输入 - 4.5V 至 35 V

DD2输出 - 2.3 V

DD1时的 UVLO - VDD2 上的多个 UVLO 选项

- A 级 — 4.4 V(典型值)正向阈值

- B 级 — 7.3 V(典型值)正向阈值

- C 级 — 11.3 V(典型值)正向阈值

- 精确的定时特性

- 最大隔离器和驱动器传播延迟下降沿 (ADuM4120)

- CMOS 输入逻辑电平

- 高共模瞬态抗扰度:150 kV/μs

- 高结温工作:125°C

- 默认低输出

- 安全和监管批准(待定)

- 根据 UL 1577 的 UL 认证

- 5 kV rms,用于 1 分钟 SOIC 长封装

- CSA 组件验收通知 5A

- VDE 合格证书(待定)

- DIN V VDE V 0884-10 (VDE V 0884-10):2006-12

- V

IORM= 849 V 峰值

- 根据 UL 1577 的 UL 认证

- 爬电距离 8 mm

- 宽体 6 引脚 SOIC,爬电距离增加

功能框图

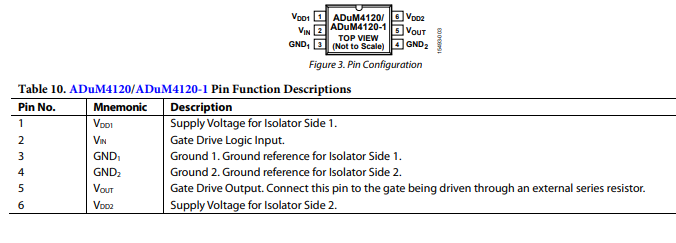

引脚配置描述

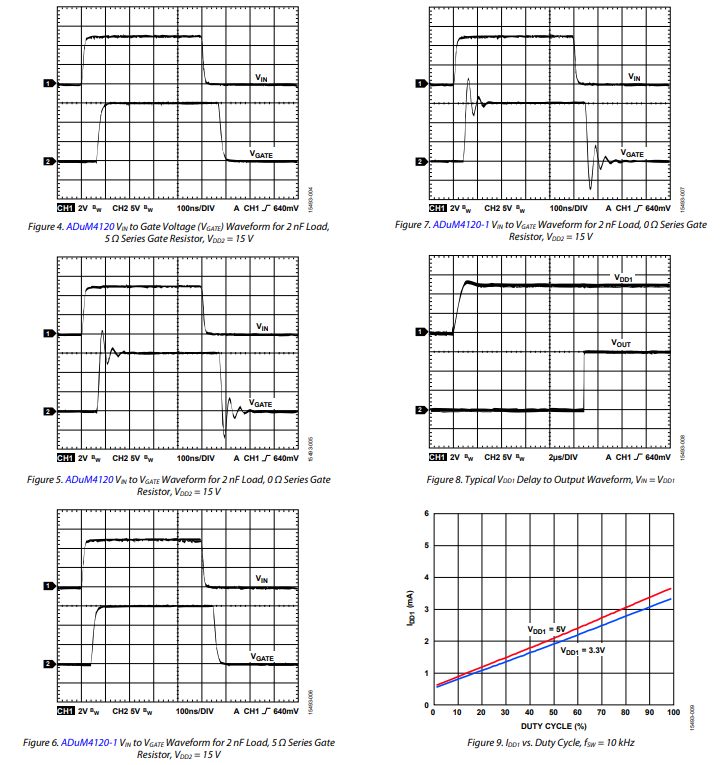

典型性能特征

工作原理

在期望开关器件栅极具有快速上升沿的情况下,需要使用栅极驱动器。对于大多数增强型功率器件而言,栅极信号需参考源极或发射极节点。由于驱动电路的控制信号与栅极驱动器的输出之间必须实现隔离,所以源极或发射极节点会在半桥等拓扑结构中摆动。开关时间取决于驱动强度。缓冲级是一种互补金属氧化物半导体(CMOS)推挽结构,可减少总延迟时间并增加驱动器的最终驱动强度。

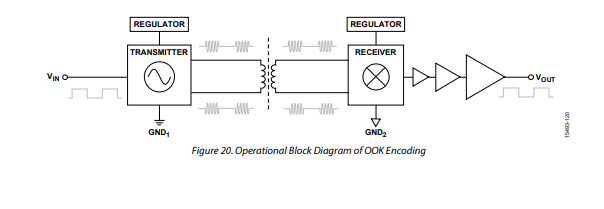

ADuM4120/ADuM4120 - 1 通过高频耦合器实现控制侧与栅极驱动器输出侧之间的隔离,该耦合器通过聚酰亚胺绝缘层分隔的芯片级变压器线圈传输数据。ADuM4120/ADuM4120 - 1 使用的编码方案是正逻辑开关键控(OOK),即高电平信号通过载波频率的存在来传输,该载波频率是芯片级变压器线圈的 iCoupler 频率。正逻辑编码确保在栅极驱动器未通电时,输出为低电平信号。在可能出现直通情况的结构中,低电平状态会驱动大多数安全增强模式电源器件。该架构旨在实现高共模瞬变抗扰度,以及对电噪声和磁干扰的高抗扰度。辐射发射通过扩频 OOK 载波和差分线圈布局等其他技术得以降低。图 20 展示了 ADuM4120/ADuM4120 - 1 使用的编码方式。

应用信息

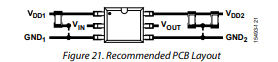

印刷电路板(PCB)布局

ADuM4120/ADuM4120 - 1 数字隔离器无需外部接口电路用于逻辑接口。需要进行电源旁路,如图 21 所示,在输入和输出电源引脚处使用 0.01 μF 至 0.1 μF 的小陶瓷电容,以实现高效旁路。在输出电源引脚 VISO2 上,建议额外添加一个 10 μF 的电容,为 ADuM4120/ADuM4120 - 1 驱动栅极提供所需的电容。避免在输出电源引脚和旁路电容之间使用过孔,或使过孔数量尽量少,以减少旁路时的电感。较小电容两端与输入或输出电源引脚之间的总引脚长度不得超过 20 毫米。

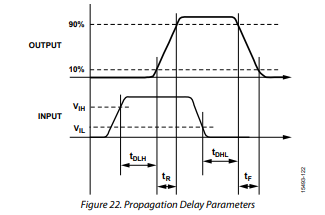

传播延迟相关参数

传播延迟是描述逻辑信号从器件输入传播到逻辑低输出所需时间的参数。传播延迟可能因器件而异。ADuM4120/ADuM4120 - 1 的传播延迟如图 22 所示。上升时间定义为输出从 VIH 上升到 10% 阈值的时间。同样,下降时间 tFALL 定义为输出从输入下降逻辑低电压阈值 VIL 下降到 90% 阈值的时间。上升和下降时间取决于负载条件,且通常不包含在传播延迟中,因为它们并非栅极驱动器的标准特性。

通道间匹配是指单个 ADuM4120/ADuM4120 - 1 器件内各通道之间传播延迟的最大差异量。

传播延迟偏差是指多个在相同条件下工作的 ADuM4120/ADuM4120 - 1 器件之间传播延迟的最大差异量。

热限制和开关负载特性

对于隔离式栅极驱动器,输入和输出电路之间需保持必要间距,防止单个热焊盘下的热量通过器件引脚传导出去。

如果器件的内部结温(θJA)超过 TSD 阈值,输出将被驱动为低电平以保护器件。高于推荐工作范围的工作条件无法保证表 1 中所示的规格。

欠压锁定(UVLO)

ADuM4120/ADuM4120 - 1 对器件的初级侧和次级侧均设有欠压锁定保护。如果初级侧或次级侧电压低于欠压锁定下降沿阈值,器件输出将为低电平信号。在 ADuM4120/ADuM4120 - 1 上电后,上升沿欠压锁定阈值使器件能够输出找到输入信号。该器件内置迟滞特性,可抵御小电压源纹波。初级侧欠压锁定阈值在所有型号中通用。次级侧阈值选项列于表 11 中。

-

深度剖析ADuM4120 - 1 隔离式精密栅极驱动器2026-02-04 856

-

ADuM3123隔离式精密栅极驱动器:特性、应用与设计要点2026-02-03 1203

-

ADUM3123隔离式精密栅极驱动器,4A输出技术手册2025-06-04 1443

-

ADuM4121/ADuM4121-1集成内部米勒箝位的高压、隔离式栅极驱动器,具有热关断功能的2A输出技术手册2025-06-03 1414

-

ADuM4120ADuM4120-1 IBIS型号2021-06-02 854

-

UG-1109:2 A输出的ADuM4120和ADuM4120-1隔离式精密栅极驱动器评估板2021-05-16 1161

-

ADuM3123:隔离式精密栅极驱动器,4.0A输出数据表2021-04-24 1070

-

ADuM4120/ADuM4120-1 IBIS模型2021-04-09 853

-

ADuM4221/ADuM4221-1/ADuM4221-2:隔离式半桥栅极驱动器,死区时间可调,4 A输出数据表2021-03-22 1283

-

ADuM4120/ADuM4120-1 IBIS Model2021-02-19 988

-

支持ADuM3123ARZ隔离式精密栅极驱动器2019-05-23 1245

-

支持ADuM3123CRZ隔离式精密栅极驱动器的EVAL-ADUM3123EBZ2019-05-06 1891

-

ADUM4120-1 输出为 2 A 的隔离式高精度栅极驱动器2019-02-22 265

全部0条评论

快来发表一下你的评论吧 !