ADuM4121/ADuM4121-1集成内部米勒箝位的高压、隔离式栅极驱动器,具有热关断功能的2A输出技术手册

描述

概述

ADuM4121/ADuM4121-1为2 A隔离式、单通道驱动器,采用ADI公司的iCoupler®技术提供精密隔离。ADuM4121/ADuM4121-1提供5 kV rms隔离,采用8引脚宽体SOIC封装。这些隔离器件将高速CMOS与单芯片变压器技术融为一体,具有优于脉冲变压器和栅极驱动器组合等替代器件的出色性能特征。

ADuM4121/ADuM4121-1采用2.5 V至6.5 V输入电压工作,可与较低电压系统兼容。与采用高压电平转换方法的栅极驱动器相比,ADuM4121/ADuM4121-1的输入与输出之间具有真电气隔离优势。

ADuM4121/ADuM4121-1集成内部米勒箝位,在2 V时可在栅极驱动输出的下降沿上激活,提供具有较低阻抗路径的驱动栅极,以减少米勒电容感应导通的可能性。

有很多选项可用于热关断使能或禁用。因此,ADuM4121/ADuM4121-1可在各种开关电压范围内对绝缘栅极双极性晶体管(IGBT)/金属氧化物半导体场效应晶体管(MOSFET)配置的开关特性进行可靠控制。

数据表:*附件:ADuM4121 ADuM4121-1集成内部米勒箝位的高压、隔离式栅极驱动器,具有热关断功能的2A输出技术手册.pdf

应用

- 开关电源

- 隔离式IGBT/MOSFET栅极驱动器

- 工业逆变器

- 氮化镓(GaN)/碳化硅(SiC)功率器件

特性

- 峰值输出电流:2 A (<2 Ω R

DSON) - 2.5 V至6.5 V输入

- 4.5 V至35 V输出

- 欠压闭锁(UVLO):2.5 V V

DD1 - V

DD2上提供多个UVLO选项- A级:V

DD2上的UVLO:4.4 V(典型值) - B级:V

DD2上的UVLO:7.3 V(典型值) - C级:V

DD2上的UVLO:11.3 V(典型值)

- A级:V

- 精密时序特性

- 隔离器和驱动器传播延迟:53 ns(最大值)

- CMOS输入逻辑电平

- 工作结温最高可达:125°C

- 高共模瞬变抗扰度:>150 kV/µs

- 默认低电平输出

- 内部米勒箝位

- 安全和法规认证(申请中)

- UL认证符合UL 1577

- 1分钟5 kV rms,SOIC长封装

- CSA元件验收通知5A

- 符合VDE标准证书(申请中)

- DIN V VDE V 0884-10 (VDE V 0884-10):2006-12

- V

IORM= 849 V峰值 - 8引脚宽体SOIC封装

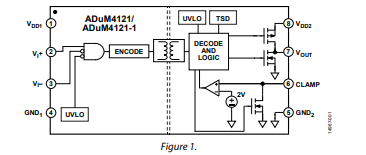

框图

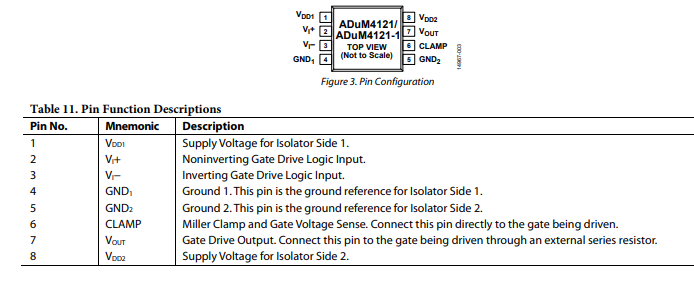

引脚配置描述

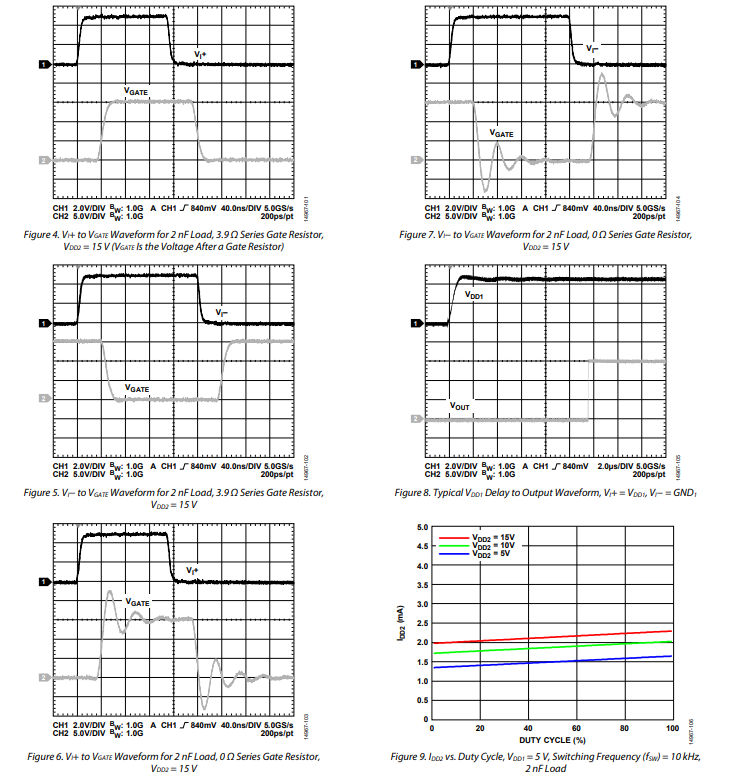

典型性能特征

工作原理

在期望开关器件的栅极具备快速上升沿的情况下,需要用到栅极驱动器。对于大多数增强型功率器件,其栅极信号需参考源极或发射极节点。由于驱动电路的控制信号与栅极驱动器的输出之间必须实现隔离,所以在半桥等拓扑结构中,源极或发射极节点会出现摆动。开关时间取决于驱动强度。缓冲级采用互补金属氧化物半导体(CMOS)推挽结构,可减少总延迟时间,并增强驱动器的最终驱动强度。

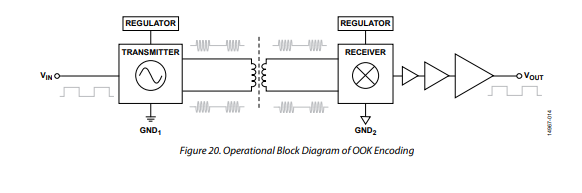

ADuM4121/ADuM4121 - 1 通过高频耦合器实现控制侧与栅极驱动器输出侧之间的隔离,该耦合器借助由聚酰亚胺绝缘层分隔的芯片级变压器线圈来传输数据。ADuM4121/ADuM4121 - 1 采用的编码方案是正逻辑开关键控(OOK),即高电平信号通过载波频率的存在来传输,该载波频率为芯片级变压器线圈的 iCoupler 频率。正逻辑编码确保当栅极驱动器的输入侧未通电时,输出为低电平信号。低电平状态会驱动大多数安全增强模式电源器件,适用于可能出现直通情况的电路结构。该架构旨在实现高共模瞬变抗扰度,以及对电噪声和磁干扰的高抗扰性。辐射发射通过扩频 OOK 载波以及差分线圈布局等其他技术得以降低。图 20 展示了 ADuM4121/ADuM4121 - 1 采用的编码方式。

应用信息

印刷电路板(PCB)布局

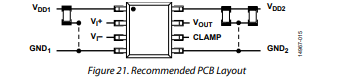

ADuM4121/ADuM4121 - 1数字隔离器无需用于逻辑接口的外部接口电路。需要进行电源旁路,如图21所示,在输入和输出电源引脚处使用0.01 μF至0.1 μF的小陶瓷电容进行高效旁路。在输出电源引脚VISO2上,建议额外添加一个10 μF的电容,为ADuM4121/ADuM4121 - 1驱动输出提供所需的电荷。在输出电源引脚处,应避免使用过孔,或使用多个过孔来降低旁路时的电感。较小电容两端与输入或输出电源引脚之间的总引脚长度不得超过20毫米。

V+和V - 工作原理

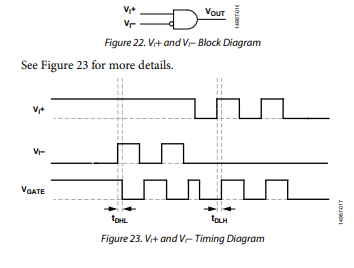

ADuM4121/ADuM4121 - 1有两个驱动输入V+和V - ,用于控制IGBT栅极驱动输入VGOUT 。V+和V - 引脚均接受CMOS电平信号。通过将V+引脚置高或V - 引脚置低来控制输入逻辑。当V - 引脚为低电平时,V+引脚接受正逻辑。如果V+保持高电平,V - 引脚接受负逻辑。更多详细信息见图23。

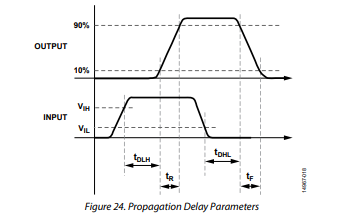

传播延迟相关参数

传播延迟是描述逻辑信号通过一个元件所需时间的参数。到逻辑0输出的传播延迟可能与到逻辑1输出的传播延迟不同。ADuM4121/ADuM4121 - 1的传播延迟如图24所示。上升时间tRise定义为输出从输入高逻辑阈值VIH上升到10%阈值的时间。同样,下降时间tFall定义为输出从输入下降逻辑低电压阈值VIL下降到90%阈值的时间。上升和下降时间取决于负载条件,且通常不包含在传播延迟中,因为它们并非栅极驱动器的标准特性。

通道间匹配是指单个ADuM4121/ADuM4121 - 1器件内各通道之间传播延迟的最大差异量。

传播延迟偏差是指在相同条件下工作的多个ADuM4121/ADuM4121 - 1器件之间传播延迟的最大差异量。

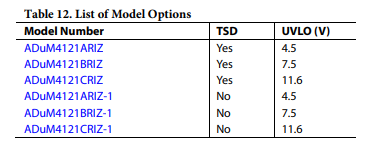

欠压锁定(UVLO)

ADuM4121/ADuM4121 - 1对器件的初级侧和次级侧均设有欠压锁定保护。如果初级侧或次级侧电压低于欠压锁定下降沿阈值,器件输出将为低电平信号。在ADuM4121/ADuM4121 - 1上电后,上升沿欠压锁定阈值使器件能够输出找到输入信号。该器件内置迟滞特性,可抵御小电压源纹波。初级侧欠压锁定阈值在所有型号中通用。次级输出欠压锁定阈值有三种选项,列于表12中。

-

探秘ADuM4121:高性能隔离栅极驱动器的卓越之选2026-02-04 556

-

ADUM4135单电源/双电源高电压隔离IGBT栅极驱动器技术手册2025-06-04 1690

-

ADuM4120/ADuM4120-1具有2A输出的隔离式精密栅极驱动器技术手册2025-06-03 1450

-

ADUM4121的左右供电分别是VDD1、DGND和VDD2、PGND,如果DGND和PGND通过零欧电阻单点连接会有什么影响吗?2024-01-11 728

-

高压隔离栅极驱动器ADuM4121/ADuM4121-1数据手册2023-11-28 629

-

EVAL-ADuM4121 EVAL-ADuM4121评估板2021-08-18 159

-

ADuM4121ADuM4121-1 IBIS型号2021-05-29 846

-

UG-1041:ADuM4121和ADuM4121-1评估板<span class=“模拟耦合器”>I</span>耦合器,高压,隔离栅驱动器,带内密勒钳位,2 A输出2021-05-16 857

-

ADuM4221/ADuM4221-1/ADuM4221-2:隔离式半桥栅极驱动器,死区时间可调,4 A输出数据表2021-03-22 1283

-

ADuM4135:提供米勒箝位的单电源 / 双电源 高电压隔离 IGBT 栅极驱动器2021-03-21 1029

-

ADuM4121/ADuM4121-1 IBIS Model2021-02-21 871

-

ADUM4121-1 集成内部米勒箝位的高压、隔离式栅极驱动器,2 A输出2019-02-22 577

-

ADuM4121/ADuM4121-1评估板介绍2018-10-29 1732

全部0条评论

快来发表一下你的评论吧 !